來源:《半導體芯科技》雜志 10/11月刊

作者:Gayle Murdoch, imec技術團隊主要成員;Zsolt Tokei, imec FELLOW兼納米互連項目總監

半鑲嵌集成是一種將互連工藝流程擴展至用于低于20nm金屬間距的方法,該方法富有吸引力且具成本效益。IMEC是在五年前提出這種方法的,現今確認:已對一款18nm金屬間距的功能性雙金屬級半鑲嵌模塊進行了首次實驗演示。

半鑲嵌集成和BEOL發展路線圖

20多年來,銅(Cu)雙鑲嵌(dual-damascene)一直是構建可靠互連的主要工藝流程。但是,當尺寸繼續縮小,并且金屬間距(metal pitches)變得像20nm及以下那樣緊密時,由于電阻電容(RC)乘積的急劇增長,后段制程(BEOL)越來越受到RC延遲的不利影響。這個問題迫使互連行業著手尋找替代集成方案,以及在緊密金屬間距下具有更好品質因數的金屬。

在本文中,imec的研究人員Gayle Murdoch和Zsolt Tokei著重闡述了緊密金屬間距下通孔自對準的重要性,解釋并演示了模塊的主要技術參數,包括通孔和線路電阻以及可靠性。該研究結果在2022年IEEE VLSI技術與電路研討會(VLSI 2022)上發表。

△圖1:imec的半鑲嵌流程:a)Ru蝕刻(底部局部互連線(Mx)的形成);b)間隙填充;c)通孔蝕刻;d)通孔填充和頂線(Mx+1)形成(在VLSI2022大會上展示)。

大約五年前,imec最初提出半鑲嵌(semi-damascene)作為銅雙鑲嵌的可行替代方案,用于集成1nm(及以下)技術節點的最關鍵的局部(Mx)互連層。

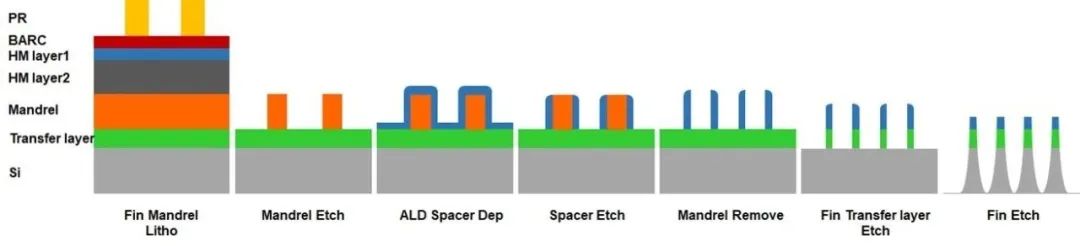

與雙鑲嵌不同,半鑲嵌集成依賴于互連金屬的直接圖案化來制作線條(稱為減材金屬化-subtractive metallization)。不需要采用金屬的化學機械拋光(CMP)來完成工藝流程。

連接后續互連層的通孔以單鑲嵌方式圖案化,然后用金屬填充和過度填充,這意味著金屬沉積會繼續進行,直到在電介質上形成一層金屬。接著,對該金屬層進行掩膜和蝕刻,以形成具有正交線的第二互連層。

在金屬圖案化之后,線之間的間隙可以用電介質填充,或用于在局部層處形成(部分)氣隙。請注意,在半鑲嵌流程中,一次性形成兩層(通孔和頂部金屬),就像傳統的雙鑲嵌一樣。當以雙鑲嵌為基準進行評估時,這使其具備很好的成本競爭力(見圖2)。

△圖2:18nm金屬間距下半鑲嵌與雙鑲嵌成本的比較。

半鑲嵌集成流程的好處

據imec Fellow兼納米互連項目總監Zsolt Tokei稱,與銅雙鑲嵌相比,半鑲嵌在緊密的金屬間距下具有多項優勢。他表示:“首先,它允許更高的線路縱橫比,同時保持電容處于受控狀態,這有望帶來整體RC優勢。其次,由于沒有金屬CMP工藝步驟,因而造就出更簡化和成本效益更高的集成方案。最后,半鑲嵌集成需要一種無阻擋層(barrierless)、可圖案化的金屬,例如鎢(W)、鉬(Mo)或釕(Ru)。通過使用不需要金屬阻擋層的金屬(這不同于銅),珍貴的導電區域就可以被互連金屬本身充分利用,從而確保在微縮尺寸上具有競爭力的通孔電阻。”

△圖3:沿Mx(左)和跨Mx(右)的自對準通孔。X-TEM顯示自對準通孔落在18nm間距Ru線上(在VLSI 2022大會上演示)。

當然,除了上述好處之外,在這樣的一項計劃獲得業界認可之前,還有許多挑戰需要解決。朝這個方向邁出的一步是實際演示了雙金屬級方案。雖然迄今僅通過仿真和建模顯示了這些好處,但是imec首次為雙金屬級半鑲嵌模塊提供了實驗證據。

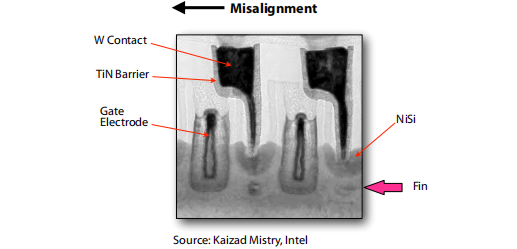

完全自對準的通孔:一個至關重要的構建塊

在金屬間距小至20nm的情況下,控制通孔降落在窄線上是半鑲嵌集成模塊成功運行的關鍵。當通孔和線路(在通孔頂部和底部)沒有正確對齊時,通孔和相鄰線路之間存在泄漏的風險。這些泄漏路徑是由小通孔的常規圖案化引起的過大覆蓋誤差造成的。

imec技術團隊主要成員Gayle Murdoch說:“找到一種方法來制作功能性、完全自對準的通孔一直是半鑲嵌工藝的‘圣杯’。我們通過imec的集成、光刻、蝕刻和清洗團隊之間的密切合作實現了這一里程碑。憑借我們完全自對準的集成方案,我們能夠補償高達5nm的覆蓋誤差,這是一項重要的成就。”

通過在間隙填充后選擇性去除氮化硅來確保底部自對準,從而允許在下部金屬線的范圍內形成通孔。朝向頂部金屬層(Ru)的自對準是通過Ru過度蝕刻步驟實現的,該步驟在通孔過度填充和Ru圖案化之后應用。

△圖4:Ru線和Cu線的導電面積與線電阻的關系(在VLSI 2022大會上演示)。

新的里程碑:18nm間距下的良好電阻和可靠性

使用具有完全自對準通孔的Ru減法蝕刻(subtractive etch)產生了18nm金屬間距的功能性雙金屬級器件。結合自對準雙重圖案化(SADP)的EUV光刻用于對9nm“寬”的Ru底部局部互連線(Mx)進行圖案化,而單次曝光EUV光刻則用于印刷頂線(Mx+1)和通孔。頂部金屬與氣隙相組合以抵消電容的增加。

當將Ru與Cu的線路電阻與導電面積進行基準比較時,在目標金屬間距下,Ru明顯優于Cu。通孔自對準在形態學和電學上都得到了確證。實現了優異的通孔電阻(對于26~18nm的金屬間距,其阻值范圍在40Ω和60Ω之間),并且證實通孔到線擊穿電場>9MV/cm。

Zsolt Tokei說道:“我們展示了所有關鍵技術參數的卓越價值,包括通孔和線路電阻及可靠性。該演示表明,半鑲嵌是雙鑲嵌的一種有價值的替代方案,用于集成1nm技術節點及以后的前三個局部互連層。我們的具有完全自對準通孔的雙金屬級器件已被證明是關鍵的構建塊。”

研究人員表示,通過增加線路的縱橫比(這可以降低電阻),同時保持氣隙(這可以控制電容),可以實現進一步的改進。與此同時,對使用半鑲嵌技術(它允許在標準單元級別進一步減小面積)實現中段制程(MOL)和BEOL技術下一步改進,imec也已經有了具體的想法。

參考文獻

Gayle Murdoch于1997年畢業于愛丁堡大學,獲化學物理學榮譽學士學位。她的職業生涯先是在NECSemiconductors公司擔任光刻工程師,后來加入Filtronic Compound Semiconductors公司,從事GaAs器件的蝕刻開發和集成工作,并最終成為首席蝕刻工程師。2008年,她加入了imec的先進光刻技術團隊,然后在2013年轉到BEOL集成部門。她從事過一系列課題的研發,包括低k電介質集成,完全自對準通孔,以及最近的半鑲嵌集成。目前,她是技術團隊的主要成員職位,并領導BEOL集成團隊。

Zsolt Tokei是imec Fellow兼納米互連項目總監。他于1999年加入imec,先是作為低k銅互連領域的一名工藝工程師和研究人員,接下來擔任了金屬部門的主管。之后,他成為了納米互連項目的首席科學家和總監。他1994年在匈牙利德布勒森的科蘇特(Kossuth)大學獲得物理學碩士學位。1997年在匈牙利科蘇特大學和法國艾克斯-馬賽第三大學(Aix Marseille-III)大學共同指導的論文框架內,他獲得了物理學和材料科學的博士學位。1998年,作為博士后研究員,他開始在德國杜塞爾多夫的馬克斯-普朗克研究所工作。加入imec后,他繼續從事一系列互連問題的研究,包括微縮、金屬化、電氣特性分析、模塊集成、可靠性和系統等方面。

審核編輯 黃昊宇

-

模塊

+關注

關注

7文章

2837瀏覽量

53300 -

IMEC

+關注

關注

0文章

60瀏覽量

22847

發布評論請先 登錄

CPO模塊電光同步貼裝新方案——京瓷高精度無源對準技術解析

Salicide自對準硅化物工藝的定義和制造流程

溫控雙金屬片VS 熱敏電阻NTC

愛立信攜手DNB斬獲全球首個自智網絡L4級認證

南非MTN攜手華為獲頒自智網絡L4級認證證書

電能質量在線監測裝置模塊故障會自診斷嗎?

基本半導體1200V工業級碳化硅MOSFET半橋模塊Pcore 2系列介紹

芯片制造中的對準技術詳解

100%開源!行業首個企業級智能體

下一代高速芯片晶體管解制造問題解決了!

自對準硅化物工藝詳解

自對準雙重圖案化技術的優勢與步驟

IBC技術新突破:基于物理氣相沉積(PVD)的自對準背接觸SABC太陽能電池開發

IMEC制造首個完全自對準的雙金屬級半鑲嵌模塊

IMEC制造首個完全自對準的雙金屬級半鑲嵌模塊

評論