隨著AI、云計算爆發(fā)式增長,數(shù)據(jù)中心面臨帶寬密度不足與功耗激增雙重挑戰(zhàn)。傳統(tǒng)電互連和板級光模塊難以滿足需求,而共封裝光學(xué)(CPO)技術(shù)將光電器件緊貼CPU/GPU封裝,縮短電傳輸距離,實現(xiàn)能效提升40%+與帶寬密度翻倍。本文介紹京瓷提出的一種無源對準方法,該方法利用CNC補償技術(shù),實現(xiàn)了CPO(共封裝光學(xué))模塊的電光同步貼裝。該方法能夠?qū)?a href="http://www.3532n.com/v/tag/2800/" target="_blank">光電轉(zhuǎn)換器精確地貼裝到聚合物波導(dǎo)上,并提供了足以支持32 Gb/s NRZ(非歸零碼)傳輸的耦合效率。

CPO模塊結(jié)構(gòu)設(shè)計

圖1:CPO模塊結(jié)構(gòu)(a)與光耦合截面示意圖(b)

京瓷CPO模塊的主要設(shè)計包括:

雙芯片設(shè)計:2個5×5mm硅光(SiPh)芯片,集成4通道收發(fā)器,采用硅光技術(shù)實現(xiàn)光電轉(zhuǎn)換;

基板尺寸:33.6×21.0mm2,嵌入聚合物波導(dǎo)+曲面反射鏡;

光路路徑:SiPh芯片 → 垂直光釘 → 45°曲面鏡 → 波導(dǎo) → 多模光纖;

創(chuàng)新光路設(shè)計:采用聚合物垂直光釘(Optical Pins)將光信號引出芯片平面。

貼片容差:±5μm的生死線

光耦合損耗必須≤0.6 dB才能滿足32 Gb/s NRZ傳輸。通過微位移實驗(圖2)測得X/Y軸偏移容忍度僅±5μm,超過±5μm損耗劇增。此外,采用曲面鏡設(shè)計使X/Y軸容差對稱化,避免焦點突變。

圖2:容差測試裝置

圖3:X/Y軸位移與光損耗關(guān)系

貼片流程:SIEOM技術(shù)突破工藝瓶頸

圖4:SIEOM工藝流程

傳統(tǒng)工藝面臨有機基板形變大、微鏡面難做標記,以及光釘位置波動等難題。京瓷采用了SIEOM創(chuàng)新流程(圖4),具體如下:

光刻核心標記:波導(dǎo)加工時同步制作定位標記(Core-Marks);

CNC視覺補償:測量基板標記/鏡面坐標,計算最佳貼裝位;

光釘主動對齊:通用貼片機以光釘為基準定位(非傳統(tǒng)設(shè)備標記);

樹脂填充:折射率匹配膠同時充當?shù)撞刻畛淞稀?/span>

一舉三得:單次貼裝同步完成100個BGA焊點+8個光通道(4Tx+4Rx)

結(jié)果分析:精度與損耗雙達標

驗證方法:采用IR顯微鏡無損檢測光釘位置(圖5驗證準確性),并對比設(shè)計位置與實際偏移量的光損耗。

圖5:光釘-波導(dǎo)耦合截面(實際貼合狀態(tài))

結(jié)果表明,如圖6所示,最佳位光耦合損耗僅0.3 dB(遠低于0.6dB上限)。SIEOM將位置偏差控制在±5μm內(nèi),傳統(tǒng)方法波動達±15μm成功支持32 Gb/s NRZ傳輸(BER<10?12)。

圖6:Y軸偏移與損耗關(guān)系(實點:SIEOM實測;虛線:容差曲線)

圖7:SIEOM vs 傳統(tǒng)方法精度對比(誤差棒=極值)

結(jié)論:為CPO量產(chǎn)鋪平道路

京瓷開發(fā)的SIEOM技術(shù)實現(xiàn)了電光同步無源貼裝。通過光刻標記+CNC補償攻克±5μm對準難題,其光損耗0.3dB滿足32Gb/s高速傳輸。該項技術(shù)為CPO標準化量產(chǎn)提供高性價比方案。

-

光電器件

+關(guān)注

關(guān)注

1文章

191瀏覽量

19682 -

CPO

+關(guān)注

關(guān)注

0文章

47瀏覽量

716

發(fā)布評論請先 登錄

應(yīng)用于CPO封裝模塊內(nèi)的光纖互聯(lián)方案

無線溫度采集新方案

三項電機驅(qū)動新方案

貼裝技術(shù)的特點

貼裝重復(fù)精度簡述

求一種基于GAP技術(shù)的網(wǎng)絡(luò)保護設(shè)備設(shè)計新方案

介紹一種車載GPS系統(tǒng)GPRS的新方案

STM32構(gòu)建數(shù)字電源新方案

基于RSA的廣播加密新方案

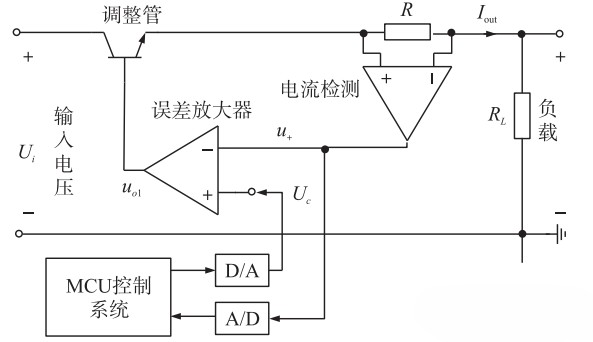

高精度電流源如何設(shè)計出來

CPO模塊電光同步貼裝新方案——京瓷高精度無源對準技術(shù)解析

CPO模塊電光同步貼裝新方案——京瓷高精度無源對準技術(shù)解析

評論