當(dāng)今的嵌入式系統(tǒng)設(shè)計(jì)人員有各種各樣的處理器類型可供選擇,與更熟悉的CPU(中央處理器)相比,FPGA(現(xiàn)場可編程門陣列)和GPU(圖形處理單元)增加了自己的各種優(yōu)點(diǎn)和缺點(diǎn)。了解這些特性以及 FPGA 和 GPU 如何堆疊可以幫助系統(tǒng)集成商在選擇和安裝處理器時(shí)做出正確的選擇,既可以單獨(dú)使用,也可以與其他類型的處理器結(jié)合使用。

當(dāng)今的嵌入式系統(tǒng)設(shè)計(jì)人員有各種各樣的處理器類型可供選擇,與更熟悉的CPU(中央處理器)相比,F(xiàn)PGA(現(xiàn)場可編程門陣列)和GPU(圖形處理單元)增加了自己的各種優(yōu)點(diǎn)和缺點(diǎn)。了解這些特性以及 FPGA 和 GPU 如何堆疊可以幫助系統(tǒng)集成商在選擇和安裝處理器時(shí)做出正確的選擇,既可以單獨(dú)使用,也可以與其他類型的處理器結(jié)合使用。

FPGA 是算法的硬件實(shí)現(xiàn),由于硬件實(shí)現(xiàn)通常比軟件實(shí)現(xiàn)運(yùn)行得更快,因此它們的性能非常好。與 FPGA 不同,GPU 執(zhí)行軟件;與 FPGA 的硬件實(shí)現(xiàn)相比,執(zhí)行復(fù)雜算法需要許多順序 GPU 指令。GPU 的優(yōu)點(diǎn)是其高內(nèi)核數(shù),這使得某些并行算法的運(yùn)行速度比 CPU 快得多,尤其是那些使用浮點(diǎn)計(jì)算的算法。1,000 核 GPU 每個(gè)時(shí)鐘周期可以運(yùn)行 1,000 次浮點(diǎn)計(jì)算。對(duì)于信號(hào)和圖像處理應(yīng)用,GPU 是自然而然的選擇。對(duì)于高度并行的數(shù)學(xué)密集型應(yīng)用,GPU 性能通常優(yōu)于 CPU,并且在每瓦性能方面接近與 FPGA 相當(dāng)。

從歷史上看,F(xiàn)PGA 的一個(gè)缺點(diǎn)是,與 CPU 和 GPU 相比,它們更難編程。CPU軟件通常使用許多現(xiàn)成的編程語言之一進(jìn)行編程,例如Java,C或Python。FPGA 使用硬件描述語言 (HDL) (如 Verilog)或超高速集成電路硬件描述語言 (VHDL) 進(jìn)行編程,后者直接轉(zhuǎn)換為 FPGA 邏輯單元。GPU 通常使用軟件框架進(jìn)行編程,使用戶不必專門為 GPU 編寫代碼;相反,代碼是在高級(jí)別編寫的。FPGA也是如此:軟件開發(fā)框架正在被設(shè)計(jì)為無需HDL(硬件描述語言)即可實(shí)現(xiàn)FPGA編程。FPGA 供應(yīng)商已經(jīng)提供了框架,并在其開發(fā)環(huán)境中構(gòu)建了工具包,從而消除了對(duì)直接 HDL 編程的需求。

異構(gòu)性/結(jié)構(gòu)連接

嵌入式應(yīng)用通常需要結(jié)合 CPU、FPGA 和 GPU 元素的異構(gòu)系統(tǒng)架構(gòu)。雖然傳統(tǒng)的嵌入式應(yīng)用可能包括單個(gè) CPU 和 GPU 處理元件,但一些處理器密集型平臺(tái)集成了多個(gè) CPU、GPU 和 FPGA 引擎,這些引擎在通過高速 PCI Express (PCIe) 或以太網(wǎng)結(jié)構(gòu)背板連接的單個(gè)或多個(gè)獨(dú)立卡上實(shí)現(xiàn),以并行通信和執(zhí)行任務(wù)。或者,NVIDIA提供的一些最新的獨(dú)立GPU加速模塊(即Jetson AGX Xavier)在單個(gè)系統(tǒng)模塊(SoM)上集成了六個(gè)不同的計(jì)算引擎,其中包括CPU,GPU,深度學(xué)習(xí)加速器,視覺加速器,多媒體引擎等。基于這項(xiàng)技術(shù)的堅(jiān)固耐用的商用現(xiàn)貨(COTS)系統(tǒng)的一個(gè)例子是Curtiss-Wright的Parvus DuraCOR AGX Xavier小型模塊化任務(wù)計(jì)算機(jī),它集成了Jetson AGX Xavier的NVIDIA CUDA核心加速圖形處理,人工智能/深度學(xué)習(xí)推理和邊緣計(jì)算功能。(見上文,圖 1。

FPGA 的一個(gè)重要特性是其任意 I/O 連接,使其能夠在沒有主機(jī) CPU 的情況下連接到傳感器、網(wǎng)絡(luò)或存儲(chǔ)設(shè)備。例如,高端雷達(dá)系統(tǒng)可能需要許多離散處理元件和計(jì)算階段來支持多個(gè)高速數(shù)據(jù)輸入;在這種情況下,F(xiàn)PGA具有一些優(yōu)勢,因?yàn)樗鼈兛梢灾苯舆B接到這些高速傳感器并提供非常高的帶寬。

延遲和確定性

隨著總線速度的提高,預(yù)計(jì)較新的 CPU 和 GPU 的延遲會(huì)降低;但是,F(xiàn)PGA 的延遲更具確定性。對(duì)于FPGA,延遲約為1μs是可行的,而CPU延遲往往在50μs左右。

在系統(tǒng)而不是傳統(tǒng)操作系統(tǒng)上使用實(shí)時(shí)操作系統(tǒng) (RTOS) 可能有助于確定性,但不一定提供更好的延遲。換句話說,使用 RTOS 可以更好地了解處理器的執(zhí)行速度,但不一定會(huì)導(dǎo)致更快的執(zhí)行速度。

在為特定應(yīng)用選擇特定處理器時(shí),許多變量都在起作用。在任何新設(shè)計(jì)計(jì)劃開始時(shí),咨詢您信任的供應(yīng)商的系統(tǒng)架構(gòu)師會(huì)很有幫助,他們會(huì)解決這些問題并每天做出這些類型的決策。正確的選擇可以改變一切。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

20250瀏覽量

252208 -

FPGA

+關(guān)注

關(guān)注

1660文章

22408瀏覽量

636222 -

gpu

+關(guān)注

關(guān)注

28文章

5194瀏覽量

135427

發(fā)布評(píng)論請(qǐng)先 登錄

思必馳亮相ISE 2026歐洲視聽技術(shù)及系統(tǒng)集成展覽會(huì)

研華科技TwinBuilder實(shí)現(xiàn)光儲(chǔ)充智能運(yùn)維解決方案

天合儲(chǔ)能榮登標(biāo)普全球能源2025電池儲(chǔ)能系統(tǒng)集成商TOP10榜單

HiL測試系統(tǒng)電氣設(shè)計(jì)與集成服務(wù)

達(dá)實(shí)榮獲2025中國安博會(huì)“卓越集成商獎(jiǎng)”

慧視光電——全棧圖像處理板供應(yīng)商

昂瑞微電子祝賀翌虹成為Google Find Hub系統(tǒng)集成服務(wù)商

天合儲(chǔ)能入選2025上半年全球儲(chǔ)能系統(tǒng)出貨量TOP10榜單

EtherCAT轉(zhuǎn)Profinet網(wǎng)關(guān)與匯川伺服系統(tǒng)集成及輪廓模式應(yīng)用解析

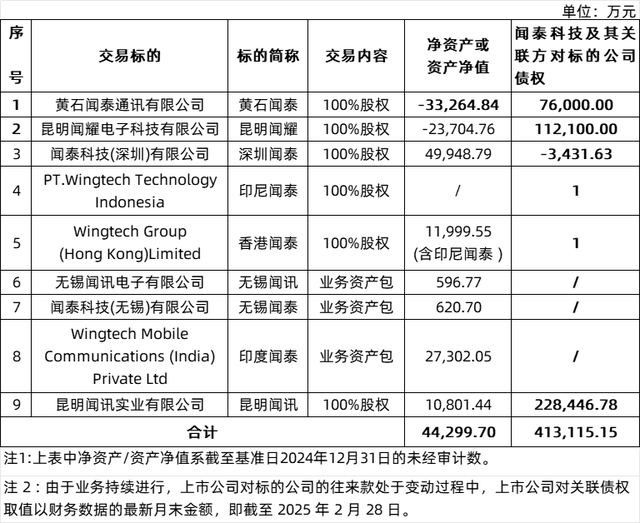

立訊精密收購聞泰子公司,拓展系統(tǒng)集成業(yè)務(wù)

無感考勤如何做到“無懈可擊”?

迎接工業(yè)革命浪潮:重塑傳統(tǒng)系統(tǒng),迎接未來機(jī)遇

探秘地下變電站:智能輔助控制系統(tǒng)業(yè)務(wù)智能處理與系統(tǒng)集成

FPGA和GPU的特點(diǎn)及如何堆疊幫助系統(tǒng)集成商

FPGA和GPU的特點(diǎn)及如何堆疊幫助系統(tǒng)集成商

評(píng)論