電子發燒友網報道(文/周凱揚)臺積電作為目前全球最大的晶圓廠,擁有龐大的客戶基數,為了打造出了一個屬于自己的設計生態系統,臺積電也成立了一個“開放創新平臺”,將廣大EDA/IP、設計中心、云服務廠商納入其中。而作為EDA廠商來說,除了要和IC設計公司打好關系以外,同樣要與晶圓廠建立深入合作,這樣才能拿到最新的工藝庫、PDK。

截至2022年7月1日,臺積電“開放創新平臺”中的電子設計自動化(EDA)聯盟已經有了16家EDA公司的加入,包括Ansys、Cadence、新思、西門子EDA和華大九天等廠商。然而,對于最新的工藝和堆疊封裝技術來說,臺積電對于EDA工具的認證卻僅限于四大頭部EDA廠商,今年10月底,這些廠商也紛紛發布了自己獲得認證的消息。

EDA大廠陸續獲得認證

今年10月25日,Cadence宣布自己的數字和定制/模擬設計流程獲得了臺積電N4P和N3E工藝的認證,支持最新的設計規則手冊和在N3工藝用到的FINFLEX技術。Cadence設計流程也為N4P和N3E的PDK進行了加強,為工程師提供更簡單的模擬設計遷移、優化的PPA和更快的上市時間。以數字設計全流程為例,Cadence為臺積電的N4P和N3E工藝提供了從綜合到簽核ECO的原生混合高度單元行優化,實現了更好的PPA。

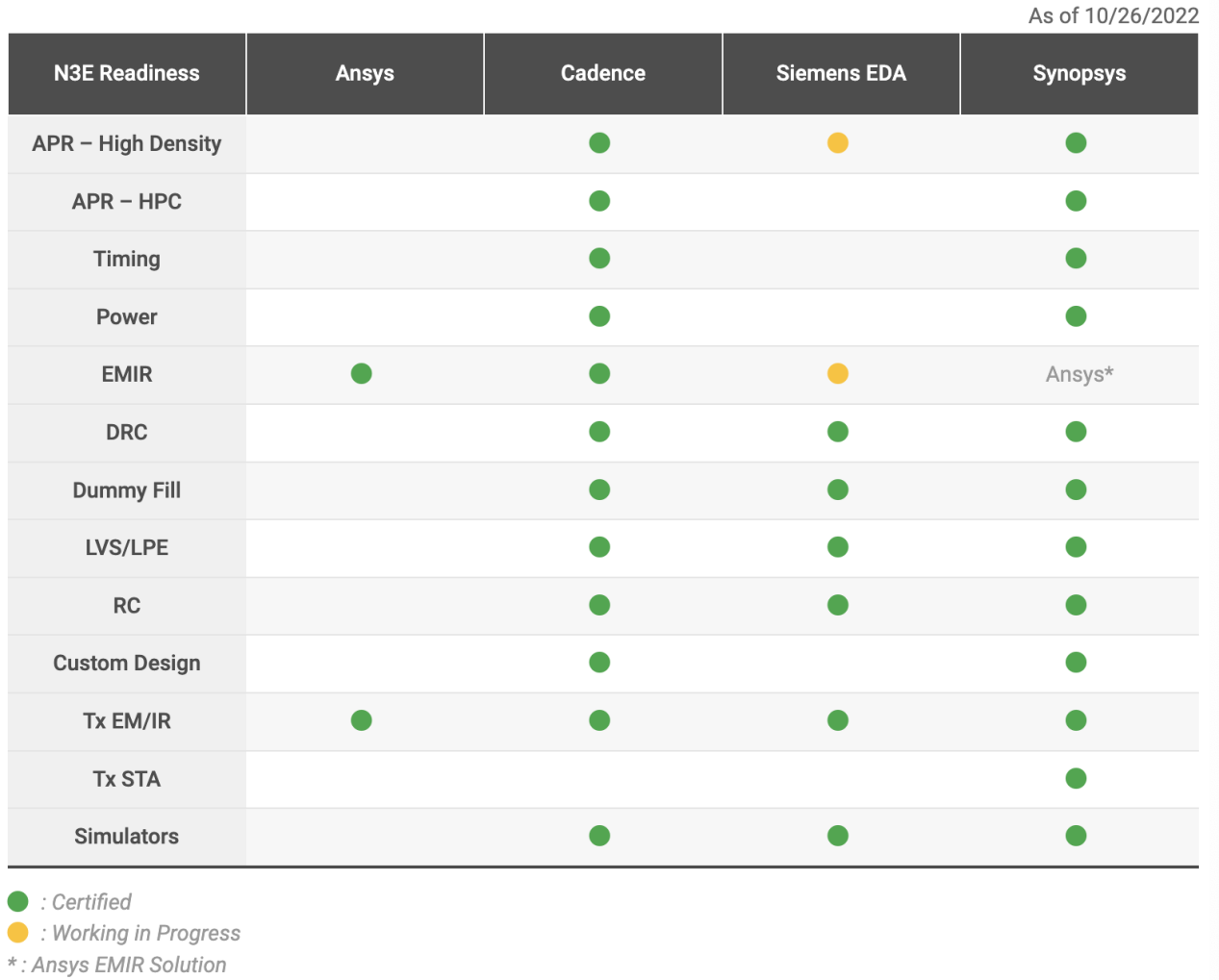

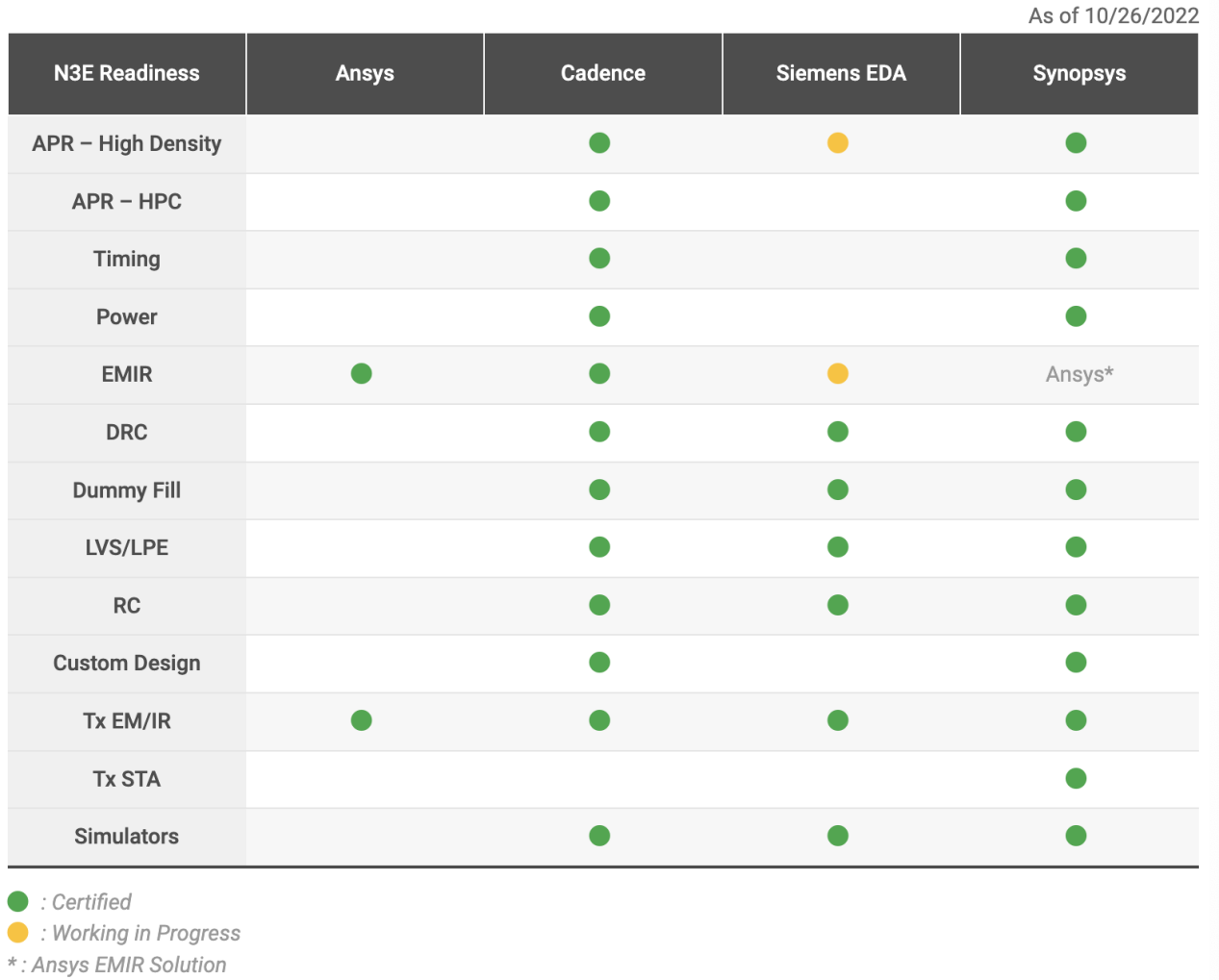

N3E工藝節點EDA工具認證情況 / 臺積電

新思的數字和定制設計流程同樣獲得了臺積電N4P和N3E的EDA工具認證,并聲稱其接口IP產品已經在N3E工藝節點上實現了多次成功流片。而且新思的AI設計工具,DSO.ai和Fusion Compiler,同樣打造出了多個經驗證的N3E測試案例,實現了更好的PPA和更快的設計周期。顯而易見,作為一家逐漸將IP業務壯大起來的EDA公司,新思很好地將這兩大業務打入了臺積電的設計生態中。

西門子EDA的物理驗證平臺Calibre、模擬/混合信號電路驗證平臺Analog FastSPICE也都獲得了臺積電N4P和N3E工藝的認證。不過在N3E這個工藝節點上,西門子EDA目前針對高密度單元庫的APR解決方案和EM/IR分析方案仍在認證過程中,不過從N4P這一節點的情況來看,獲得認證也只是時間問題。

不只是最新工藝

獲得了針對臺積電N3E和N4P的認證后,自然是為兩大工藝在移動設備、HPC、定制設計和模擬設計遷移上提供了完備的EDA方案,但同樣不可忽視的還有堆疊封裝技術以及特種工藝,比如3DFabric、不同節點的毫米波和sub-6G射頻工藝等等。

要想實現2.5D/3D的芯片設計,尤其需要與EDA/IP廠商的深度聯合,這樣才能加快封裝/芯片的聯合設計,解決散熱、串行/并行IO、ESD等設計痛點。所以臺積電在今年的技術論壇上提出了3Dblox的概念,用于解決復雜系統前端設計中的分區問題,比如先分成bump、via、cap和die等模組,再根據所選的臺積電3D封裝方案(CoWoS、InFO、SoIC)開展模組化的設計流程。

從目前的認證情況上來看,Ansys、Cadence、西門子EDA和新思都已經獲得了3Dblox這一設計方案的認證,然而在一些驗證、分析環節,這幾家獲得的工具認證情況有些差異。比如雖然Cadence、西門子EDA和新思都已經獲得了物理驗證方案的認證,但在電氣驗證上只有Cadence和新思兩家獲得了完備的認證,而且新思在EM/IR分析上用到了Ansys的方案。

再者就是臺積電16nm FFC工藝的毫米波射頻認證,這一工藝代表了支持毫米波5G的RFIC和5G SoC的下一代方案。幾家EDA廠商中,新思、Ansys和是德科技的毫米波射頻設計流程獲得了臺積電的16FFC認證,Cadence的RFIC設計解決方案也獲得了該認證。

寫在最后

從臺積電的EDA工具認證來看,國內EDA廠商在打入臺積電設計生態上還有很長的路要走,數字/模擬設計全流程和晶圓廠的深入合作要兩手抓。畢竟Ansys走的也并非全流程路線,卻依然在不少環節獲得了臺積電的EDA工具認證,而全流程認證走得最遠的依然是Cadence和新思兩家廠商。

截至2022年7月1日,臺積電“開放創新平臺”中的電子設計自動化(EDA)聯盟已經有了16家EDA公司的加入,包括Ansys、Cadence、新思、西門子EDA和華大九天等廠商。然而,對于最新的工藝和堆疊封裝技術來說,臺積電對于EDA工具的認證卻僅限于四大頭部EDA廠商,今年10月底,這些廠商也紛紛發布了自己獲得認證的消息。

EDA大廠陸續獲得認證

今年10月25日,Cadence宣布自己的數字和定制/模擬設計流程獲得了臺積電N4P和N3E工藝的認證,支持最新的設計規則手冊和在N3工藝用到的FINFLEX技術。Cadence設計流程也為N4P和N3E的PDK進行了加強,為工程師提供更簡單的模擬設計遷移、優化的PPA和更快的上市時間。以數字設計全流程為例,Cadence為臺積電的N4P和N3E工藝提供了從綜合到簽核ECO的原生混合高度單元行優化,實現了更好的PPA。

N3E工藝節點EDA工具認證情況 / 臺積電

新思的數字和定制設計流程同樣獲得了臺積電N4P和N3E的EDA工具認證,并聲稱其接口IP產品已經在N3E工藝節點上實現了多次成功流片。而且新思的AI設計工具,DSO.ai和Fusion Compiler,同樣打造出了多個經驗證的N3E測試案例,實現了更好的PPA和更快的設計周期。顯而易見,作為一家逐漸將IP業務壯大起來的EDA公司,新思很好地將這兩大業務打入了臺積電的設計生態中。

西門子EDA的物理驗證平臺Calibre、模擬/混合信號電路驗證平臺Analog FastSPICE也都獲得了臺積電N4P和N3E工藝的認證。不過在N3E這個工藝節點上,西門子EDA目前針對高密度單元庫的APR解決方案和EM/IR分析方案仍在認證過程中,不過從N4P這一節點的情況來看,獲得認證也只是時間問題。

不只是最新工藝

獲得了針對臺積電N3E和N4P的認證后,自然是為兩大工藝在移動設備、HPC、定制設計和模擬設計遷移上提供了完備的EDA方案,但同樣不可忽視的還有堆疊封裝技術以及特種工藝,比如3DFabric、不同節點的毫米波和sub-6G射頻工藝等等。

要想實現2.5D/3D的芯片設計,尤其需要與EDA/IP廠商的深度聯合,這樣才能加快封裝/芯片的聯合設計,解決散熱、串行/并行IO、ESD等設計痛點。所以臺積電在今年的技術論壇上提出了3Dblox的概念,用于解決復雜系統前端設計中的分區問題,比如先分成bump、via、cap和die等模組,再根據所選的臺積電3D封裝方案(CoWoS、InFO、SoIC)開展模組化的設計流程。

從目前的認證情況上來看,Ansys、Cadence、西門子EDA和新思都已經獲得了3Dblox這一設計方案的認證,然而在一些驗證、分析環節,這幾家獲得的工具認證情況有些差異。比如雖然Cadence、西門子EDA和新思都已經獲得了物理驗證方案的認證,但在電氣驗證上只有Cadence和新思兩家獲得了完備的認證,而且新思在EM/IR分析上用到了Ansys的方案。

再者就是臺積電16nm FFC工藝的毫米波射頻認證,這一工藝代表了支持毫米波5G的RFIC和5G SoC的下一代方案。幾家EDA廠商中,新思、Ansys和是德科技的毫米波射頻設計流程獲得了臺積電的16FFC認證,Cadence的RFIC設計解決方案也獲得了該認證。

寫在最后

從臺積電的EDA工具認證來看,國內EDA廠商在打入臺積電設計生態上還有很長的路要走,數字/模擬設計全流程和晶圓廠的深入合作要兩手抓。畢竟Ansys走的也并非全流程路線,卻依然在不少環節獲得了臺積電的EDA工具認證,而全流程認證走得最遠的依然是Cadence和新思兩家廠商。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

臺積電

+關注

關注

44文章

5803瀏覽量

176296 -

eda

+關注

關注

72文章

3113瀏覽量

182890

發布評論請先 登錄

相關推薦

熱點推薦

臺積電擬投資170億,在日本建設3nm芯片工廠

據報道,全球最大的半導體代工制造商臺積電(TSMC)已最終確定在日本熊本縣量產3nm線寬的尖端半導體芯片的計劃。預計該項目投資額將達到170億美元。日本政府正致力于提升國內半導體制造能

1.4nm制程工藝!臺積電公布量產時間表

電子發燒友網綜合報道 近日,全球半導體代工龍頭臺積電在先進制程領域持續展現強勁發展勢頭。據行業信源確認,臺積

臺積電2納米制程試產成功,AI、5G、汽車芯片

又近了一大步。 ? ? 這一歷史性節點不僅意味著制程技術的再度跨越,也預示著未來AI、通信與汽車等核心領域即將迎來一場深刻的“芯革命”。 1、技術再突破 與現行的3nm工藝相比,臺積電

臺積電預計對3nm漲價!軟銀豪擲54億美元收購ABB機器人部門/科技新聞點評

在十一黃金周和國慶假期后第一天工作日,科技圈接連發生三件大事:1、臺積電預計將對3nm實施漲價策略;2、日本巨頭軟銀宣布54億美元收購ABB機器人部門;

突發!臺積電南京廠的芯片設備出口管制豁免被美國正式撤銷

美國已撤銷臺積電(TSMC)向其位于中國大陸的主要芯片制造基地自由運送關鍵設備的授權,這可能會削弱其老一代晶圓代工廠的生產能力。 美國官員最近通知臺

今日看點:傳臺積電先進2nm芯片生產停用中國大陸設備;保時捷裁員約200人

傳臺積電先進2nm芯片生產停用中國大陸設備 ? 業內媒體報道,根據多位知情人士透露,臺

發表于 08-26 10:00

?2644次閱讀

重新定義基礎款,eSUN Basic 系列產品已陸續上線!

eSUN易生PLA基礎(PLA-Basic)、PETG基礎(PETG-Basic)等基礎(Basic)系列產品已陸續上線,它們的主要特點在于出色的性價比,在保持價格優勢的同時,也為用戶提供較好的打印使用體驗。

長電科技先進封裝技術助力智能眼鏡功能升級

2025年以來,眾多廠商陸續推出智能眼鏡產品,“百鏡大戰”一觸即發,市場或將迎來爆發元年。根據國際數據公司(IDC)的預測,2025年全球智能眼鏡市場出貨量將達到1280萬臺,同比增長26%。輕量化設計、AI大模型融合與現實多場

臺積電先進制程漲價,最高或達30%!

%,最高可能提高30%。 ? 今年1月初臺積電也傳出過漲價消息,將針對3nm、5nm等先進制程技術進行價格調整,漲幅預計在

發表于 05-22 01:09

?1256次閱讀

西門子與臺積電合作推動半導體設計與集成創新 包括臺積電N3P N3C A14技術

西門子和臺積電在現有 N3P 設計解決方案的基礎上,進一步推進針對臺積電 N

發表于 05-07 11:37

?1523次閱讀

臺積電2nm制程良率已超60%

,較三個月前技術驗證階段實現顯著提升(此前驗證階段的良率已經可以到60%),預計年內即可達成量產準備。 值得關注的是,蘋果作為臺積電戰略合作伙伴,或將率先采用這一尖端制程。盡管廣發證券分析師Jeff Pu曾預測iPhone 18

臺積電3nm推出在即,EDA廠商陸續取得認證

臺積電3nm推出在即,EDA廠商陸續取得認證

評論