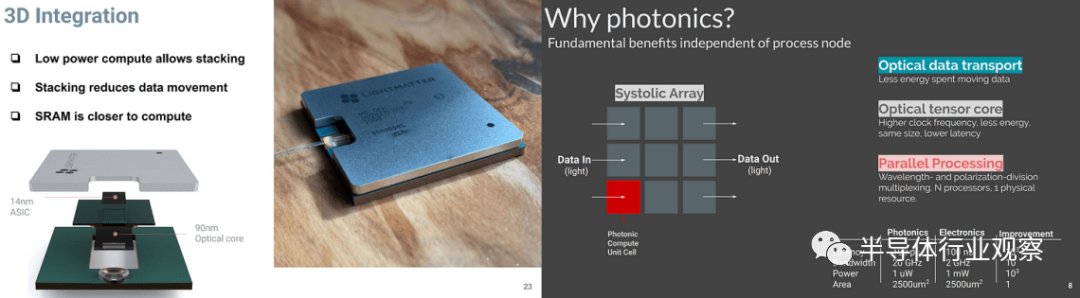

幾年前,Lightmatter 通過展示人工智能加速器 Mars 引起了轟動,該加速器重新思考了電子計算和移動數據的范式。他們展示了一種使用光子學進行計算的處理器。該芯片承諾將延遲、帶寬和功率提高多個數量級。由于芯片所涉及的軟件和計算結構的剛性,這最終沒有成功。

Lightmatter 已經創建了名為 Envise 的第二代 AI 計算產品,但這不是今天帖子的重點。我們想分享 Lightmatter 在他們的最新產品 Passage 上展示的內容。總結就是,Lightmatter 希望通過 Passage 打破高級封裝和 IO 的限制。

眾所周知,AI 和 HPC 等領域的問題規模呈指數級增長,但摩爾定律無法跟上。

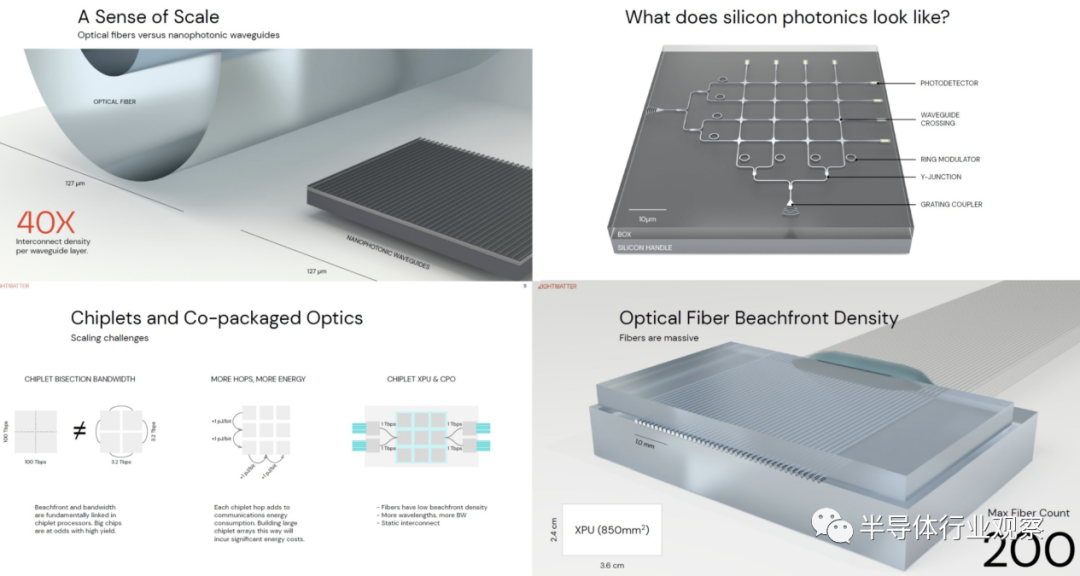

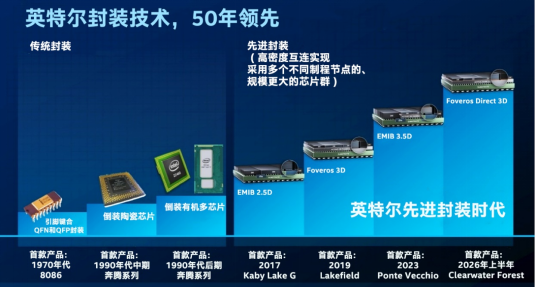

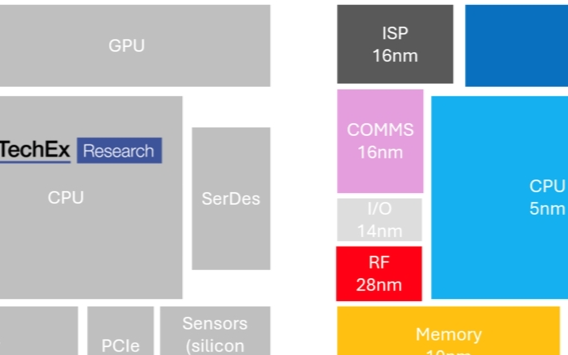

因此,該行業已轉向使用chiplet來組合更大的封裝,以繼續滿足計算需求。將芯片分解成許多chiplet并超過標線限制(光刻工具的圖案化限制的物理限制)將實現持續縮放,但這種范例仍然存在問題。即使采用先進的封裝,將數據移出芯片的電力成本也將成為限制因素。此外,即使采用最先進的封裝形式,帶寬仍然有限。

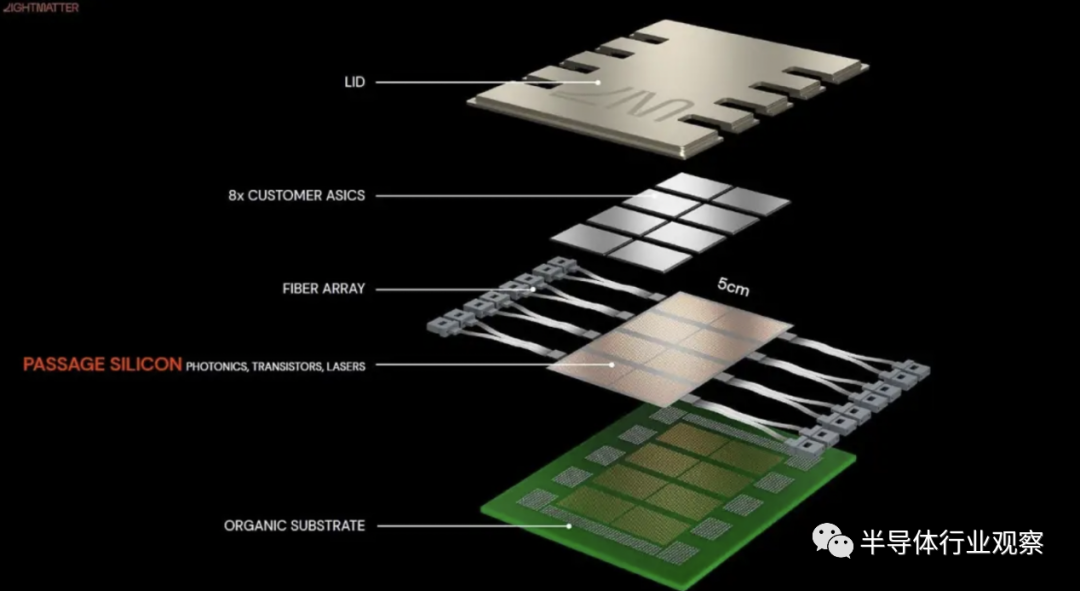

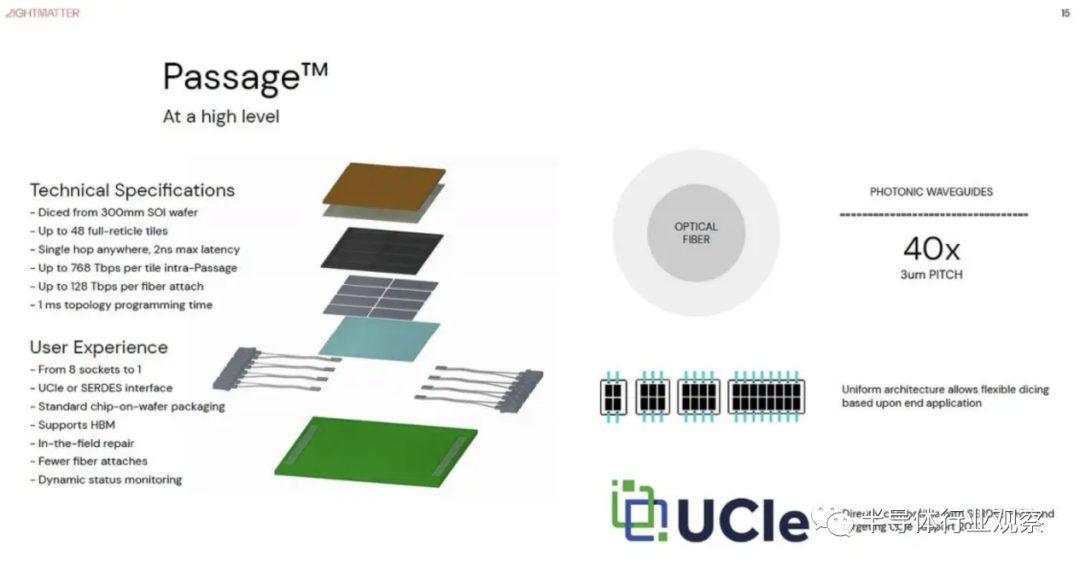

Lightmatter 不想將硅放在硅上,而是希望通過 Passage 顛覆先進的封裝游戲。Passage 連接到光學中介層上的 48 個客戶芯片。Passage 建立在GlobalFoundries Fotonix 45CLO 工藝技術之上。它旨在以非常高的帶寬和性能連接許多芯片。這種optical interposer打破了帶寬限制,在每個tile之間提供每秒 768 太比特,并且可以以每秒 128 太比特擴展到多個interposers,這是傳統封裝無法達到的能力和規模水平。

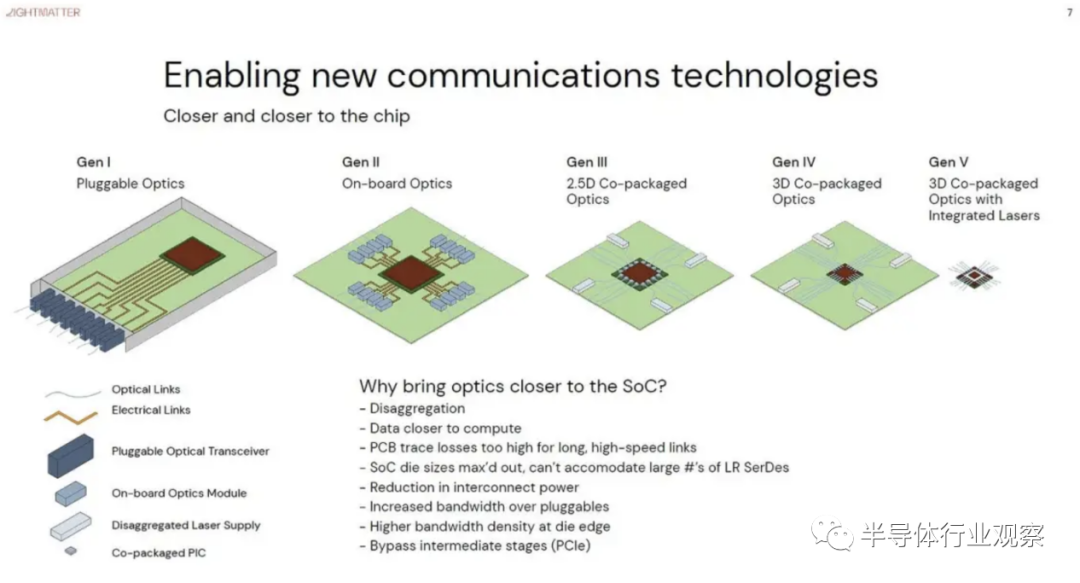

幾十年來,光學一直承諾解決電氣 IO 的瓶頸。技術在這方面的進展緩慢。Lightmatter 稱之為 Gen 1 的可插拔光學器件多年來一直用于連接數據中心內的交換機。由于英特爾和Ayar Labs等公司,第 2 代和第 3 代光學器件(將光學器件放在同一個封裝上或直接連接)開始進入網絡交換機和計算領域。Lightmatter 想通過 Passage 直接跳到第 4 代和第 5 代。

英特爾和 Ayar Labs 等標準聯合封裝光學器件的規模比 Lightmatter 使用的光學中介層解決方案低一個數量級。其互連密度高出 40 倍,因為單個芯片中只能插入大約 200 根光纖。此外,互連是完全靜態的,而 Passage 具有可動態配置的結構。

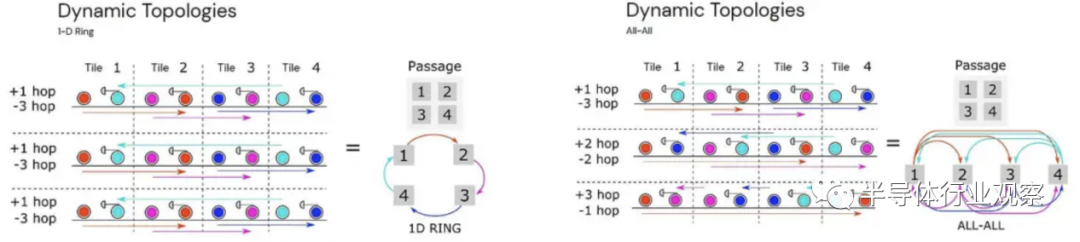

這種光中介層可以在芯片之間進行交換和路由。整個互連可以在 1ms 內重新配置。

Lightmatter 表示,他們可以支持所有拓撲,例如 all to all、1D ring、Torus、Spine 和 Leaf 等等。Passage 的交換和路由在 48 芯片陣列上的任何芯片與任何其他芯片之間的最大延遲為 2ns。

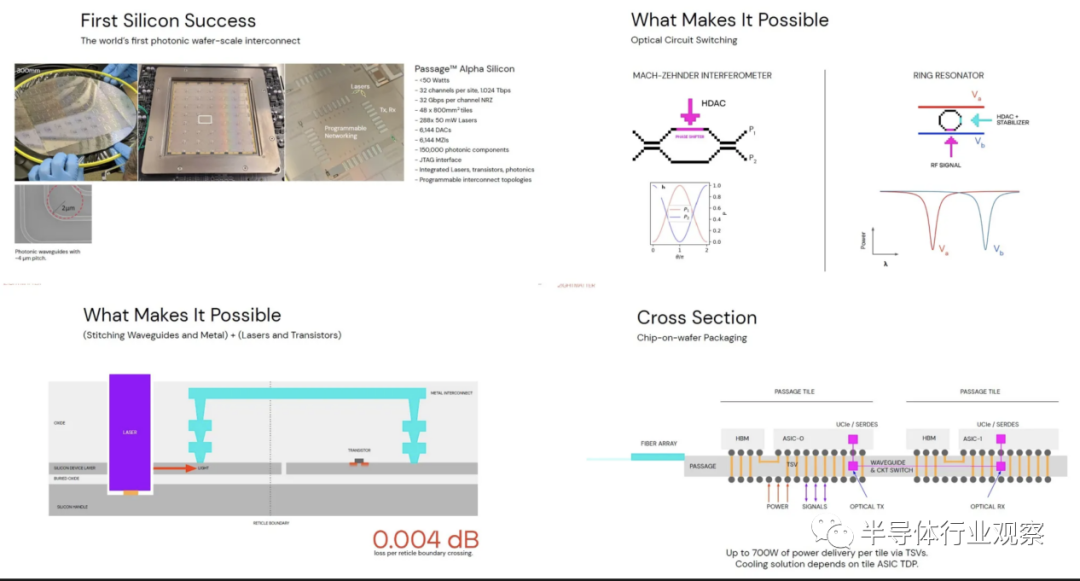

切換是通過使用環形諧振器調制顏色并使用馬赫-曾德干涉儀來引導它們來實現的。

Lightmatter 的光子晶圓級中介層具有 A0 硅,并聲稱每個站點使用的功率不到 50 瓦。每個站點有 8 個混合激光器驅動 32 個通道;每個通道運行 32Gbps NRZ。

Lightmatter 的晶圓級硅光子芯片主要采用硅基制造技術;它有許多相同的限制。即光刻工具的標線限制。GlobalFoundries 和 Lightmatter 通過縫合波導解決了這個問題。納米光子波導的光罩間連接在每個光罩交叉處僅具有 0.004 dB 的損耗。波導損耗為 0.5 dB/cm,每個 Mach-Zehnder 干涉儀損耗為 0.08 dB。每次交叉也有 0.028 dB 的損耗。

Lightmatter 表示,借助 UCIe,他們可以運行最高規格的 32Gbps chiplet到中介層互連。如果使用直接 SERDES,他們相信它們可以以 112G 的速度運行。客戶 ASIC 被 3D 封裝在中介層之上。然后 OSAT 將組裝這個最終產品。它可以有多種變體,從 48 個芯片到只有 8 個芯片的更小的interposer。passage封裝還必須為封裝在頂部的芯片供電。它通過使用 TSV 為每個tile提供高達 700W 的功率來做到這一點。在這個功率級別需要水冷,但如果客戶 ASIC 消耗較少,他們可以使用空氣冷卻。

請注意,聲稱的 768Tbps 似乎在很大程度上被浪費了。它們的功能似乎允許它們將一個輸入耦合到一個輸出。這使得大部分互連空閑。為了讓他們找出不沖突的途徑,這將是必要的。這些路徑是被動的,在不使用時幾乎不會浪費電力。MZI 元素向左或向右。沒有混合(blending),沒有多播(multicasting)。一進一出。

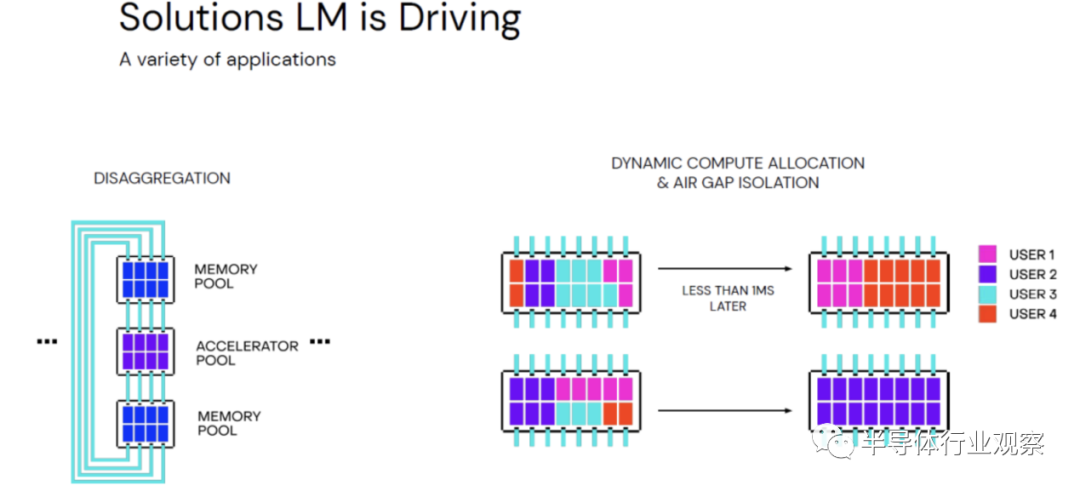

Lightmatter 還舉了一個分解內存設計和多租戶架構的例子。他們開始他們的 interposer可以支持任何協議,包括 CXL。interposer頂部的客戶 ASIC 可以通過重新配置網絡實現氣隙,因此在特定芯片之間傳遞數據是不可能的。最大的問題是產品是否會出現以及何時會出現。這可能只是vaporware,也可能是高端領先的分類服務器設計的未來。Lightmatter 必須吸引其他公司為這個平臺制造芯片。這些公司必須將其昂貴的開發信任與未經證實的合作伙伴。

審核編輯 :李倩

-

封裝

+關注

關注

128文章

9235瀏覽量

148433 -

人工智能

+關注

關注

1815文章

50053瀏覽量

264525 -

chiplet

+關注

關注

6文章

493瀏覽量

13574

原文標題:顛覆先進封裝,光芯片走向Chiplet

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

先進封裝時代,芯片測試面臨哪些新挑戰?

Chiplet核心挑戰破解之道:瑞沃微先進封裝技術新思路

Chiplet封裝設計中的信號與電源完整性挑戰

Chiplet與先進封裝全生態首秀即將登場!匯聚產業鏈核心力量共探生態協同新路徑!

華大九天推出芯粒(Chiplet)與2.5D/3D先進封裝版圖設計解決方案Empyrean Storm

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

突破!華為先進封裝技術揭開神秘面紗

時擎科技受邀亮相無錫先進封裝產業發展高峰論壇并發表主題演講

英特爾先進封裝:助力AI芯片高效集成的技術力量

全面剖析倒裝芯片封裝技術的內在機制、特性優勢、面臨的挑戰及未來走向

Chiplet 顛覆芯片創新,一文看懂計算平臺大廠 Arm 的布局藍圖

光芯片走向Chiplet,顛覆先進封裝

光芯片走向Chiplet,顛覆先進封裝

評論