1. 為什么使用PCIe傳輸

在FPGA需要和處理器打交道時,無論是X86,還是PowerPC,以及一些嵌入式的ARM等,對外的接口常見如下表。

其中,USB需要外部的PHY對接FPGA,而且需要firmware;以太網走到TCP才會保證不丟數據;PCI逐漸淘汰了,占用引腳多,而且帶寬有限;SATA側重存儲,其協議的局限性比較高;RapidIO在一些場合使用,結構可以做到Full Mesh結構,但是這些年發展速度比較慢。

而PCIe具備如下優點:

A. 帶寬高,目前FPGA有PCIe Gen3 x16,或者PCIe Gen4 x8,鏈路速度可以達到128Gbps;

B. FPGA直連,不需要外部PHY;

C. 協議保證數據無誤傳輸,兩級CRC,重傳機制,保證數據無誤;

D. 軟件生態豐富,各種系統原生支持,通過簡單的驅動就可以完成數據交互;

E. 在PCIe之上的協議逐漸增多,例如NVMe是基于PCIe的上層協議;

Xilinx從15年前,V4系列開始,一直在PCIe的解決方案上深耕,提供眾多的應用方案級的解決方案,方便用戶專注于自己的應用。早期,Xilinx提供的有Application Notes,例如XAPP859,XAPP1052等,構建了基本的雙向數據傳輸。當時一些第三方公司,類似于PLDA,NwLogic也出針對Xilinx FPGA的PCIe傳輸方案。

后來,Xilinx團隊2017年附近推出XDMA解決方案,并持續增加功能、修正Bug,到目前為止,XDMA已經成為一個功能強大、成熟穩定的Xilinx FPGA解決方案。功能上涵蓋了SG功能,AXI-Lite功能,多通道分離,AXI-MM和AXI-Stream支持等。穩定性上,經過4年的逐步完善,目前已經有眾多的客戶基于這套方案實現產品,涵蓋醫療、電力、通訊、數據中心等各種應用。

最重要的是,XDMA是免費的!!!

2. XDMA IP配置實例

Xilinx XDMA支持的系列包括7系列,UltraScale系列,UltraScale+系列各種系列,界面配置基本相同。這里以KU040的一個板子做例程,其他系列可以參考。Vivado使用2018.3,Vivado的版本,做XDMA,建議盡量使用新一些的版本。詳細的說明,參考Xilinx的文檔PG195,下面主要摘取影響使用的關鍵部分。

配置IP

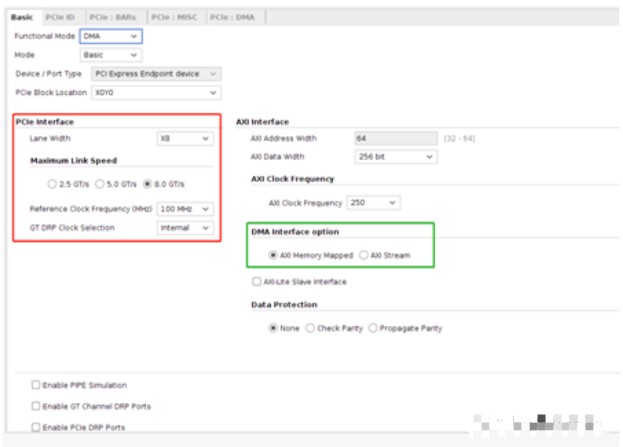

第一頁,IP基本配置。

紅色框根據實際板卡硬件來選擇,Lane Width是物理的位寬;Link Speed是希望運行在那個速率。速率和位寬越高,最終的帶寬就越高,對應FPGA內的資源和頻率也相對多一些。

綠色框是選擇接口方式,AXI Memory Mapped選擇用戶接口是AXI內存映射的接口,常見用于對接DDR、RAM等有地址尋址的外設。AXI Stream的用戶接口是流接口,類似于一段數據包,FIFO流等。IP只能支持其中一種選擇,不能說多通道混合使用不同的用戶接口,所以用戶需要分析自己的數據接入方式,慎重選擇。

常見的,例如ADC采集,如果帶DDR,則可以把ADC暫存在DDR中,XDMA使用AXI-MM的方式讀取DDR數據;也可以ADC通過FIFO緩存后,XDMA使用AXI-Stream讀取FIFO,不過需要注意ADC速度非常高的時候容易溢出。

例如,讀取外部網絡報文,報文長短不一,使用AXI-Stream接口方式比較合適。

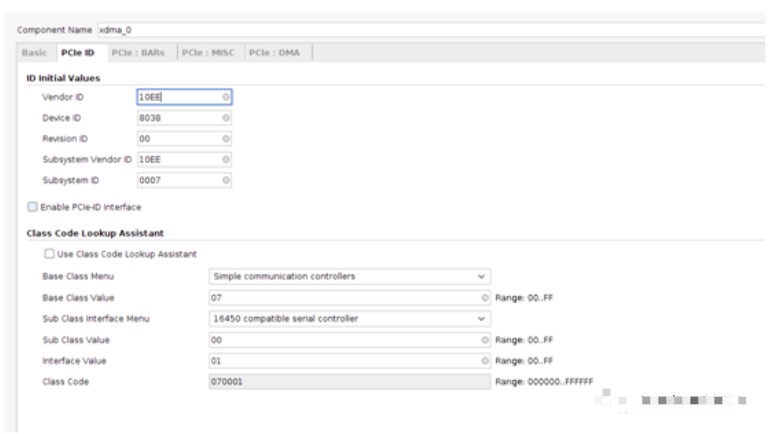

第二頁,VID,DID,Class等選擇。

如果沒有特殊的需要,這一頁可以不變。尤其是Vendor ID,Device ID,盡量不修改,因為Xilinx提供的驅動是對應這些VID,DID的。

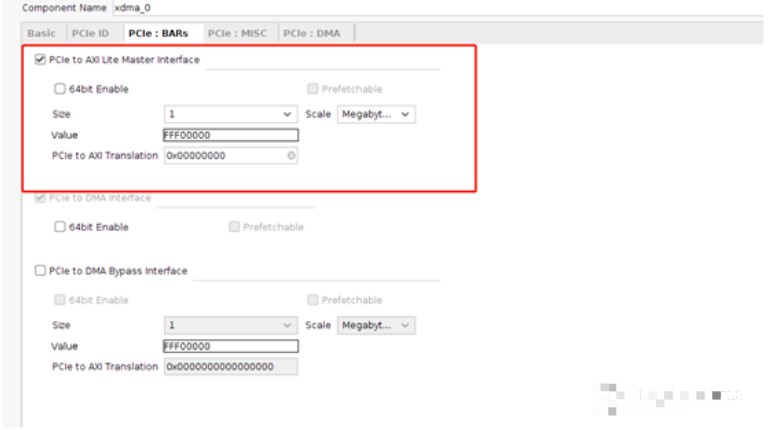

第三頁,PCIe BAR空間。

紅色框,PCIe to AXI Lite Master Interface可以選擇上。通常,這個接口可以用作寄存器接口。上位機需要控制板卡內的用戶寄存器,可以通過這個接口擴展。

通常來說,寄存器接口盡量對齊,比如常用32bit寄存器。

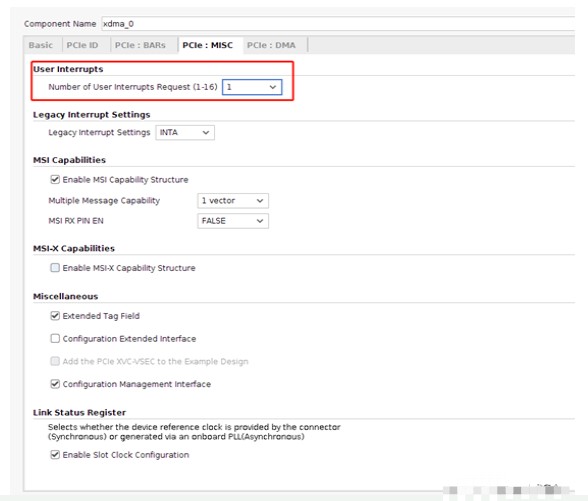

第四頁,雜項

需要關注的是用戶中斷數量,是從用戶層通知CPU的中斷。注意,XDMA本身的操作中斷不算在內,這里是用戶產生的中斷。

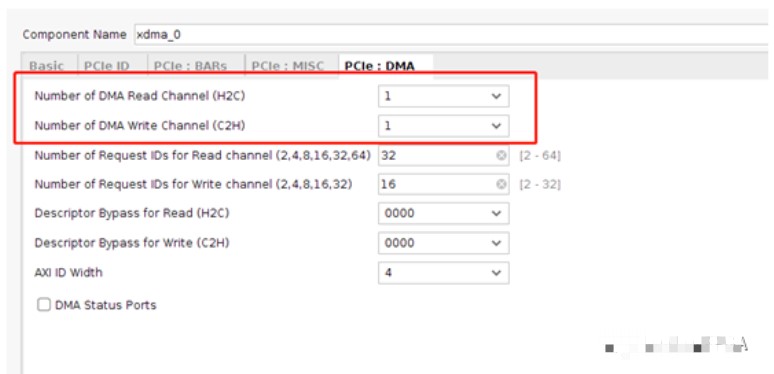

第五頁,DMA通道選擇

需要關注的是紅色框,讀寫通道數量選擇,根據實際的業務來選擇。例如有4路ADC數據傳輸,可以選擇C2H為4,當然,也可以4路ADC數據在FPGA內合并后成1路,然后只選擇C2H為1 。

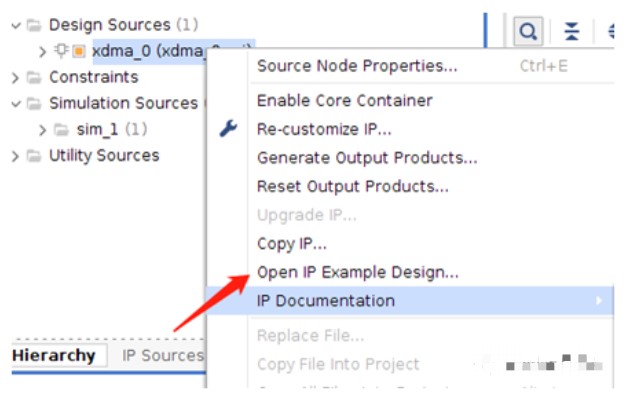

生成example design例程

上一步IP配置后,在生成的IP上,右鍵點擊,選擇打開open example design。

生成的例程,如果選擇是AXI-MM的用戶接口,那么這個接口對接的是AXI接口形式的Block RAM,上位機可以讀/寫這片RAM。如果選擇的是AXI-Stream接口,例程中將Stream讀寫環回,上位機寫下去的內容再讀回去。

此外,第三頁BAR空間如果勾選了PCIeto AXI Lite Master Interface,例程中會額外多出來一個AXI接口的Block RAM。如果需要,可以將這塊修改為寄存器接口。

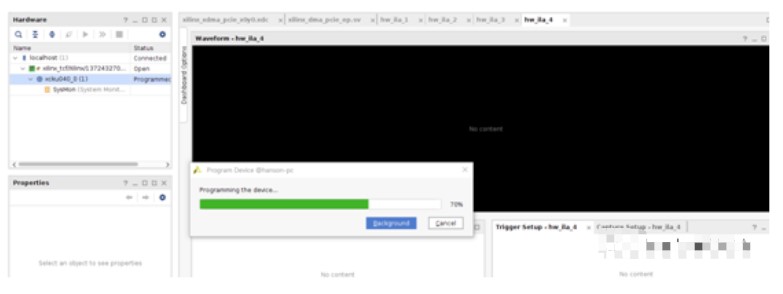

修改約束引腳后,生成bit文件,下載到FPGA中,并重啟電腦,注意這里說的是重啟電腦,不是關機再開機。電腦重啟的開始,BIOS會重新掃描PCIe設備,才能被CPU枚舉。

3. Block Design下快速構建XDMA Subsystem

上面的例程,例化一個IP,然后打開example design的方式。實際使用,可以用block design快速構建XDMA的設計。

下面舉例,快速構建一個XDMA到DDR4傳輸的設計。

1. 新建block design,加入XDMA IP和DDR4 MIG IP。XDMA配置參考上面描述的內容,DDR4根據板卡實際的選擇配置。

2. 連接關系很簡單,XDMA的M_AXI接口通過AXI_Interconnect連接DDR4,這里AXI_Interconnect起到時鐘域轉換的作用。

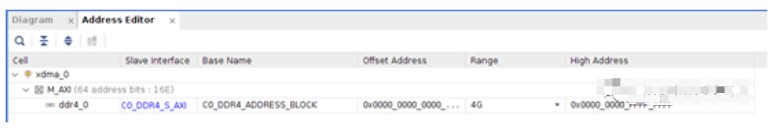

3. 地址分配,將DDR4的空間分配到XDMA中即可。

4. 生成block design的wrapper,修改正確的引腳約束后,生成bit文件。下載到FPGA后重啟電腦。

Block Design的方式,適用于快速構建比較復雜的設計,例如包含DDR4,Datamover等各種基于AXI互聯的IP。

4. 驅動和軟件應用

通過pci utility查看設備

pci utility工具,用于查看PCIe設備各種屬性的工具。Linux系統默認自帶了pci utility工具,windows下也有對應版本,在GitHub上搜索。

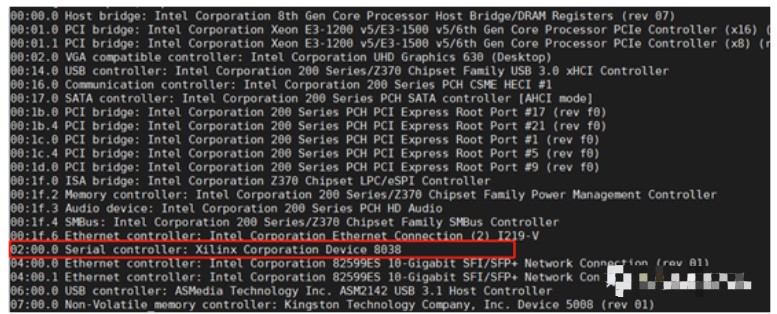

lspci命令,列舉所有pci和pcie設備:

紅色框,即上面配置的XDMA example design。

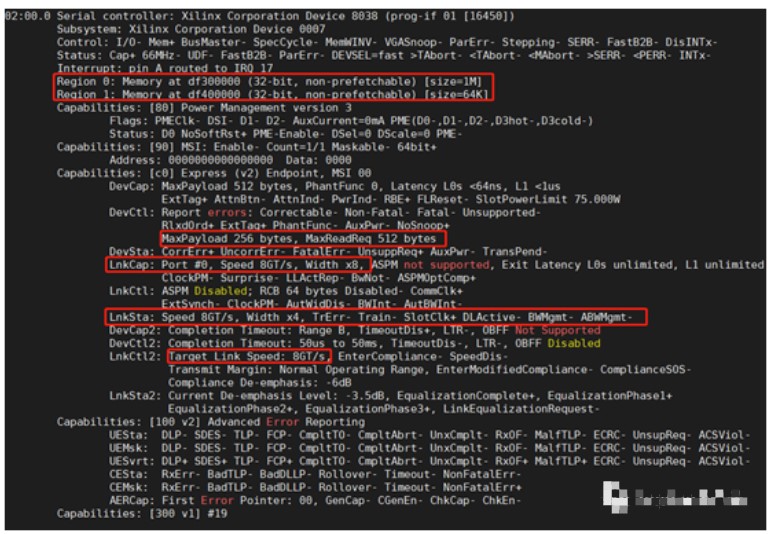

lspci -vv -s 02:00.0 命令,詳細列出位于02:00.0槽位的Xilinx設備詳細信息。

這里把一些信息列舉下來:

A. Region 0,這個是上面PCIe to AXI Lite Master Interface選擇的空間。Region 1,這個是XDMA IP自身內部寄存器空間,不用關心。

B. MaxPayload size是256字節,是系統協商的,不能修改。MaxReadReq是最大請求字節,協商后是512字節。

C. LnkCap字段,是協商后的PCIe鏈路狀態,上面寫的速度是8G,位寬是x4。PCIe IP上選擇的是8G,這個目前協商到了。位寬選擇x8,實際是x4,因為這個機箱用的一個x4PCIe延長線,限制了適配到x8位寬。

D. LnkCtl2,顯示設備最大能支持到8G的鏈路速度。

5. 驅動安裝,Linux環境

Linux的驅動在GitHub上,https://github.com/Xilinx/dma_ip_drivers,下載到宿主機。

readme.txt中有驅動使用說明,目錄結構、安裝使用等。tests目錄下有安裝腳本,測試腳本等。

5.1. 驅動安裝

tests目錄下,sh load_driver.sh即安裝驅動,安裝成功會提示。

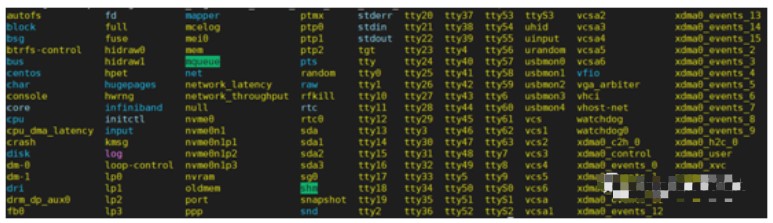

安裝完畢,查看/dev目錄下,多出來一些xdma0開頭的設備。

文件目錄分別說明下

A. _c2h_x,是card to host的設備,板卡向CPU傳輸數據的時候使用這個設備;

B. _h2c_x,是host to card的設備,CPU向板卡發送數據的時候使用這個設備;

C. _control,是XDMA的內部寄存器控制設備,一般用戶不需要使用;

D. _user,是PCIe to AXI Lite Master Interface選擇的空間;

E. _event_x,是IP配置第四頁,選擇的用戶層中斷對應的設備;

5.2 軟件測試,Linux環境

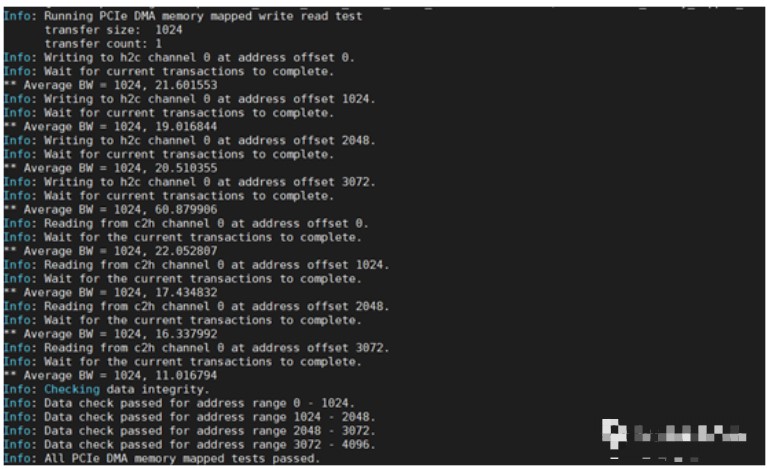

如果IP配置選擇AXI-Memory Map,參考dma_memory_mapped_test.sh,這個腳本寫入一段數據到BlockRAM中,然后讀出對比。

如果IP配置選擇AXI-Stream接口,參考dma_streaming_test.sh,腳本寫入一段數據,回環后讀回校驗。

上述兩個例子,用下面的命令測試。

sh dma_memory_mapped_test.sh 1024 1 1 1

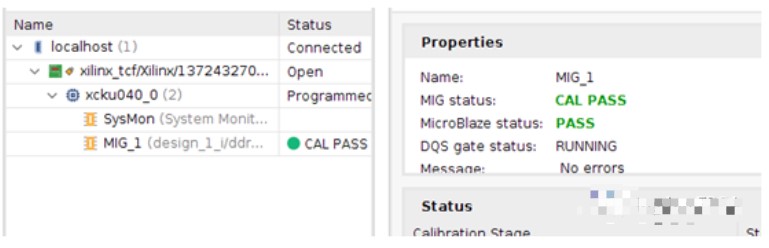

Block Design下,DDR4顯示已經校準完畢。使用dma_memory_mapped_test.sh測試,數據寫入DDR4,然后再從DDR4讀回。

FAQ

1. Windows下安裝驅動,安裝后驅動有一個感嘆號,不能正常使用。

Windows從Win764bit開始,安裝驅動必須的簽名,Win7的簽名和Win10的簽名還不同。Xilinx提供的Windows驅動不包括驅動簽名,安裝的時候就出現感嘆號。

這個問題可以百度下,開機的時候選擇禁止驅動簽名。或者購買微軟的簽名即可。

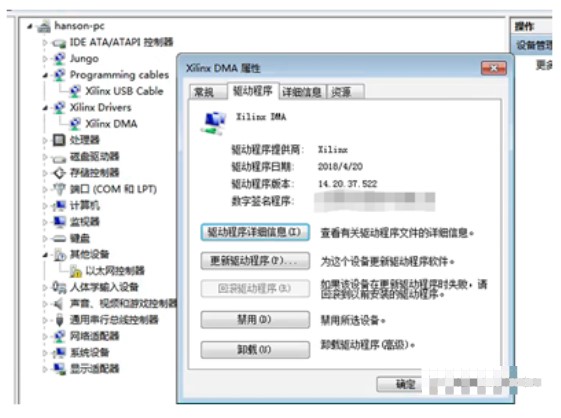

例如下圖,是一個公司購買了簽名,簽名這個驅動后的狀態,可以直接安裝好驅動。

2. Linux下,Stream模式接收溢出。

IP設置為Stream模式,默認Linux上有循環Buffer來處理接收的數據。如果Stream接收的速率太高,超過驅動和應用能處理的范圍,就會出現溢出的問題。出現溢出后,驅動里做了錯誤恢復,一段數據就丟掉了。

審核編輯:劉清

-

處理器

+關注

關注

68文章

20250瀏覽量

252186 -

FPGA

+關注

關注

1660文章

22408瀏覽量

636199 -

USB接口

+關注

關注

9文章

715瀏覽量

59017 -

PCIe

+關注

關注

16文章

1460瀏覽量

88391

發布評論請先 登錄

求 CS32G020移動電源EVB用戶使用指南 中的清晰原理圖

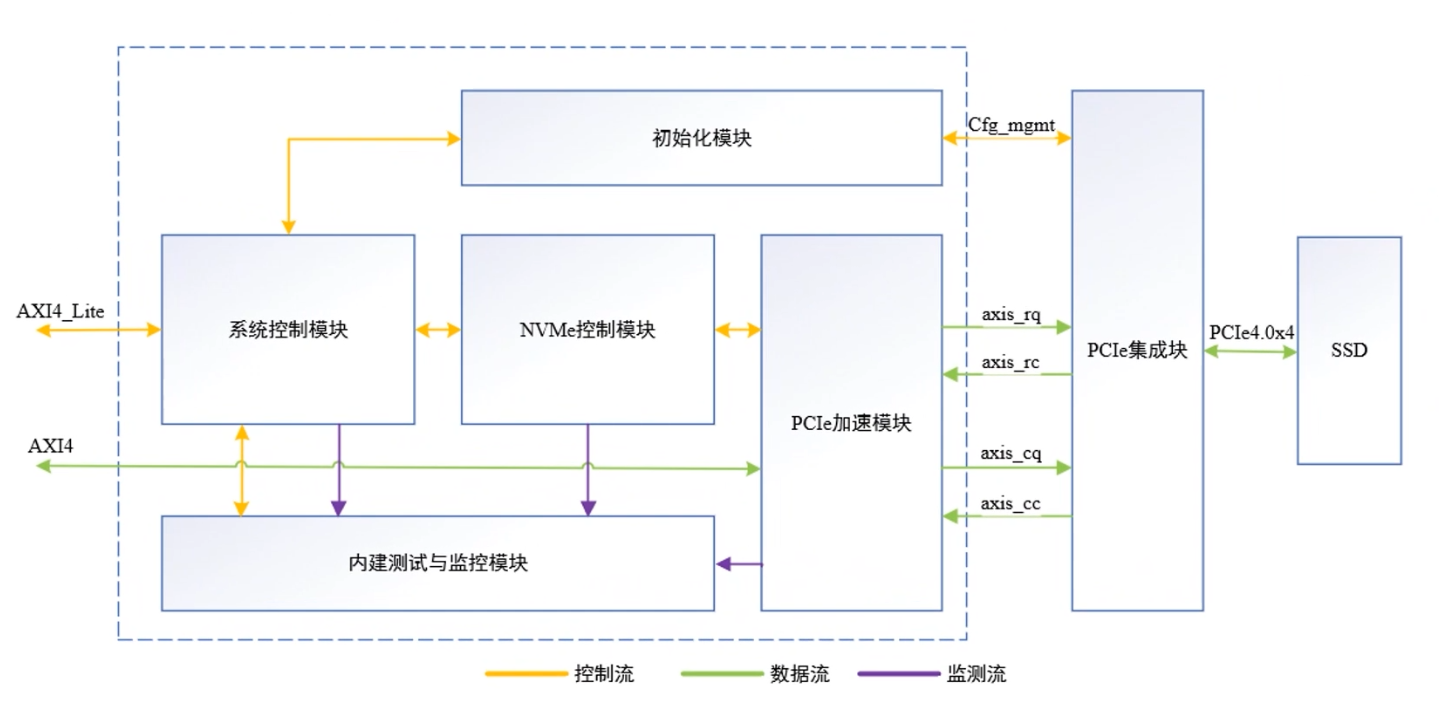

NVMe高速傳輸之擺脫XDMA設計20: PCIe應答模塊設計

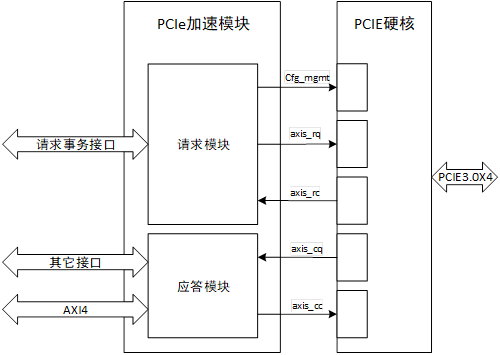

NVMe高速傳輸之擺脫XDMA設計17:PCIe加速模塊設計

NVMe高速傳輸之擺脫XDMA設計14: PCIe應答模塊設計

NVMe高速傳輸之擺脫XDMA設計13:PCIe請求模塊設計(下)

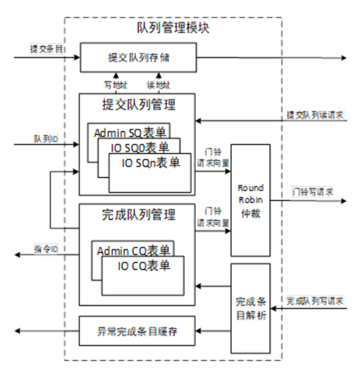

NVMe IP高速傳輸卻不依賴XDMA設計之九:隊列管理模塊(上)

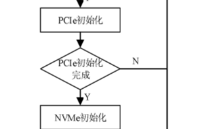

NVMe IP高速傳輸卻不依賴XDMA設計之八:系統初始化

NVMe IP高速傳輸卻不依賴便利的XDMA設計之一

NVMe IP over PCIe 4.0:擺脫XDMA,實現超高速!

基于PCIe(XDMA/QDMA)的多路視頻采集與顯示IP 多路高速AD采集與DA回放IP

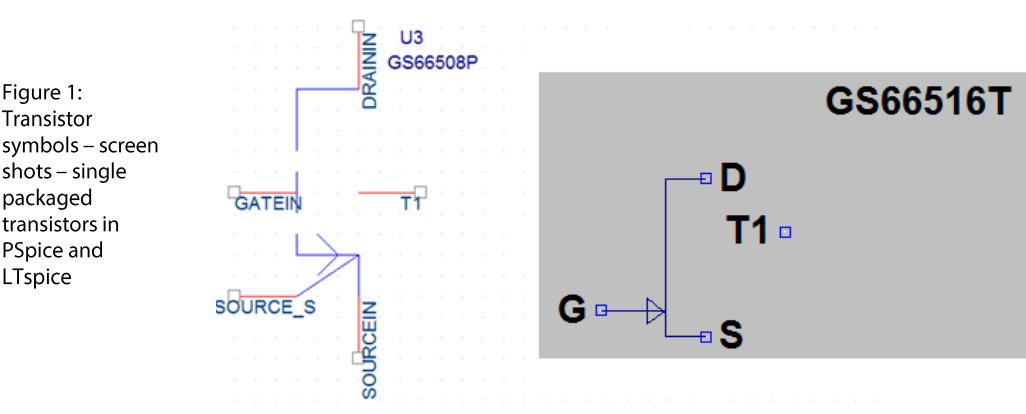

GaN HEMT的SPICE模型使用指南及示例

Xilinx PCIe XDMA使用指南

Xilinx PCIe XDMA使用指南

評論