采用XDMA是許多人常用xilinx庫實現NVMe或其他傳輸的方法。但是,XDMA介紹較少,在高速存儲設計時,尤其是PCIe4.0模式下,較難發揮其最優性能,因此,直接采用PCIe實現NVMe功能。

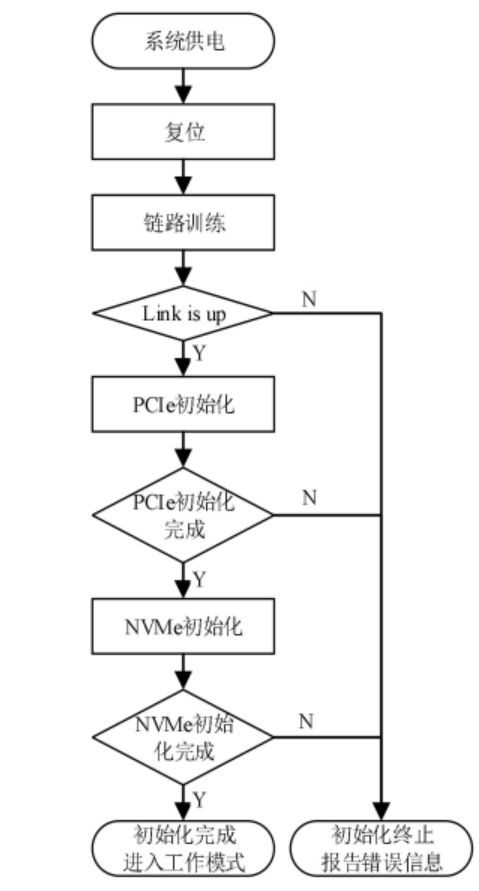

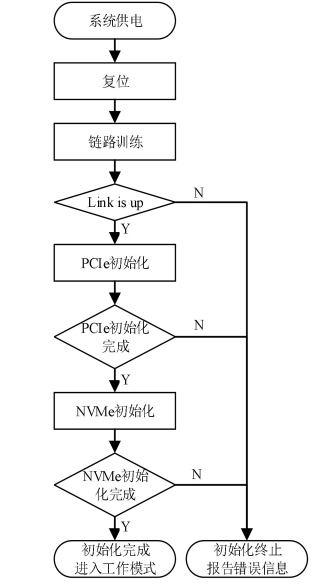

這里主要分享基于PCIe3.0接口的NVMe IP設計簡介。有需要更高性能需求的,請先了解其性能簡介,在文末給出鏈接。它的系統初始化流程主要分為鏈路訓練、PCIe 初始化和 NVMe 初始化, 分別實現 PCIe鏈路連接、 PCIe 設備枚舉配置和 NVMe 設備配置功能。 其中鏈路訓練由 PCIE 集成塊實現, 初始化模塊根據鏈路訓練完成信號和初始化啟動信號來執行 PCIe 初始化和NVMe 初始化。

圖1 系統初始化流程

系統初始化的主要流程如圖 1 所示, 在系統供電后, 首先進入復位狀態, 一旦退出復位狀態, 由 PCIE 集成塊執行鏈路訓練, PCIE 集成塊提供了 LinkUp 信號用于指示鏈路訓練是否成功。 鏈路訓練消耗時間為毫秒級別, 為了確保系統的穩定, 在系統復位退出后 1 秒時如果 LinkUp 信號仍為低電平, 則斷言為鏈路訓練失敗, 初始化流程終止。

如果 LinkUp 為高電平, 此時用戶可通過系統控制模塊啟動 PCIe 初始化,進入 PCIe 初始化狀態。 PCIe 初始化狀態機在執行完初始化流程后, 會報告初始化執行狀態, 如果在初始化過程中出錯, 進入初始化終止狀態并將錯誤信息反饋到初始化狀態寄存器。 當 PCIe 初始化正常完成后, 可以進入 NVMe 初始化狀態, NVMe 初始化也由用戶通過系統控制模塊啟動。 當 NVMe 初始化正常完成后, 系統的初始化完成, NoP 邏輯加速引擎進入正常工作模式。

-

高速傳輸

+關注

關注

0文章

39瀏覽量

9270 -

高速存儲

+關注

關注

0文章

15瀏覽量

6063 -

nvme

+關注

關注

0文章

289瀏覽量

23741

發布評論請先 登錄

NVMe IP高速傳輸卻不依賴便利的XDMA設計之三:系統架構

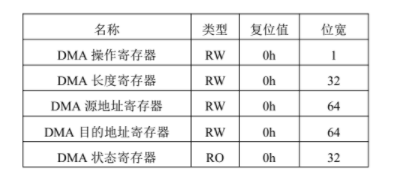

NVMe IP高速傳輸卻不依賴XDMA設計之五:DMA 控制單元設計

NVMe高速傳輸之擺脫XDMA設計之十:NVMe初始化狀態機設計

NVMe高速傳輸之擺脫XDMA設計33:初始化功能驗證與分析

NVMe高速傳輸之擺脫XDMA設計34:初始化功能驗證與分析2

NVMe高速傳輸之擺脫XDMA設計35:初始化功能驗證與分析3

NVMe IP高速傳輸卻不依賴XDMA設計之二:PCIe讀寫邏輯

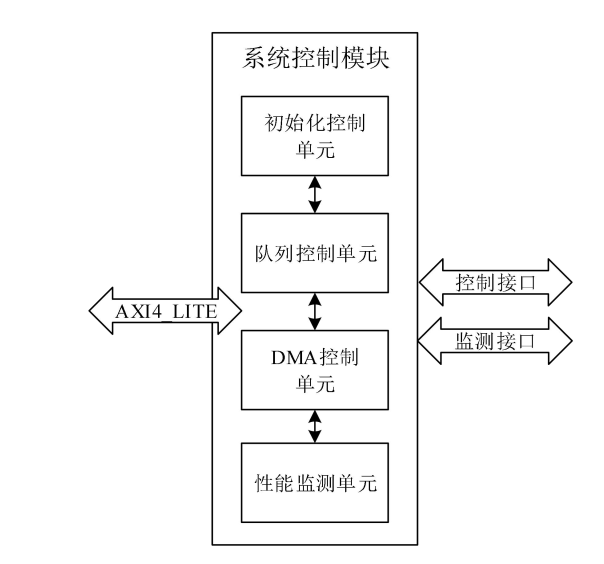

NVMe IP高速傳輸卻不依賴XDMA設計之四:系統控制模塊

NVMe IP高速傳輸卻不依賴XDMA設計之五:DMA 控制單元設計

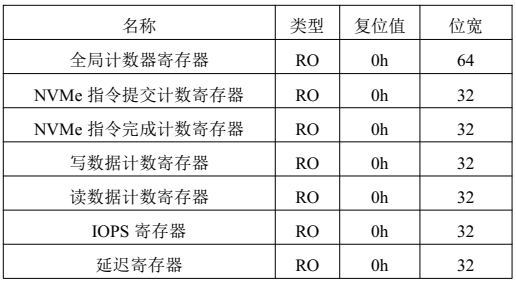

NVMe IP高速傳輸卻不依賴XDMA設計之六:性能監測單元設計

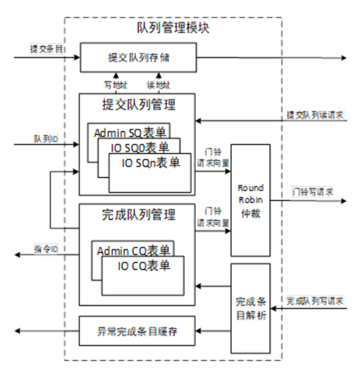

NVMe IP高速傳輸卻不依賴XDMA設計之九:隊列管理模塊(上)

NVMe IP高速傳輸卻不依賴XDMA設計之八:系統初始化

NVMe IP高速傳輸卻不依賴XDMA設計之八:系統初始化

評論