在很多Vivado的高速接口的IP中,比如Ethernet、PCIe、SRIO的設(shè)置中,都會(huì)有個(gè)Shared Logic的頁(yè)面:

可能很多同學(xué)并沒(méi)有很關(guān)注這個(gè)頁(yè)面,直接默認(rèn)設(shè)置就完事了。

但其實(shí)這個(gè)頁(yè)面的內(nèi)容也是非常有用的,我們可以看到頁(yè)面中有兩個(gè)選擇:

- Include Shared Logic in core

- Include Shared logic in example design

首先,什么是Shared Logic?字面意思很好理解,就是共享邏輯,主要包括時(shí)鐘、復(fù)位等邏輯。當(dāng)選擇Shared Logic in core時(shí),這些共享的邏輯就會(huì)被集成到IP的內(nèi)部,也就是說(shuō)這些邏輯是不能被修改的。當(dāng)選擇Shared Logic in example design時(shí),這些共享邏輯就會(huì)出現(xiàn)在IP的接口上,我們可以根據(jù)自己的需求進(jìn)行控制,那為什么叫in example design呢?因?yàn)閂ivado的IP都會(huì)提供一個(gè)example,在shared logic在example中就相當(dāng)于是這些邏輯是對(duì)外開(kāi)放的。

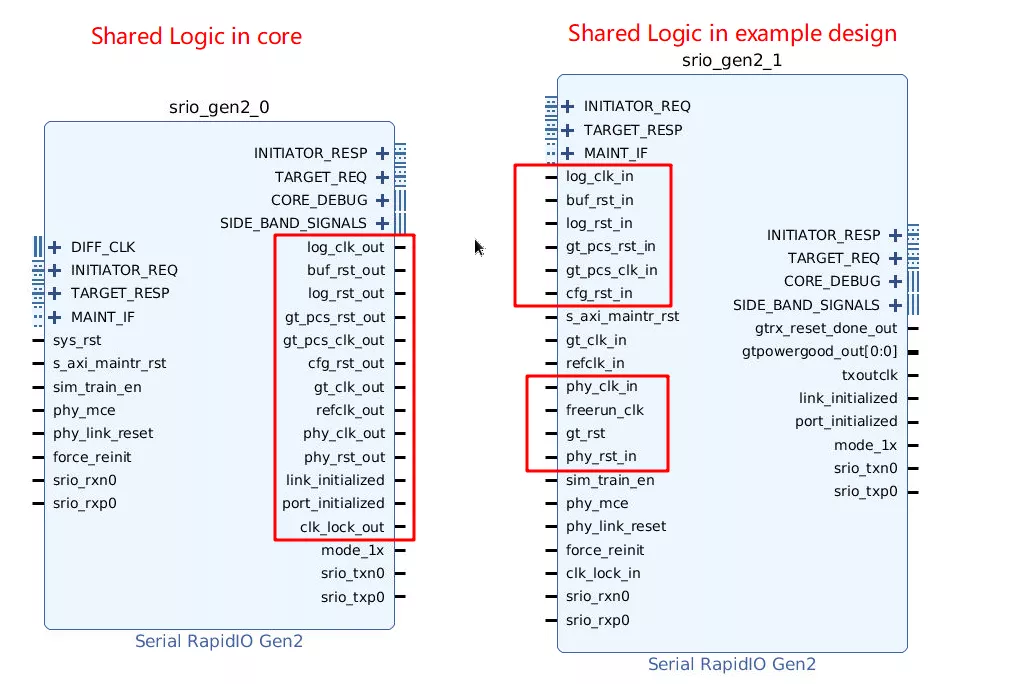

我們以SRIO IP Core為例,下圖顯示了Shared Logic in core和Shared Logic in example design接口上的區(qū)別,可以看到,Shared Logic in core的輸入接口是比較少的,因?yàn)檫@些時(shí)鐘和復(fù)位的邏輯都被集成到了內(nèi)部,但這些IP提供了這些邏輯的輸出接口,我們?cè)谕饷婵梢员O(jiān)測(cè)這些邏輯是否正確;Shared Logic in example design的輸入接口明顯要多一些,這些時(shí)鐘、復(fù)位接口都需要我們自己提供,靈活性更強(qiáng),當(dāng)然我們可以直接參考example中的控制方式。

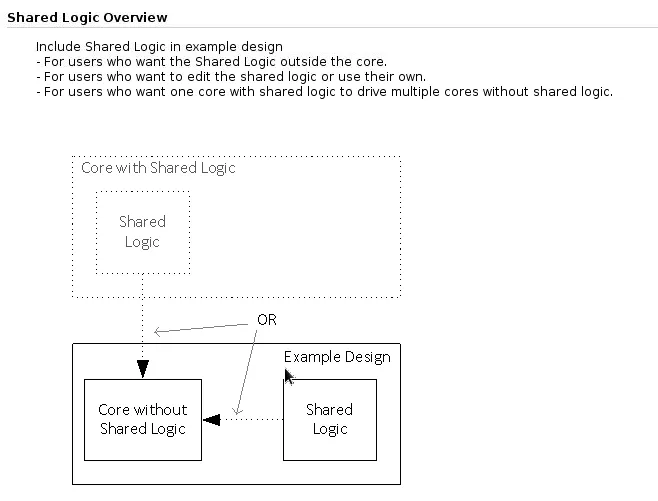

看懂上面這些,我們也就理解IP設(shè)置頁(yè)面中下面這個(gè)圖的含義了。

-

IP

+關(guān)注

關(guān)注

5文章

1872瀏覽量

156228 -

Logic

+關(guān)注

關(guān)注

1文章

97瀏覽量

48075 -

Vivado

+關(guān)注

關(guān)注

19文章

859瀏覽量

71273

發(fā)布評(píng)論請(qǐng)先 登錄

請(qǐng)問(wèn)Keil中的map文件到底是什么意思?

在vivado中是否有像Logic Lock這樣的功能

Northwest Logic支持Xilinx IP集成器工具流

如何在Vivado Design Suite 中進(jìn)行IP加密

如何使用Vivado Logic Analyzer與邏輯調(diào)試IP進(jìn)行交互

如何在Vivado Logic Analyzer中新儀表板,及使用的好處有哪些

在Vitis中把Settings信息傳遞到底層的Vivado

Vivado中BRAM IP的配置方式和使用技巧

Vivado IP核Shared Logic選項(xiàng)配置

Vivado中IP核被鎖定的解決辦法

Vivado IP中的Shared Logic到底是干嘛的

Vivado IP中的Shared Logic到底是干嘛的

評(píng)論