在工業中,我們看到越來越多的系統示例是通過利用 2.5D 或 3D 連接的異構集成來構建的。在本次采訪中,imec 高級研究員、研發副總裁兼 3D 系統集成項目總監 Eric Beyne 回顧了趨勢并討論了構建下一代 3D 片上系統所需的技術。各級報告的進展將使系統設計和開發進入下一個層次,有望在系統的功率-性能-面積-成本 (PPAC) 指標方面獲得巨大回報。

未來幾年哪些主要趨勢將標志著您的研究領域?

Eric Beyne:“傳統的 CMOS 技術規模化——產生單片 CMOS 單芯片片上系統 (SOC)——將通過技術、材料和器件架構的創新持續到下一個十年。CMOS 縮放越來越多地得到設計-技術-協同優化 (DTCO) 的補充,以提高系統的功率、性能、面積和成本 (PPAC)。但隨著成本和技術復雜性的增加,這些方法不再在系統級別提供足夠的收益。對于數據密集型高性能應用程序尤其如此,這些應用程序受到所謂的內存墻的挑戰——難以足夠快地訪問數據。

為了進一步優化系統的 PPAC 指標,半導體行業越來越關注多芯片異構集成解決方案。

采用這種方法,可以分別優化芯片上的不同功能(使用不同的(節點)技術),并且可以在系統的子組件之間實現更短、更快的連接。第一個“異構”實現(例如高帶寬存儲器 (HBM))主要依賴 2.5 或 3D 小芯片方法,涉及單獨設計和處理的小芯片裸片。芯片間通信主要使用標準化接口物理層 (PHY) IP 塊實現,將應用程序限制為延遲容忍功能,例如最后一級內存緩存。

盡管小芯片方法大大拓寬了異構系統集成的范圍,但我們將見證向真正的 3D-SOC 設計的演變,其中不再需要中間接口 PHY 層。這些 3D SOC 將通過巧妙地共同設計不同的 3D 分區和實現直接的 die-to-die 3D 互連來實現。”

imec 正在探索哪些途徑來克服未來的挑戰?

“實現最佳 3D SOC 需要重新設計系統架構,需要對電子設計自動化 (EDA) 工具進行創新,以便在一個視圖中實現不同設備的協同設計。

在這種情況下,imec 與其在 EDA 軟件方面的合作伙伴合作,開發用于自動網表分區和 3D 路徑優化的解決方案。在這種情況下,我們最近報道了一種新的 3D 設計流程——與 Cadence 合作開發。該軟件有助于預測所提議的 3D 分區是否會產生強大且功能齊全的 3D SOC,從而使異構集成更接近工業現實。

其他貢獻來自 3D 集成技術開發——這是 3D SOC 的關鍵推動力。與我們的材料和設備供應商一起,我們開發了多種 3D 互連技術,涵蓋從毫米(封裝堆疊)到小于 100 納米(晶體管堆疊)的各種互連間距。我們開發了高效的冷卻解決方案(例如基于沖擊的冷卻),以更有效地處理日益密集的高性能片上系統中不斷增加的功率。”

還有其他值得一提的技術發展嗎?

“背面供電 (BSPD) 是另一項很有前途的技術開發,可幫助實現高性能應用的 3D SOC。

在 BSPD 網絡 (BSPDN) 中,電源傳輸和電源轉換從邏輯芯片的正面移到其背面 - 到目前為止,它僅用作載體。因此,可以通過變薄的背面直接向先進的微處理器核心芯片供電,而無需通過電阻較高的正面。這可以放寬對高級 IC 系統電源的要求,該系統越來越受到功率密度、縮放晶體管的較低電源電壓(因此,更大的電流)以及激進的 IR 壓降的挑戰。我們的一位合作伙伴最近宣布,它將在其未來的技術節點芯片之一中實施 BSPDN 概念。

我們現在可以設想一個多核處理器,它由一個內存緩存晶片組成,堆疊在一個先進的微處理器核心邏輯晶片的頂部,使用細間距晶片對晶片鍵合。電源通過 BSPDN 直接提供給核心邏輯晶體管。這種邏輯存儲器結構隨后可以堆疊到包含內部和外部互連的第三個芯片上——使用舊的技術節點進行優化。”

我們在實現后端供電網絡方面取得了哪些進展?

“為了實現 BSPDN,需要一種專用的晶圓減薄工藝(低至幾 100 納米),以及處理將器件晶圓背面電連接到正面的納米硅通孔 (n-TSV) 的能力。 . n-TSV 可以降落在第一個正面金屬上,也可以降落在晶圓正面的埋入式電源軌 (BPR) 上。

Imec 在其 3D 集成計劃的框架內開發這些流程。我們所謂的 n-TSV-last 方法包括使用低溫晶圓對晶圓鍵合技術將第一個晶圓(包括晶體管)的“有源”正面鍵合到第二個載體晶圓。第一個晶圓的背面被減薄,通過n-TSV圖案化和鎢填充以及背面金屬化完成該工藝。

其中一個挑戰與晶圓鍵合工藝有關,該工藝固有地會引起第一片晶圓的變形。這對圖案化 n-TSV 所需的背面光刻步驟提出了挑戰,尤其是達到與邏輯標準單元結構相匹配的所需對準精度的能力。Imec 及其合作伙伴開發了替代方法,以實現更好的疊加精度并改進 BSPDN。”

您能否詳細介紹一下imec 的3D 集成技術對行業的附加價值?

“今天,一些商業 '3D' 產品使用 TSV 和 Sn 微凸塊的組合來實現異構裸片到裸片或裸片到中介層堆疊。雖然研究顯示 TSV 微縮的良好前景,但生產中最先進的 Sn 微凸塊間距在約 30μm 時已飽和。問題在于互連間隙:芯片到芯片的微凸塊連接還沒有趕上可以充分利用 TSV 的程度。

在imec,我們正在突破今天可能的界限。我們已經展示了一種基于 Sn 的微凸塊互連方法(在凸塊金屬化下使用大馬士革)產生低至 7μm 的互連間距,并制定了將該間距降至 5μm 的路線圖。

通過使用我們的 Cu/SiCN 芯片到晶圓混合鍵合方法,我們可以進一步減小互連間距(低至 3μm)。按照這種方法,芯片使用電介質對電介質鍵合方法堆疊,然后是金屬對金屬連接——不使用微凸塊。最大的挑戰與芯片放置在晶圓上的純度和精度有關。

使用我們的晶圓對晶圓鍵合解決方案可以獲得最高的互連密度。這些發展是由邏輯存儲器堆疊驅動的,需要遠低于 1μm 的互連間距。今天,我們獲得了 700nm 間距,并希望將其降低到前所未有的 500nm。”

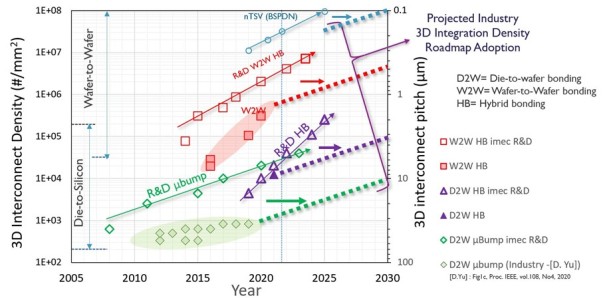

3D 互連 imec 研發路線圖

是什么讓 imec 的 3D 系統集成計劃在全球半導體行業中獨樹一幟?

“Imec 提出了不同 3D 集成技術的行業路線圖,其 3D 互連密度的范圍接近 8 個數量級。這些 3D 集成技術中的每一種都滿足不同的需求,因此針對不同的終端應用,例如智能手機、DRAM 芯片或高性能計算系統。最佳選擇是在層次驅動的 3D 互連密度和最終解決方案的成本之間進行權衡。

為了在系統級別獲得盡可能多的好處,我們不斷突破各種選項的界限。為此,我們與我們的設備、計量和材料供應商密切合作,并得到 EDA 軟件開發商和針對不同終端應用的公司的支持。這種獨特的合作伙伴生態系統使我們能夠加速真正的 3D SOC 的開發,并在系統級別獲得最佳的 PPAC 增益。

審核編輯 黃昊宇

-

芯片

+關注

關注

463文章

54223瀏覽量

468090 -

3D

+關注

關注

9文章

3016瀏覽量

115392

發布評論請先 登錄

常見3D打印材料介紹及應用場景分析

探索TLE493D-P3XX-MS2GO 3D 2Go套件:開啟3D磁傳感器評估之旅

京東11.11直播技術全面升級,立影3D技術、JoyAI大模型重構沉浸式購物體驗

技術資訊 I 圖文詳解 Allegro X PCB Designer 中的 3D 模型映射

玩轉 KiCad 3D模型的使用

iTOF技術,多樣化的3D視覺應用

索尼與VAST達成3D業務合作

多芯粒2.5D/3D集成技術研究現狀

對 3D 技術前景的看法

對 3D 技術前景的看法

評論