隨著雷達(dá)和無線通信系統(tǒng)中的信號(hào)處理從模擬轉(zhuǎn)向數(shù)字,人們?cè)陂_發(fā)先進(jìn)的波束成形技術(shù)以實(shí)現(xiàn)新應(yīng)用方面付出了巨大的努力。使用數(shù)字方法精確引導(dǎo)波束的能力,最常見的是快速傅里葉變換 (FFT),導(dǎo)致雷達(dá)和移動(dòng)電信系統(tǒng)的設(shè)計(jì)方式發(fā)生了重大變化。

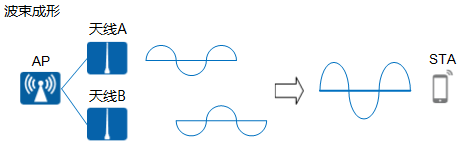

波束成形可以切換或自適應(yīng)。例如,在切換波束成形中,移動(dòng)電信基站從預(yù)先定義的波束選擇中進(jìn)行選擇,每個(gè)波束都基于接收到的信號(hào)的強(qiáng)度以特定方向?yàn)槟繕?biāo)。當(dāng)用戶相對(duì)于天線陣列移動(dòng)時(shí),信號(hào)被切換到陣列中的其他元件,這些元件定位得更好,以在特定方向上提供更強(qiáng)的信號(hào)。另一方面,自適應(yīng)波束形成依賴于實(shí)時(shí)計(jì)算,允許基站在目標(biāo)用戶的方向上發(fā)射更多聚焦的波束,同時(shí)減少其他方向的輸出,從而大大減少元素之間的干擾。

自適應(yīng)波束成形設(shè)計(jì)需要非常高的處理帶寬——每秒必須執(zhí)行數(shù)十億次乘法和累加操作。因此,接收系統(tǒng)抑制噪聲源和干擾變得更加重要。同時(shí),必須保持對(duì)天線陣列中每個(gè)元件的實(shí)時(shí)方向控制。為了實(shí)現(xiàn)這一點(diǎn),有必要對(duì)每個(gè)天線元件接收到的信號(hào)進(jìn)行數(shù)字化處理,同時(shí)使用元件級(jí)處理。由于需要繁重的計(jì)算負(fù)載,傳統(tǒng)的 CPU 和 DSP 在自適應(yīng)波束成形應(yīng)用中可能會(huì)迅速負(fù)擔(dān)過重。然而,性能更高的 FPGA 非常適合該任務(wù),因?yàn)樗鼈兙哂?a target="_blank">嵌入式 DSP 模塊、并行處理架構(gòu)和增強(qiáng)的存儲(chǔ)器功能。

全球?qū)σ苿?dòng)寬帶數(shù)據(jù)和語音服務(wù)不斷增長的需求不斷推動(dòng)無線網(wǎng)絡(luò)運(yùn)營商擴(kuò)展和升級(jí)其網(wǎng)絡(luò)以提供更多容量。運(yùn)營商同時(shí)試圖最大限度地增加每個(gè)無線基站可以支持的用戶數(shù)量,以降低其基礎(chǔ)設(shè)施成本,同時(shí)保持對(duì)用戶有吸引力的價(jià)格點(diǎn)。

由于可用無線頻譜的數(shù)量有限,這項(xiàng)工作變得復(fù)雜,因此增加的流量會(huì)產(chǎn)生更多的干擾,通話質(zhì)量也會(huì)受到影響,部分原因是天線技術(shù)的限制。全向天線通常用于在蜂窩塔上進(jìn)行發(fā)送和接收。然而,這種傳統(tǒng)方法(其中天線充當(dāng)傳感器,將電磁能轉(zhuǎn)換為電能)效率不高,并且由于單個(gè)塔上存在大量信號(hào)而受到高度干擾,從而降低了整體連接性。

這種干擾可以通過使用在同一塔上組合在一起的定向扇區(qū)天線來減輕。這些自適應(yīng)陣列天線或智能天線已越來越多地用于電信網(wǎng)絡(luò),以提高無線連接質(zhì)量并提高整體容量。這是通過波束成形技術(shù)實(shí)現(xiàn)的,該技術(shù)通過使用先進(jìn)的數(shù)字信號(hào)處理將來自基站的波束引導(dǎo)至各個(gè)用戶。波束成形調(diào)整每個(gè)傳入和傳出信號(hào)的功率和相位,以創(chuàng)建沿特定方向傳播的波束,同時(shí)減少非必要輸出。這減少了單個(gè)信號(hào)對(duì)彼此造成的干擾量,并提高了所有連接的質(zhì)量。

創(chuàng)新的自適應(yīng)波束形成算法的出現(xiàn)導(dǎo)致在信號(hào)處理中使用浮點(diǎn)算法的增加,以通過實(shí)現(xiàn)實(shí)時(shí)目標(biāo)跟蹤來最大限度地減少干擾并提高雷達(dá)容量。這是通過使用 QR 分解 (QRD) 和權(quán)重反向替換 (WBS) 等算法同時(shí)創(chuàng)建多個(gè)點(diǎn)光束來實(shí)現(xiàn)的。這些算法有助于波束的自適應(yīng)形成,同時(shí)減少噪聲和干擾,但它們每秒需要大量的浮點(diǎn)運(yùn)算。

由于許多雷達(dá)系統(tǒng)的尺寸、重量和功率限制,使用傳統(tǒng) CPU 或 GPU 選項(xiàng)并不是最佳方法,因?yàn)閳?zhí)行浮點(diǎn)計(jì)算所需的硬件數(shù)量增加。由于需要更多的內(nèi)存、功率和空間,更不用說更高的成本、更復(fù)雜的系統(tǒng)設(shè)計(jì)和延長的集成時(shí)間,因此使用多個(gè) CPU 對(duì)雷達(dá)系統(tǒng)的設(shè)計(jì)產(chǎn)生了重大影響。基于 CPU 的設(shè)計(jì)進(jìn)一步受到有限的內(nèi)存和接口選項(xiàng)的限制。

FPGA 在采用先進(jìn)數(shù)字波束形成技術(shù)的雷達(dá)系統(tǒng)中提供了優(yōu)于 CPU 和 GPU 選項(xiàng)的巨大優(yōu)勢,因?yàn)樗鼈兛梢越档统杀尽?fù)雜性、功耗和上市時(shí)間。由于其在自適應(yīng)波束成形應(yīng)用中處理高度并行浮點(diǎn)運(yùn)算的卓越能力,F(xiàn)PGA 可以提高算法性能,同時(shí)顯著降低功耗。

FPGA 也更高效,因?yàn)橐粋€(gè)設(shè)備通過諸如 PCIe 和 Serial RapidIO 等 I/O 標(biāo)準(zhǔn)從天線陣列中每個(gè)元件捕獲的信號(hào)中接收和處理大量數(shù)據(jù)。除了提供更高性能的處理之外,這樣的系統(tǒng)還不需要安裝在需要超過 1,000 W 的 VPX 機(jī)箱中的大量耗電的多核 CPU 板。流線型的單 FPGA 設(shè)計(jì)還受益于外部存儲(chǔ)器和其他額外的單塊電路板上提供的功能小于 80 W。

智能天線和自適應(yīng)波束成形的使用,雖然幾十年來在軍事和國防應(yīng)用中很常見,但由于與廣泛部署相關(guān)的高昂成本,直到最近才在商業(yè)蜂窩網(wǎng)絡(luò)中廣泛使用。隨著高性能、低成本 FPGA 和 DSP 的興起,自適應(yīng)波束成形在 2000 年代初進(jìn)入了 3G 移動(dòng)基礎(chǔ)設(shè)施,該技術(shù)現(xiàn)在被廣泛用于擴(kuò)展 4G 網(wǎng)絡(luò)。這為硬件和固件設(shè)計(jì)人員提供了新的機(jī)會(huì),可以改進(jìn)用于國防和商業(yè)應(yīng)用的波束成形方法。

審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1660文章

22412瀏覽量

636309 -

cpu

+關(guān)注

關(guān)注

68文章

11279瀏覽量

224987 -

gpu

+關(guān)注

關(guān)注

28文章

5194瀏覽量

135450

發(fā)布評(píng)論請(qǐng)先 登錄

AI波束管理測試系統(tǒng)和信道模型簡化實(shí)現(xiàn)方案

AMD 推出第二代 Kintex UltraScale+ 中端FPGA,助力智能高性能系統(tǒng)

AMD UltraScale架構(gòu):高性能FPGA與SoC的技術(shù)剖析

基于DSP與FPGA異構(gòu)架構(gòu)的高性能伺服控制系統(tǒng)設(shè)計(jì)

波束成形技術(shù):從原理到實(shí)踐,如何精準(zhǔn)控制無線信號(hào)方向?

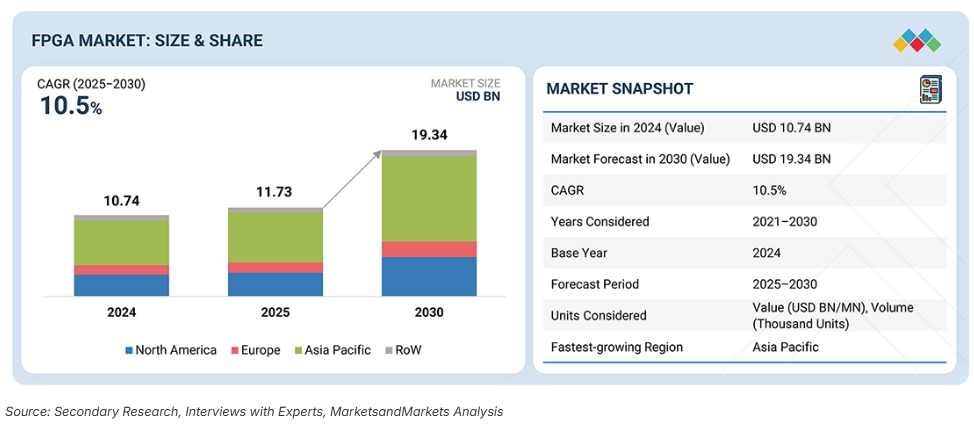

MarketsandMarkets FPGA行業(yè)報(bào)告,2026~2030 FPGA市場洞察

Altera Agilex 3 FPGA和SoC產(chǎn)品家族的性能分析

ASP4644芯片在雷達(dá)FPGA供電系統(tǒng)中的適配與性能分析

25年11月上海FPGA算法實(shí)現(xiàn)與應(yīng)用技術(shù)高級(jí)研修分享

信號(hào)發(fā)生器如何與波束賦形算法配合優(yōu)化?

A-59P 多功能語音處理模組:性能卓越,便捷易用?

相控陣波束賦形芯片對(duì)衛(wèi)星通信的必要性

波束賦形技術(shù)的優(yōu)勢和應(yīng)用場景

Altera Agilex 5 D系列FPGA的性能和能效

FPGA是什么?應(yīng)用領(lǐng)域、差分晶振作用及常用頻率全面解析

FPGA可以提供更好的波束賦形性能

FPGA可以提供更好的波束賦形性能

評(píng)論