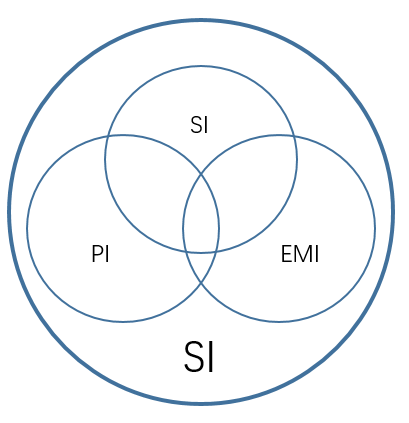

先說(shuō)一下,信號(hào)完整性為什么寫(xiě)電源完整性?SI 只是針對(duì)高速信號(hào)的部分,這樣的理解沒(méi)有問(wèn)題。如果提高認(rèn)知,將SI 以大類(lèi)來(lái)看,SI&PI&EMI 三者的關(guān)系:

所以,基礎(chǔ)知識(shí)系列里還是得講講電源完整性。話(huà)不多說(shuō),直接上圖:

01

區(qū)別

記得剛接觸信號(hào)完整性的時(shí)候,對(duì)電源完整性(PI)和電源工程師之間的關(guān)系是分不清的。后來(lái)才漸漸了解這里面的千差萬(wàn)別。簡(jiǎn)單來(lái)說(shuō),電源的產(chǎn)生與轉(zhuǎn)化,比如Buck電路,LDO,DC-DC等,源端部分這些是電源工程師來(lái)確定的。

電源工程師也會(huì)進(jìn)行相關(guān)的電源可靠性設(shè)計(jì)與測(cè)試,比如耐壓余量,耐電流余量,保護(hù)設(shè)計(jì)(過(guò)壓、過(guò)溫、過(guò)流等)。這些工作是電源工程師的專(zhuān)業(yè)范疇。電源這一塊很復(fù)雜,光各種拓?fù)浣Y(jié)構(gòu)就已經(jīng)讓人云里霧里了,絕對(duì)是可以深究的一份職業(yè)。

02

PDN

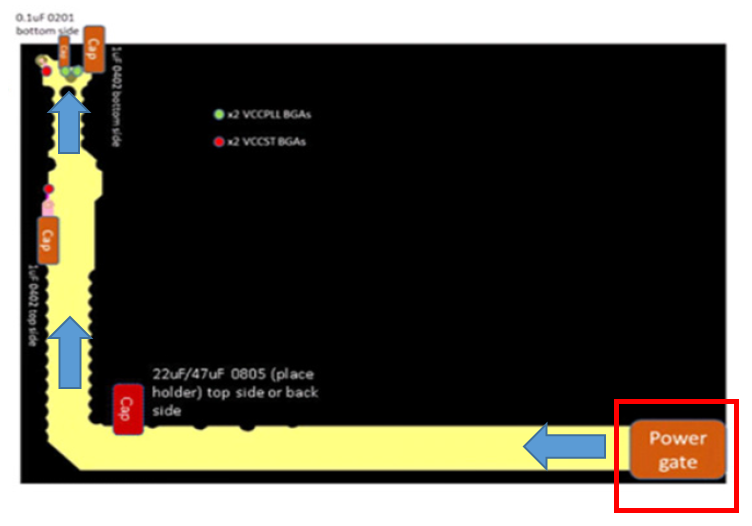

電源完整性(PI)更關(guān)注于電源路徑及終端,也就是電源分配網(wǎng)絡(luò)(PDN)。從源端穩(wěn)壓模塊(VRM)經(jīng)過(guò)路徑(單層直達(dá)或過(guò)孔轉(zhuǎn)換的幾個(gè)層面),到達(dá)終端,最終流向使用芯片或經(jīng)過(guò)線纜到使用設(shè)備。

電源路徑與信號(hào)路徑是有區(qū)別的,電源分配網(wǎng)絡(luò)中一個(gè)電源路徑可以在一個(gè)節(jié)點(diǎn)分成多個(gè)路徑,或者說(shuō)轉(zhuǎn)換成多個(gè)電源,終端掛多個(gè)元器件,可以理解為一對(duì)多。而信號(hào)路徑只能一對(duì)一。

既然電源分配網(wǎng)絡(luò)是為終端設(shè)備提供所需電源,那就是有要求,就需要對(duì)電源分配網(wǎng)絡(luò)管控。如信號(hào)路徑,除了保證返回電流,還要盡量保證返回路徑的低阻抗。由于是一對(duì)多的情況,這樣的管控,才能保證返回電流不相互重疊,不會(huì)發(fā)生地彈,即盡量避免開(kāi)關(guān)噪聲(SSN)。

基本要求是,保證供電電壓穩(wěn)定,至少能夠維持在一個(gè)很小的容差范圍內(nèi),通常在+/-5%以?xún)?nèi)。電源的測(cè)試中有紋波測(cè)試,這個(gè)紋波測(cè)試標(biāo)準(zhǔn)就是+/-5%。

講到返回電流,這里就要分為直流部分和交流部分。

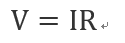

直流部分:

終端設(shè)備需要穩(wěn)定的電壓輸出,電源分配網(wǎng)絡(luò)互連之間串聯(lián)電阻的存在,直流部分通過(guò),就會(huì)產(chǎn)生壓降,通常稱(chēng)為IR 壓降。當(dāng)電流發(fā)生波動(dòng)時(shí),壓降也會(huì)隨之波動(dòng),從而影響終端設(shè)備的識(shí)別。之前的USB設(shè)備好像最低電壓值4.75 V。

交流部分:

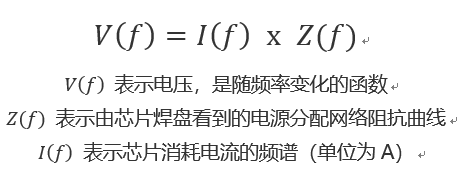

當(dāng)交流電流通過(guò)電源路徑時(shí),電源分配網(wǎng)絡(luò)上也將產(chǎn)生電壓降,這個(gè)壓降會(huì)隨著頻率發(fā)生變化:

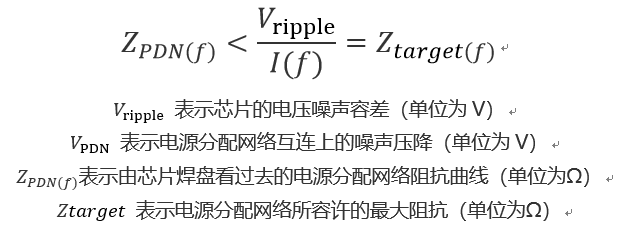

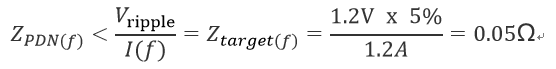

電源路徑的不同(層數(shù)&Shape寬度等),造成的壓降變化是不同的,輸出穩(wěn)定電壓到終端的難度很大,我們所要做的只是保證電壓的變化在一定的范圍之內(nèi),也就是所謂的噪聲容差。上式就可能轉(zhuǎn)換為目標(biāo)阻抗:

既然保證不了路徑上電壓的穩(wěn)定,那么電源分配網(wǎng)絡(luò)的電流在波動(dòng)的情況下,就需要保持電源分配網(wǎng)絡(luò)阻抗低于目標(biāo)阻抗。

需要注意的是,即使同一個(gè)電源芯片或模塊,針對(duì)不同的產(chǎn)品,也會(huì)給出不同的標(biāo)準(zhǔn)。即使相同的標(biāo)準(zhǔn),因?yàn)椴煌碾娫绰窂剑煌陌鎴D走線,也會(huì)有千差萬(wàn)別。所以,電源分配網(wǎng)絡(luò)目標(biāo)阻抗才是最基本的要求。

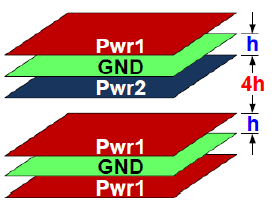

目標(biāo)阻抗的管控說(shuō)到底就是路徑管控。兩個(gè)因素:電源和地平面之間介質(zhì)盡量薄,盡量短而寬的走線。

03

電源樹(shù)(Power tree)

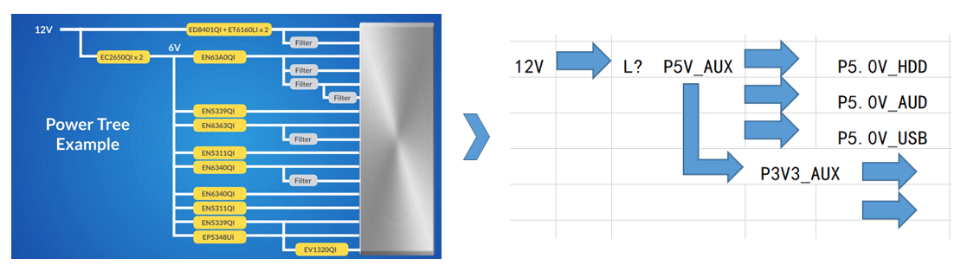

先期評(píng)估,確認(rèn)各個(gè)電所需層面和路徑的時(shí)候,我們會(huì)預(yù)先根據(jù)相關(guān)規(guī)范或標(biāo)準(zhǔn),制定一個(gè)電源樹(shù)(Power tree)。個(gè)人覺(jué)得電源樹(shù)的概念提的特別好。一個(gè)主干道有很多分支,分支上再有分叉,一直到末端。

電源分配網(wǎng)絡(luò)可以有很多分支,也就是說(shuō)路徑上可以?huà)旌芏嘣O(shè)備,比如5V電源下掛HDD,USB設(shè)備等。

電源的分類(lèi)

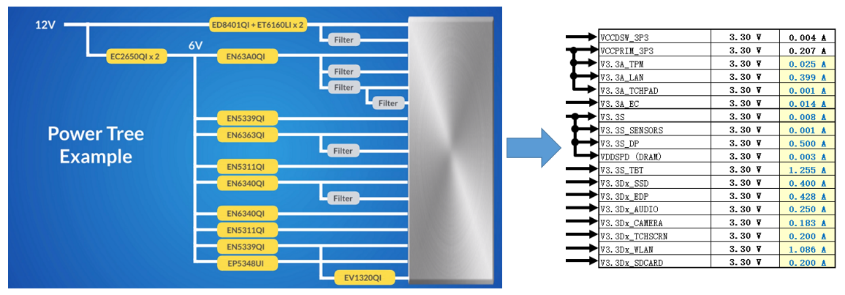

比如12 V的電轉(zhuǎn)出5V,5V總電分出分支,給到各種設(shè)備。5V經(jīng)過(guò)LDO轉(zhuǎn)換電路出3.3V電,,3.3V總電分出分支,再往下繼續(xù)……

同時(shí)列出各個(gè)分支所需電流的多少,為后面路徑規(guī)劃(所需電源Shape大小給出標(biāo)準(zhǔn)),同時(shí)給出對(duì)應(yīng)的層面及評(píng)估。

在做電源路徑規(guī)劃,建議先做電源樹(shù)Power Tree,對(duì)所做設(shè)計(jì)的終端設(shè)備所需電壓路徑及所需電流大小一一評(píng)估,產(chǎn)品的不同,有的產(chǎn)品可能會(huì)使用幾十種電壓值。檢查的時(shí)候,建議從終端往前反推,這樣保證沒(méi)有遺漏。

04

頻段管控

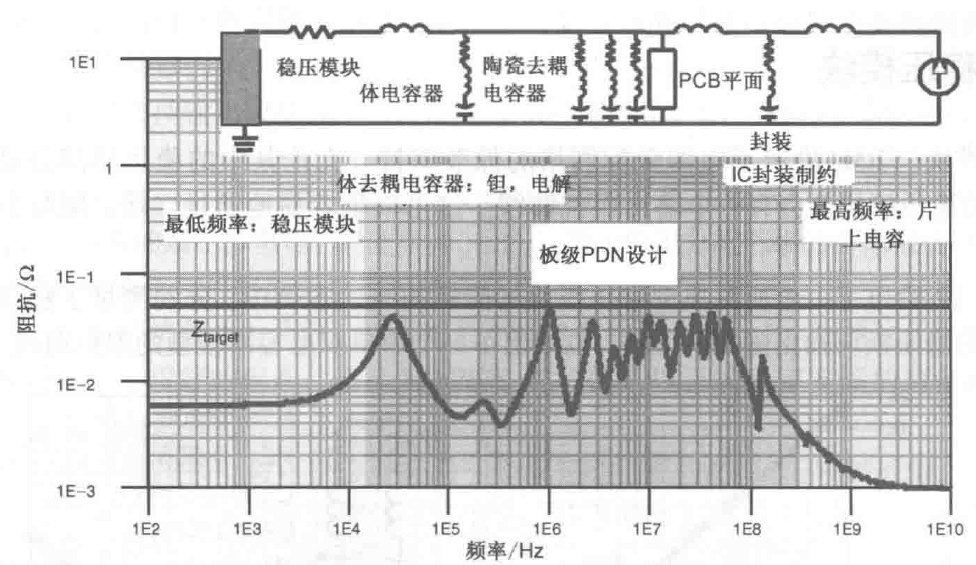

上面提到一款產(chǎn)品,有幾十種電壓,每個(gè)電壓的目標(biāo)阻抗隨著頻率是改變的,這個(gè)時(shí)候就需要對(duì)路徑進(jìn)行頻段分類(lèi):

片選電容

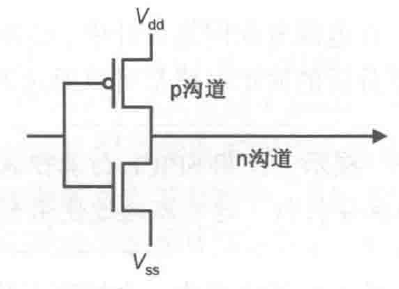

芯片是由晶體管組成,不管是P溝道還是n溝道導(dǎo)通,都會(huì)形成柵極電容,隨著制程工藝的提升,溝道長(zhǎng)度變短,單位面積電容增大。所以,高頻時(shí),片上電容為電源分配網(wǎng)絡(luò)提供了低阻抗。

穩(wěn)壓模塊

穩(wěn)壓模塊( VRM)決定了電源分配網(wǎng)絡(luò)的低頻阻抗。穩(wěn)壓模塊是為了保證輸出阻抗低頻的阻抗曲線。

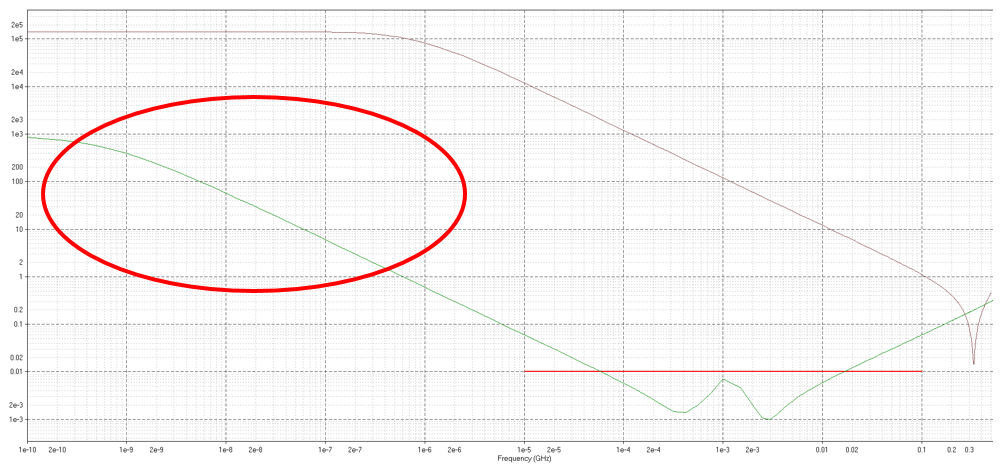

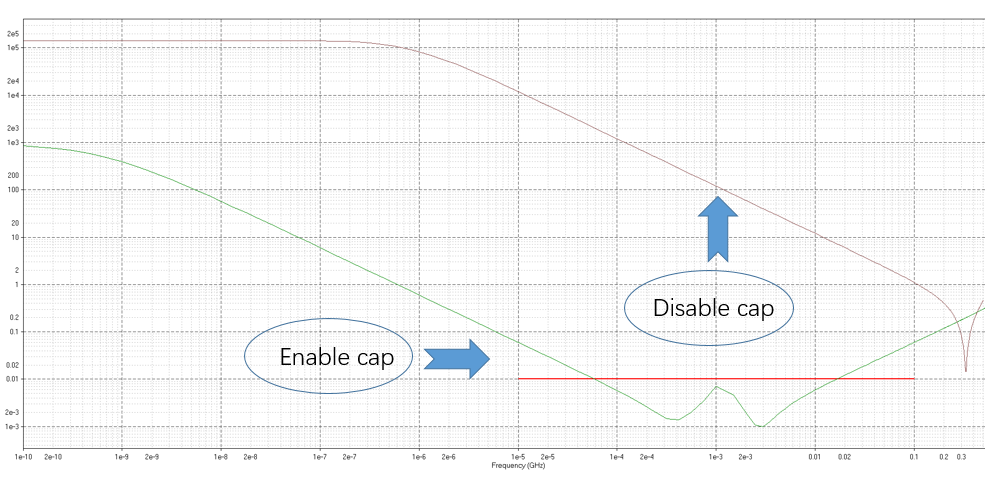

實(shí)際中VRM沒(méi)有相關(guān)模型,所以我們仿真的曲線見(jiàn)下圖。所以在低頻(10K以下)阻抗反而很高。

PCB板級(jí)

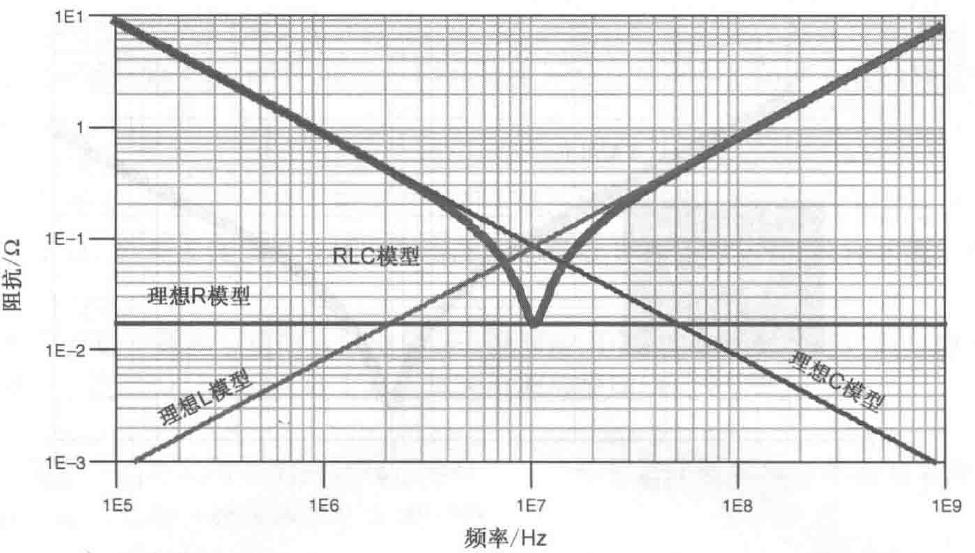

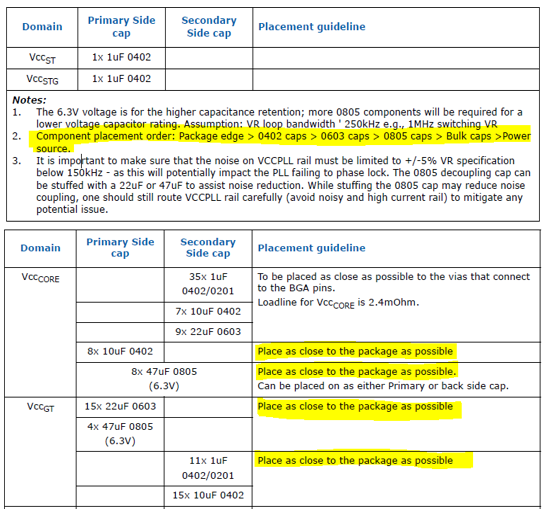

為了確定板級(jí)電源分配網(wǎng)絡(luò)的設(shè)計(jì)目標(biāo)阻抗,可以先找出上限頻率,即找出PCB板的阻抗開(kāi)始超過(guò)目標(biāo)阻抗時(shí)的頻率點(diǎn)。如果要整個(gè)單獨(dú)分析,會(huì)比較麻煩。在低頻時(shí),RLC 電路的阻抗取決于理想電容,在高頻時(shí)則取決于理想電感。而理想電阻則決定了 RLC 的最低阻抗。

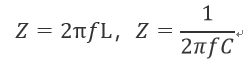

簡(jiǎn)單點(diǎn),分為電感和電容的兩個(gè)部分。相關(guān)公式為:

注意其和截止頻率公式區(qū)分。

電感方面考慮封裝引腳、過(guò)孔和擴(kuò)散電感等共同作用。

封裝引腳是串聯(lián)在芯片焊盤(pán)到電路板焊盤(pán)之間,可能有數(shù)百個(gè)電源/地平面對(duì),開(kāi)關(guān)數(shù)量的不同,封裝引腳電感是變化的,一般不超過(guò)1 nH。還有過(guò)孔及電源/地平面上運(yùn)送電流過(guò)程中的擴(kuò)散電感,共同決定了回路電感。

當(dāng)然,這里面過(guò)孔與過(guò)孔之間,平面之間,表層傳輸線之間等,這些情況的回路電感,這里就不做展開(kāi)。

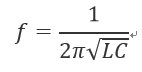

電容方面從擺放位置、電容容值&個(gè)數(shù)、反諧振三個(gè)方面來(lái)說(shuō)。不同的容值,不同封裝,耦合半徑的不同,所以擺放的位置需要考慮。還有,電容器的相關(guān)組合,擺放位置都是盡量靠近封裝,那是因?yàn)殡娏髦丿B,擴(kuò)散電感增加,電容器擺放可以減小增加量。

所以,電容器組合對(duì)電源分配網(wǎng)絡(luò)阻抗曲線的影響,在很大程度上取決于擺放在PCB板上位置。

電容除了擺放位置還要分為容值相同和容值不同的兩種情況。在通常的板級(jí)應(yīng)用中,使用較少個(gè)數(shù)的不同容值的電容器(而不是使用相同容值的電容器)往往能使阻抗最低的原因。為了使電容器的個(gè)數(shù)最少 ,一般選擇不同的容值。

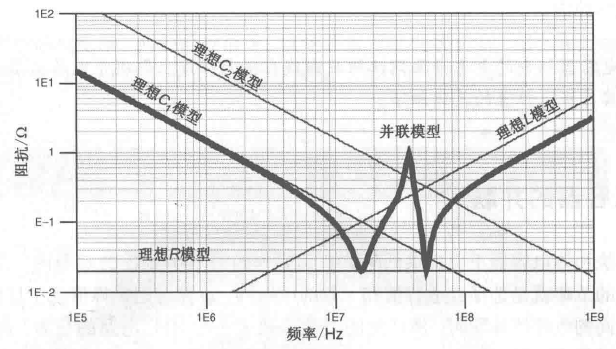

選擇不同容值的電容器,還有一個(gè)原因:反諧振。容值的不同,自諧振頻率也不同,電容之間的并聯(lián),讓其之間有一個(gè)新的特性,即阻抗的峰值,稱(chēng)為并聯(lián)諧振峰值,它發(fā)生在并聯(lián)諧振頻率( Parallel Resonant Frequency, PRF)處。這時(shí)候就需要添加一個(gè)其自諧振頻率介于它們之間的電容器加以降低。

需要注意的是,當(dāng)需要采用多個(gè)電容并聯(lián)來(lái)滿(mǎn)足容值要求時(shí),最好采用同類(lèi)型的電容進(jìn)行并聯(lián)。這里的同類(lèi)型是指封裝。

板級(jí)電源分配網(wǎng)絡(luò)設(shè)計(jì)的頻率范圍約從 100 kHz 到 100 MHz。這正是電路板平面和多層陶瓷貼片電容器( MLCC) 發(fā)揮作用的頻率范圍 。這也是仿真時(shí),重點(diǎn)關(guān)注的頻率范圍。

本例以1.2V的CPU用電為例,來(lái)舉例說(shuō)明PDN阻抗仿真。紋波百分比5%,最大電流為1.2A,根據(jù)公式

上圖說(shuō)明,是否使能電容對(duì)PDN阻抗的影響很大。

05

總結(jié)

在電源樹(shù)里,我們給出的都是產(chǎn)品規(guī)格或者設(shè)計(jì)規(guī)范里給出的峰值電流,實(shí)際的應(yīng)用中,這種情況出現(xiàn)的機(jī)率很小。所以,消費(fèi)類(lèi)產(chǎn)品,在成本的管控之下,會(huì)給出不同配置的產(chǎn)品。低配版本,這時(shí)候,會(huì)減小MLCC的使用種類(lèi)和數(shù)量,OptimizePI是一項(xiàng)很重要的工作,這個(gè)后面有機(jī)會(huì)再講。通過(guò)優(yōu)化,來(lái)降低產(chǎn)品成本,這也是電源完整性的關(guān)鍵所在。

審核編輯 :李倩

-

電源

+關(guān)注

關(guān)注

185文章

18930瀏覽量

264231 -

阻抗

+關(guān)注

關(guān)注

17文章

990瀏覽量

49439 -

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1490瀏覽量

98205

原文標(biāo)題:電源完整性基礎(chǔ)知識(shí)

文章出處:【微信號(hào):mcu168,微信公眾號(hào):硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

IDT信號(hào)完整性產(chǎn)品:解決高速信號(hào)傳輸難題

SI合集002|信號(hào)完整性測(cè)量應(yīng)用簡(jiǎn)介,快速掌握關(guān)鍵點(diǎn)

使用MATLAB和Simulink進(jìn)行信號(hào)完整性分析

Cadence工具如何解決芯粒設(shè)計(jì)中的信號(hào)完整性挑戰(zhàn)

串?dāng)_如何影響信號(hào)完整性和EMI

了解信號(hào)完整性的基本原理

Samtec虎家大咖說(shuō) | 淺談信號(hào)完整性以及電源完整性

電源完整性基礎(chǔ)知識(shí)

各種常用電路模塊設(shè)計(jì)原則:電源完整性

受控阻抗布線技術(shù)確保信號(hào)完整性

信號(hào)完整性測(cè)試基礎(chǔ)知識(shí)

電源完整性分析及其應(yīng)用

普源DHO3000系列示波器電源完整性測(cè)試

技術(shù)資訊 | 信號(hào)完整性測(cè)試基礎(chǔ)知識(shí)

信號(hào)完整性為什么寫(xiě)電源完整性?

信號(hào)完整性為什么寫(xiě)電源完整性?

評(píng)論