PCIe(Peripheral Component Interconnect express)作為一種在芯片和系統內快速移動數據的方法已經存在了一段時間。

要檢查它的起源,必須一直追溯到 1991 年,從英特爾的本地總線 PCI 標準開始。PCI 插槽首先出現在服務器中,后來進入臺式機,十年來一直是臺式機擴展卡的標準。隨著計算的發展,業界認識到需要創建一個標準來解決新的總線架構技術和多個芯片的內部連接。就這樣,PCIe 誕生了,并在 2003 年由 PCI-SIG(外圍組件互連特別興趣小組)領導,批準了 1.0 規范,提供了當時驚人的 2.5GT/s 數據速率。

PCIe 在包括固態驅動器、顯卡加速和網絡在內的各種用途中立足,不斷發展以滿足市場需求。PCIe 幾乎可以在每個現代計算系統中找到;不僅在最初開發 PCIe 的個人計算機和服務器中,而且在高端移動設備、物聯網設備、汽車、醫療設備等領域。

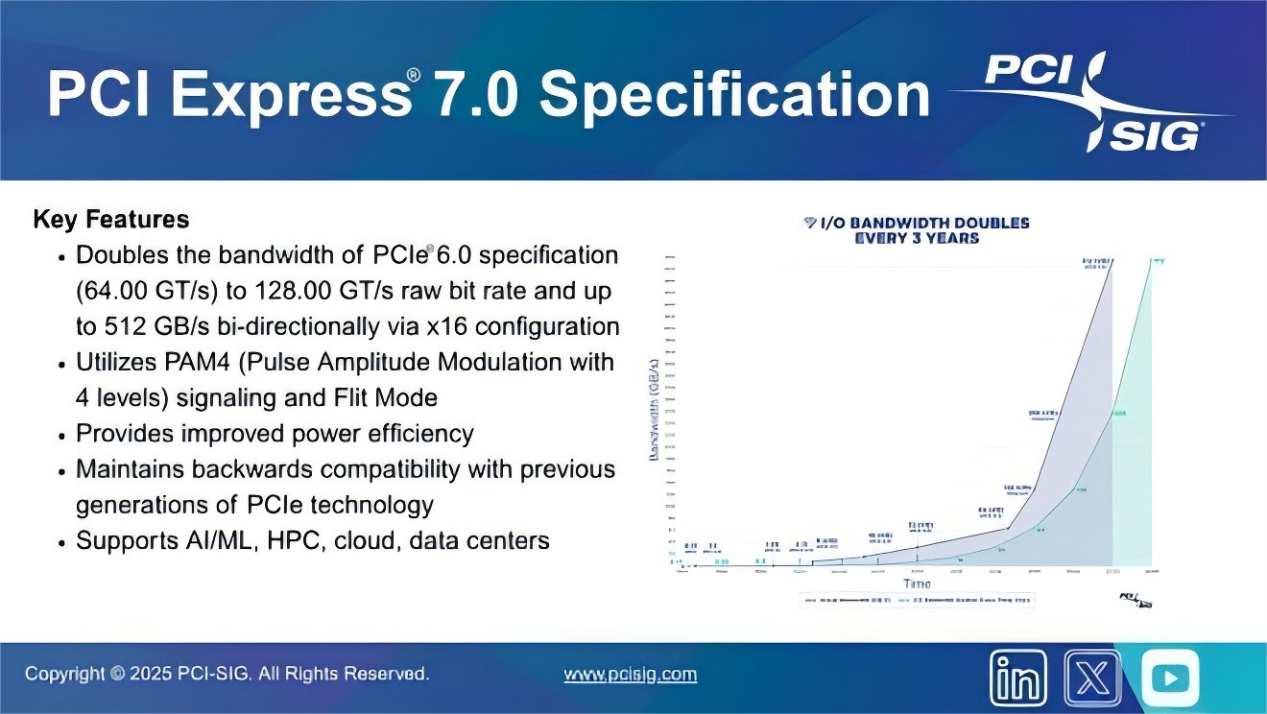

圖 1 顯示了規范隨時間的演變:

圖 1:PCIe 隨時間的演變

讓我們來看看 PCIe 6.0 規范以及它是如何從過去的規范演變而來的,以及為什么這對系統設計人員或芯片架構師在考慮他們的下一代設計時很重要。

首先,與每個新版本一樣,PCIe 6.0 將最大帶寬翻倍;這次是 64 GT/s。PCI-SIG 在規范過程的早期就認識到,自 PCIe 1.0 以來使用的 NRZ 信號編碼根本無法支持 PCIe 6 所需的 64GT/s 帶寬。因此,規范已過渡到 PAM4,這是一種允許承載在相同的時間內比特數的兩倍。然而,向 PAM4 信號編碼的過渡具有引入顯著更高的誤碼率 (BER) 的副作用。這促使采用前向糾錯 (FEC) 機制來降低較高的錯誤率。幸運的是,FEC 機制足夠輕量級,對延遲的影響最小。注意:雖然 PAM4 信令更容易出錯,

PCIe 6.0 還引入了 FLIT 模式,其中數據包被組織在固定大小的流控制單元中,而不是過去規范版本中的可變大小。引入 FLIT 模式的最初原因是糾錯需要處理固定大小的數據包。但是,FLIT 模式還簡化了控制器級別的數據管理,并帶來更高的帶寬效率、更低的延遲和更小的控制器占用空間。讓我們花一分鐘來解決帶寬效率問題:對于固定大小的數據包,不再需要物理層的數據包幀,每個數據包節省 4 字節。FLIT 編碼還消除了以前 PCIe 規范中的 128B/130B 編碼和 DLLP 開銷,從而顯著提高了 TLP 效率,尤其是對于較小的數據包。

雖然與前幾代相比,PCIe 6.0 的變化很大,但業界對其采用有著強大而廣泛的支持。PCIe 在每個現代計算架構中無處不在,您應該期望 PCIe 6.0 將在高性能計算和云計算空間、企業存儲和網絡空間以及新興應用程序(如 AI/機器學習和汽車。

審核編輯:郭婷

-

云計算

+關注

關注

39文章

8021瀏覽量

144379 -

PCIe

+關注

關注

16文章

1460瀏覽量

88404 -

機器學習

+關注

關注

66文章

8553瀏覽量

136934

發布評論請先 登錄

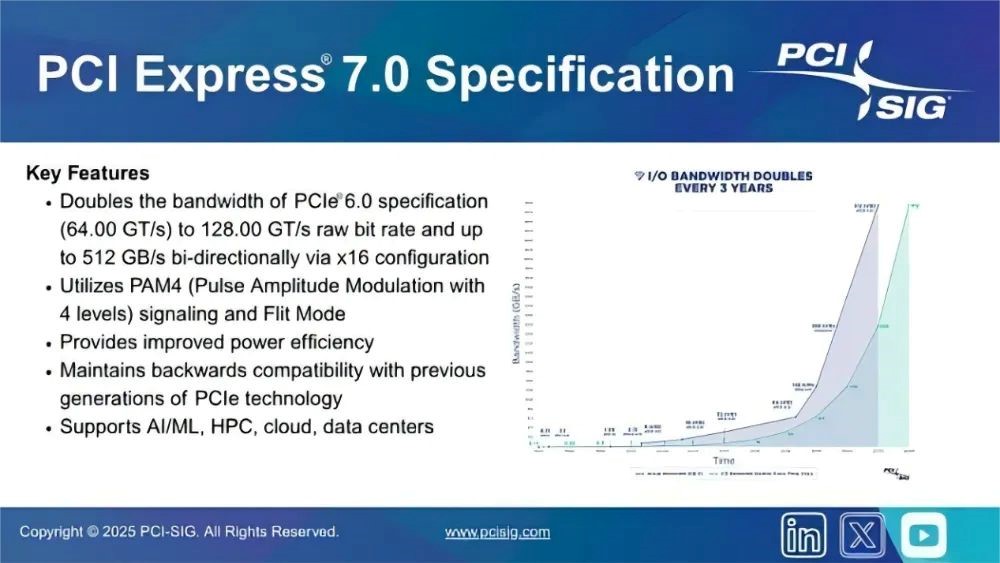

PCIe 7.0發布:16通道雙向512GB/s,擁抱光纖未來

電氣接線規范詳解

PCIe協議分析儀的核心功能與工作原理

PCIe 8.0規范開發更新!

風華電阻器命名規范解析

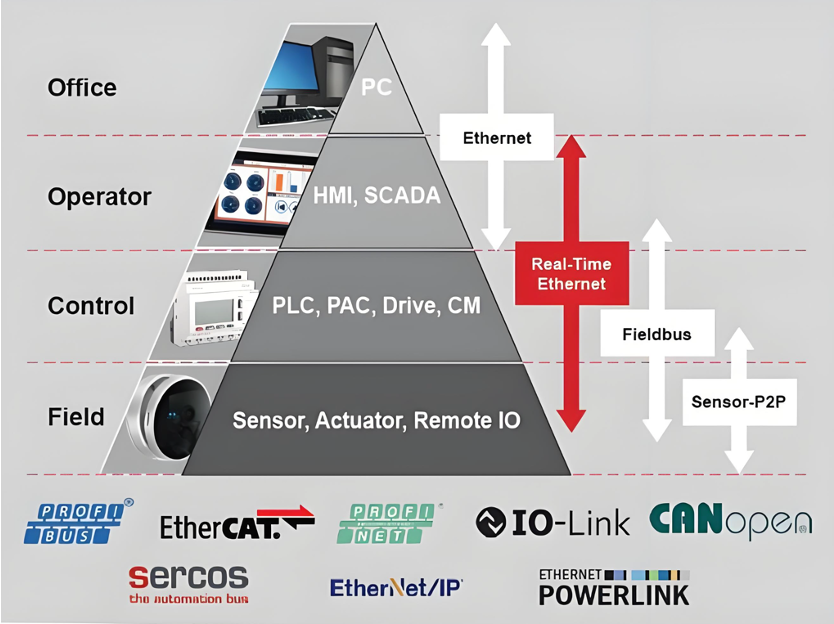

睿遠研究院丨IO-Link規范解讀(一):技術定義與組織規范

PCIe 6.0 SSD主控芯片狂飆!PCIe 7.0規范到來!

PCIe 8.0 規范公布:1TB/s 帶寬、256GT/s 速率

PCIe 4.0/5.0仍是主流!三家SSD企業搶灘高性能存儲市場,新品相繼亮相

為什么你拿著《規范》,卻不會“設計”?

133條原理圖設計規范checklist

Diodes公司PCIe 6.0時鐘緩沖器介紹

PCIe 6.0規范及它是如何從過去的規范演變而來的

PCIe 6.0規范及它是如何從過去的規范演變而來的

評論