摘要

隨著旨在解決現代算法加速工作負載的設備越來越多,就必須能夠在高速接口之間和整個器件中有效地移動高帶寬數據流。Achronix的Speedster7t獨立FPGA芯片可以通過集成全新的、高度創新的二維片上網絡(2D NoC)來處理這些高帶寬數據流。Achronix的FPGA中特有的2D NoC實現是一種創新,它與用可編程邏輯資源來實現2D NoC的傳統方法相比,有哪些創新和價值呢?本白皮書討論了這兩種實現2D NoC的方法,并提供了一個示例設計,以展示與軟2D NoC實現相比,Achronix 2D NoC是如何去提高性能、減少面積并縮短設計時間。

介紹

Achronix為其Speedster7t系列FPGA完全重新設計了片上通信架構,通過集成創新的2D NoC來適應高帶寬數據流的需求。在該FPGA器件的外圍,這個2D NoC連接到所有高速接口:包括多個400G以太網、PCIe Gen5、GDDR6和DDR4/5端口。在該FPGA內的可編程邏輯陣列上部署了一系列高速行和列通道,它們分別向FPGA可編程邏輯陣列的水平和垂直方向分配網絡流量。除了這些行和列之外,在NoC的每一行和每一列交叉的位置還有發送點和目標NoC訪問節點(NAP)。這些NAP充當NoC和位于可編程邏輯陣列中的資源之間的源或目的地。

為了將Achronix FPGA中內置的2D NoC,與使用傳統方法在可編程邏輯陣列中創建的NoC進行比較,為此我們評估了幾種軟NoC設計;最后,基于同行評審和FPGA結構的可移植性,我們選擇了米蘭理工學院的軟2D NoC(https://github.com/agalimberti/NoCRouter,2017)設計。這種軟NoC在單向網狀網絡(mesh)中實現了蟲洞前瞻預測切換。在實施時,它需要每個mesh節點上的多個存儲器來存儲和轉發流控制單元(flit)。

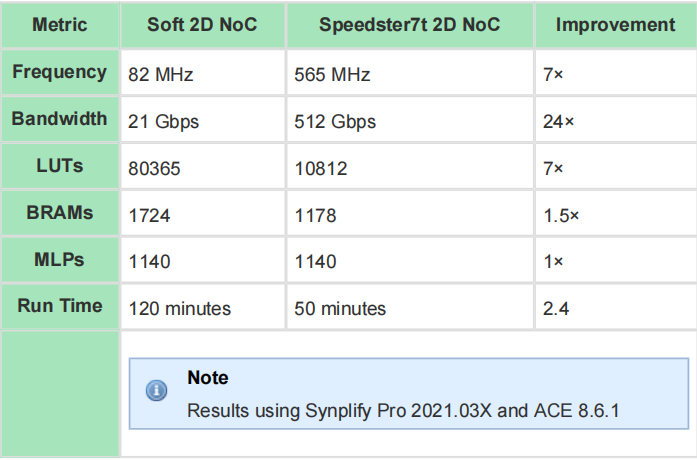

為了量化片上2D NoC實現模式和使用邏輯陣列資源的軟實現模式之間的差異,首先創建了一個實例化AlexNet 2D卷積的19個實例設計,然后在完整的2D NoC設計之間比較了三個主要指標:所需資源、設計性能和設計時間(創建設計的時間以及在工具中編譯設計的時間)。其結果是在所有三種情況下,集成Achronix 2D NoC的性能都明顯優于軟實現。

2D NoC減少使用的資源

為了比較兩種不同的2D NoC設計,兩種2D NoC都與現有的2D卷積(conv2d)設計相結合。conv2d設計對輸入圖像執行AlexNet 2D卷積。此conv2d設計需要一個或兩個AXI-4連接:一個用于從內存讀取,一個用于寫入內存,或者一個共享的AXI-4執行讀取和寫入。為了實現與軟NoC的最佳集成,選擇了單個共享AXI-4接口,conv2d模塊的實例位于每個mesh節點。然后,軟NoC啟用了GDDR6存儲接口的數據入口和出口——在軟NoC中,內存接口連接到第20個mesh節點上;而在內置式NoC中,這種連接已經存在。在整個設計中,從GDDR6到每個conv2d節點都存在節點到節點通信,但conv2d節點之間不通信。

Achronix 2D NoC的設計細節

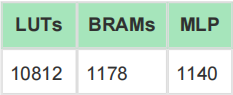

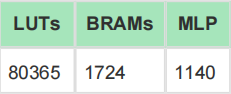

該設計有19個conv2d模塊實例,每個實例都訪問GDDR6存儲器。第20個實例是空閑的,因為GDDR6接口直接連接到集成的2D NoC。80個可用的NoC接入點(NAP)中有38個用于連接到conv2d實例。每個conv2d實例使用64個機器學習處理器(MLP),它在垂直方向覆蓋兩個NAP。由于這種部署是針對內置2D NoC,所以采用雙AXI-4方法連接conv2d模塊。下表列出了本設計中使用的資源。

表1:Achronix 2D NoC使用的資源

使用Achronix FPGA集成的2D NoC,可為設計布局產生了一種不凌亂的、可重復的結構,并且只消耗了不到一半的器件資源。下面是AC7t1500器件中資源使用的平面圖。

圖1:在AC7t1500中使用Achronix 2D NoC布局實例

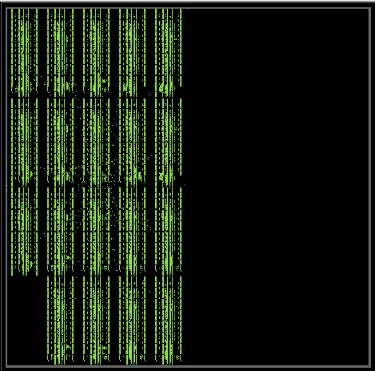

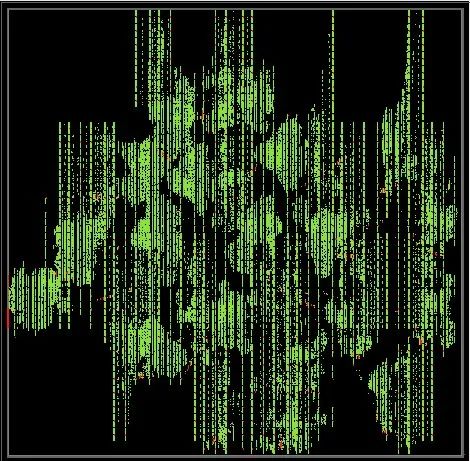

軟2D NoC的設計細節

該設計被配置為5 × 4規模mesh,具有19個conv2d模塊實例,每個實例都連接到一個軟NoC節點。其第20 mesh節點是為GDDR6接口預留的。因此,需要更多的邏輯資源來管理軟2D NoC結構。此實現還需要每個節點上的存儲,以便存儲flit并將其轉發到下一個節點。結果是顯著提高了資源的使用量,以及在器件上的不規則布局。下表列出了使用的資源;下圖為AC7t1500所用資源的平面圖。

表2:軟2D NoC使用的資源

圖2:使用軟2D NoC布局實例

2D NoC提高性能

如前所述,通過使用Achronix 2D NoC,conv2d設計產生了規則的資源布局,從而形成規則的布線。減少了邏輯資源使用就減少了擁塞,因為需要布線的邏輯更少。該解決方案實現了最高565 MHz的頻率,關鍵路徑包含在conv2d實例邏輯中。隨著更多conv2d節點添加到設計中,最大頻率不會降低。

下圖顯示了使用Achronix 2D NoC時產生的布線

圖3:使用Achronix 2D NoC的cnv2d設計布線

使用軟2D NoC解決方案會導致復雜且不規則的布線,同時時序也受到影響,因為需要深度LUT邏輯來選擇軟2D NoC中的適當路徑。

此外,性能會隨著mesh網絡大小的增加而降低。使用2 × 3 mesh的設計可以達到94 MHz,而5 × 4 mesh只能達到82 MHz。關鍵路徑包含在軟NoC mesh網絡中,而不是在conv2d邏輯中。如果花更多時間優化設計以提高性能,則可以進一步優化軟2D NoC的時序。

下圖顯示了使用軟2D NoC設計時生成的布線。

圖4:使用軟2D NoC時的cnv2d設計布線

2D NoC改善了帶寬

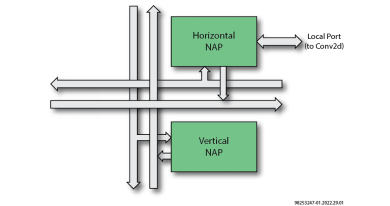

Achronix的2D NoC使用運行速度在2 GHz的256位雙向總線,每個conv2d實例連接到兩個NAP,從而在一個節點上與GDDR6接口之間的連接可實現的最大帶寬為512 Gbps。下面的框圖顯示了2D NoC和一個連接到本地conv2d實例的NAP的細節。

圖5:Achronix的2D NoC和NAP

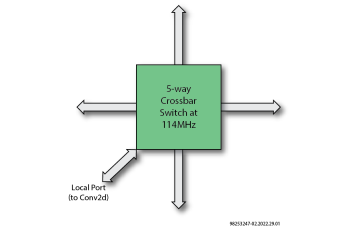

軟2D NoC使用五路交叉開關(crossbar switch),其中一個端口與本地conv2d實例通信,而其他端口與網格中的下一個節點通信。該解決方案可以實現節點到節點連接的頻率為82 MHz,從而在一個節點上形成最高為21 Gbps的GDDR6接口帶寬。下面的框圖顯示了軟2D NoC mesh中的一個交叉開關。

圖6:軟2D NoC交叉開關

2D NoC縮短了設計時間和工具運行時間

Achronix的2D NoC采用AXI-4標準與NAP通信,這是許多FPGA設計人員已經熟悉的接口標準。此外,2D NoC包括內置功能,例如跨時鐘域邏輯、流量控制和地址解碼等,這些功能不再需要包含在用戶邏輯中。Achronix的2D NoC的全功能實現為用戶省去了大量的設計工作,使設計人員能夠專注于連接到2D NoC的加速器。

除了縮短設計時間外,使用Achronix片上2D NoC的設計比使用軟2D NoC的設計使用更少的資源。結果是需要布局和布線的邏輯更少,從而使得工具的編譯時間更短。例如,與使用軟2D NoC的實現相比,使用Achronix片上2D NoC的設計布局和布線所需的時間不到一半。

結論

集成2D NoC的Speedster7t器件創新地帶來了FPGA設計過程的根本轉變。Achronix是第一家集成2D NoC的FPGA公司,它連接所有系統接口和FPGA邏輯陣列。這種新架構使Achronix FPGA器件特別適用于高帶寬應用,同時顯著提高了設計人員的工作效率。由于2D NoC管理著從設計在FPGA邏輯陣列中的數據加速器到高速數據接口之間的所有網絡功能,因此設計人員只需設計他們的數據加速器并將它們連接到NAP接入點。與使用軟2D NoC相比,設計人員可以受益于以下優點:

● 降低邏輯資源占有率并提高FPGA的整體性能

● 增加帶寬

● 減少對存儲器的需求

● 更快的設計時間和更短的工具編譯時間

表3:Speedster7t 2D NoC與Soft 2D NoC的總結比較

如希望進一步了解Achronix Speedster7t FPGA芯片及其2D NoC可以發揮的巨大效用。

原文標題:Achronix在其先進FPGA中集成2D NoC以支持高帶寬設計(WP028)

文章出處:【微信公眾號:Achronix】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636203 -

芯片

+關注

關注

463文章

54007瀏覽量

465896 -

NoC

+關注

關注

0文章

43瀏覽量

12163 -

Achronix

+關注

關注

1文章

78瀏覽量

23012

原文標題:Achronix在其先進FPGA中集成2D NoC以支持高帶寬設計(WP028)

文章出處:【微信號:Achronix,微信公眾號:Achronix】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

XS5018C:高性能2D/3D降噪ISP-TX 2K芯片電路圖資料

2D、2.5D與3D封裝技術的區別與應用解析

探索TRAVEO? T2G Cluster 6M Lite Kit:功能、應用與編程指南

淺談2D封裝,2.5D封裝,3D封裝各有什么區別?

【CPKCOR-RA8D1】3、2D繪圖引擎(D/AVE)DRW

Achronix亮相2025全球AI芯片峰會

Achronix邀您相約2025全球AI芯片峰會

從 2D 到 3.5D 封裝演進中焊材的應用與發展

TechWiz LCD 2D應用:不同結構下的VT曲線

Techwiz LCD 2D應用:二維LC透鏡建模分析

HT 可視化監控頁面的 2D 與 3D 連線效果

Achronix Speedster7t FPGA芯片中2D NoC的設計細節

Achronix Speedster7t FPGA芯片中2D NoC的設計細節

評論