Vivado自帶的仿真,個人覺得跑一些小模塊的仿真還是可以的,不過跑大的仿真系統(tǒng),容易無體驗感,建議用第三方工具,這邊就直接對ModelSim下手了,接下來介紹下這兩者聯(lián)合仿真的操作。

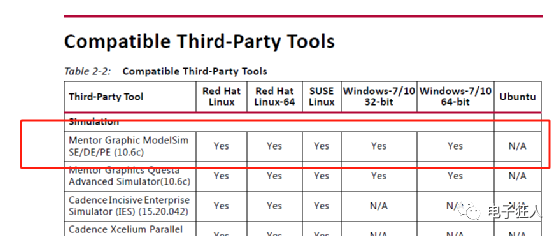

首先確定下自己的Vivado版本和適配的ModelSim版本,可以在ug973中,找到對應的版本,比如我用的Vivado是2018.2的,然后匹配的ModelSim是10.6c的版本。(有時候版本不匹配也能用,不過還是建議盡量匹配版本的好,省得出一些奇怪的問題)

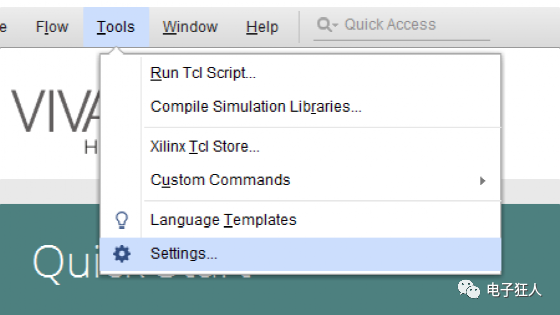

然后準備編譯仿真庫,打開Vivado,先打開Settings的仿真器配置 (注:我因為裝過多個版本,仿真器要換成最16.c的版本,不然編譯結(jié)果會因為版本不匹配出問題)

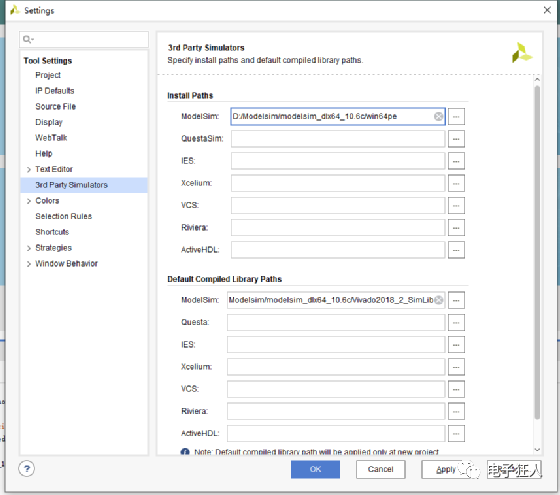

ModelSim的安裝路徑換成16.c版本的位置,庫路徑也設置好對應的位置,然后就可以OK保存并關(guān)閉了

ModelSim的安裝路徑換成16.c版本的位置,庫路徑也設置好對應的位置,然后就可以OK保存并關(guān)閉了

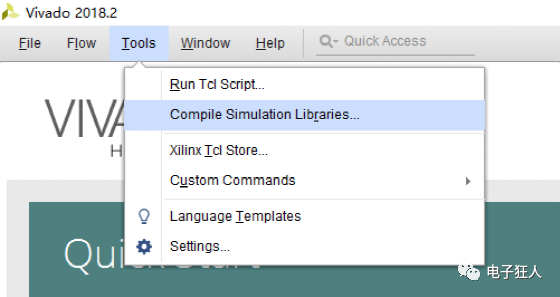

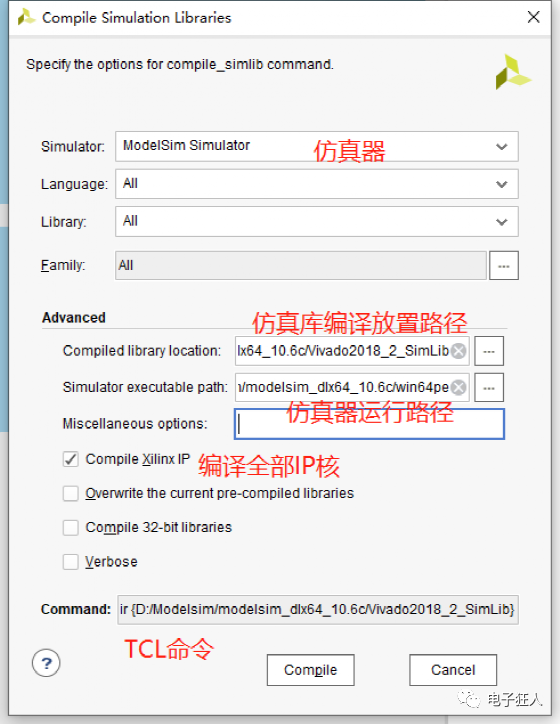

接著在菜單欄中選 Tools > Compile Simulation Libraries

設置項里選好仿真器(此處為ModelSim),編譯后的仿真庫放置路徑(就填上面設置的那個新的仿真庫路徑),ModelSim程序的路徑,IP核編譯那項別取消了,是為了編譯Xlinx全部IP核的,其他項保持默認即可;TCL的命令就是根據(jù)這些配置生成的,然后點Compile就可以開始慢慢等編譯結(jié)果了。

經(jīng)過漫長的等待。。。。。。

結(jié)果出來了,檢查下結(jié)果.......

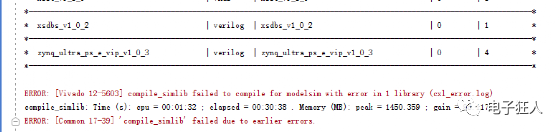

ERROR: [Vivado 12-5603] compile_simlib failed to compile for modelsim with error in 1 library

看著紅彤彤的ERROR,心里有那么一絲絲小慌,然后往上翻,看看哪ERROR了

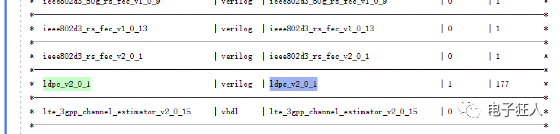

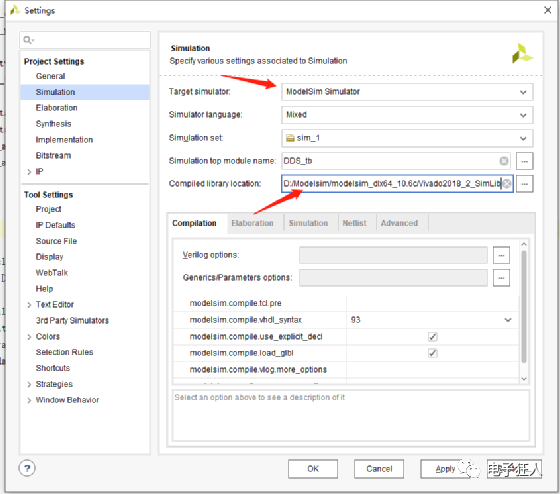

查到是ldpc編碼的這個IP核出了問題,這個平常也沒用到,就直接無視這個錯誤了(要是你們的沒錯誤,就更好了,這個好像是因為系統(tǒng)是64位導致的,具體就懶得深究了)…… 如果是出現(xiàn)很多errors,就建議先檢查下版本是否匹配上了,不然也不會瘋狂報錯…… 就接著往下說吧~ 打開要仿真的工程,然后對打開Settings,因為創(chuàng)建的工程默認是用的自帶的仿真配置,所以需要改下仿真設置,首先將 Target simulator 改為 ModelSim Simulator,其次仿真庫的位置也需要檢查下是不是剛剛編譯好的庫對應的路徑,檢查無誤就可以點OK,開始后面的了

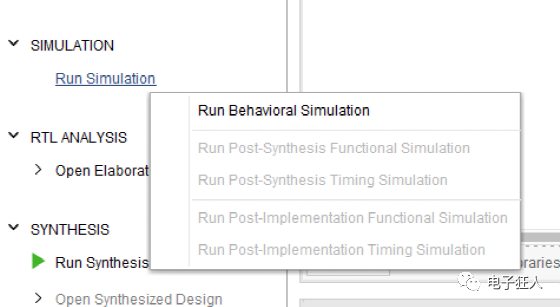

直接運行仿真

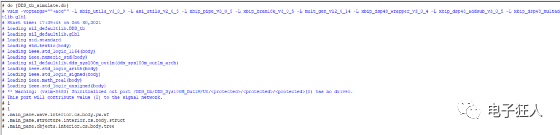

過一小會兒,Modelsim就被Vivado調(diào)用了,觀察窗口的輸出,正常無誤

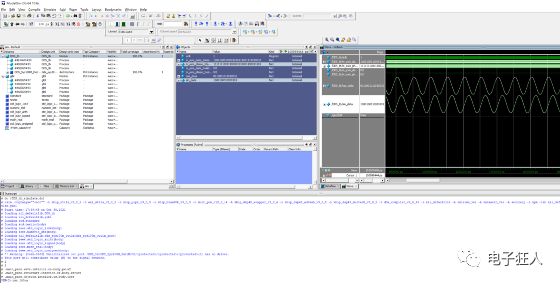

接著運行100us的仿真

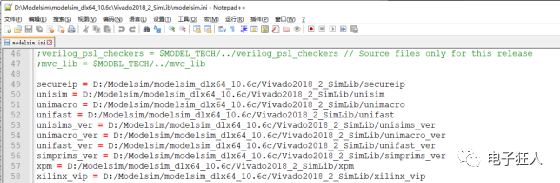

也能正常運行,聯(lián)合仿真OK~~ 最后補一點,假如自己不想編譯庫,想直接拿別人編好的,則拷貝好庫后,還需要對庫的初始化文件做對應的修改,找到庫路徑下的modelsim.ini(注:不要弄錯成ModelSim安裝路徑下的那個ini了),然后用編輯器打開

可以看到這些庫都有以絕對路徑的形式鏈接,所以如果是從別的地方拷過來的,或者你打算換個路徑放仿真庫,那么就需要將舊的路徑改為新的路徑,然后其他的使用操作就和上面的一模一樣了。

-

仿真

+關(guān)注

關(guān)注

55文章

4526瀏覽量

138588 -

ModelSim

+關(guān)注

關(guān)注

5文章

175瀏覽量

49428 -

Vivado

+關(guān)注

關(guān)注

19文章

860瀏覽量

71319

原文標題:Vivado與ModelSim的聯(lián)合仿真

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

如何使用Modelsim仿真I2C控制器

一文詳解SystemC仿真庫的編譯

【產(chǎn)品介紹】Modelsim:HDL語言仿真軟件

Vivado與ModelSim的聯(lián)合仿真操作

Vivado與ModelSim的聯(lián)合仿真操作

評論