摘要

一種形成介電間隔物的方法,包括提供襯底,文章全部詳情:壹叁叁伍捌零陸肆叁叁叁該襯底包括具有第一多個柵極結構的第一區(qū)域和具有第二多個柵極結構的第二區(qū)域和至少一種含氧化物材料或含碳材料。在第一區(qū)域上方形成厚度小于存在于第二區(qū)域中的含氮化物層的厚度的含氮化物層。在第一多個柵極結構和第二多個柵極結構上由含氮化物層形成介電間隔物。

背景

本公開涉及半導體結構和器件。更具體地,本公開涉及在半導體器件的制造中采用的蝕刻工藝。

為了能夠制造出比目前可行的更高集成密度的集成電路 (IC),例如 10 個存儲器、邏輯和其他設備,必須找到進一步縮小場效應晶體管 (FET) 尺寸的方法,例如金屬氧化物半導體場效應晶體管 (MOSFET) 和互補金屬氧化物半導體 (CMOS)。縮放通過縮小設備的整體尺寸和工作電壓同時保持設備的電氣特性來實現(xiàn)緊湊性并提高設備的工作性能。蝕刻工藝正在不斷改進,以滿足半導體器件規(guī)模增加 20 倍的需求。

總結

提供了一種形成介電柵極側壁間隔物的方法,其中提供介電柵極側壁間隔物的氮化物材料層的蝕刻速率通過控制在形成介電柵極側壁間隔物的蝕刻工藝期間存在的氧化物的量來調整. 在一個實施例中,形成介電間隔物30的方法包括提供襯底,該襯底包括具有第一多個柵極結構的第一區(qū)域和具有第二多個柵極結構和至少一種含氧化物材料的第二區(qū)域。

詳細說明

本文公開了要求保護的結構和方法的詳細實施例;然而,應當理解,所公開的實施例僅僅是可以以各種形式體現(xiàn)的所要求保護的結構和方法的說明。此外,結合各種實施例給出的每個示例旨在是說明性的,而不是限制性的。此外,附圖不一定按比例繪制,某些特征可能被夸大以顯示特定組件的細節(jié)。

審核編輯:符乾江

-

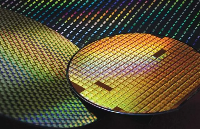

半導體

+關注

關注

339文章

30737瀏覽量

264138 -

刻蝕

+關注

關注

2文章

220瀏覽量

13779

發(fā)布評論請先 登錄

集成電路制造工藝中的刻蝕技術介紹

晶圓濕法刻蝕技術有哪些優(yōu)點

大尺寸玻璃晶圓(12 英寸 +)TTV 厚度均勻性提升技術

【新啟航】大尺寸碳化硅(150mm+)TTV 厚度均勻性提升技術

臺階儀表征MEMS壓力傳感器硅槽刻蝕:TMAH80℃下薄膜良率達到92.67%

濕法刻蝕sc2工藝應用是什么

超薄晶圓切割液性能優(yōu)化與 TTV 均勻性保障技術探究

LED 太陽光模擬器光照均勻性控制:從理論設計到工程實現(xiàn)

超薄晶圓淺切多道切割中 TTV 均勻性控制技術探討

基于淺切多道的晶圓切割 TTV 均勻性控制與應力釋放技術

改善刻蝕均勻性的技術

改善刻蝕均勻性的技術

評論