芯片刻蝕是半導體制造中的關鍵步驟,用于將設計圖案從掩膜轉移到硅片或其他材料上,形成電路結構。其原理是通過化學或物理方法去除特定材料(如硅、金屬或介質層),以下是芯片刻蝕的基本原理和分類:

1. 刻蝕的基本原理

刻蝕的本質是選擇性去除材料,即只去除不需要的部分,保留需要的部分。根據刻蝕方式的不同,可以分為以下兩類:

(1)濕法刻蝕(Wet Etching)

原理:利用化學液體(如酸、堿或溶劑)與材料發生化學反應,溶解目標材料。

例子:

用氫氟酸(HF)腐蝕二氧化硅(???2SiO2?),形成接觸孔。

用堿性溶液(如KOH)各向異性蝕刻硅,制造斜面或V形槽。

特點:

設備簡單、成本低。

橫向腐蝕明顯,精度較低,不適合微小圖形。

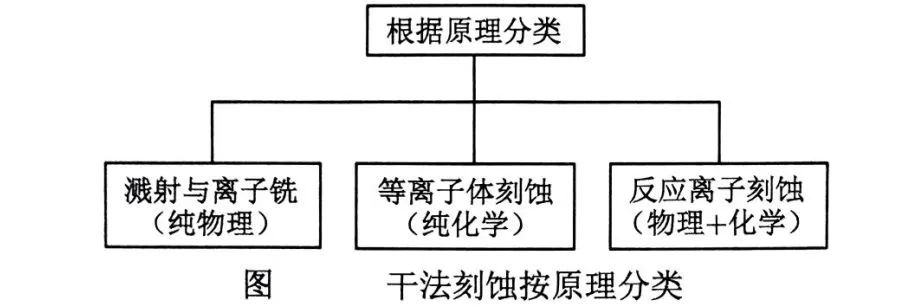

(2)干法刻蝕(Dry Etching)

原理:通過等離子體或離子束轟擊材料表面,利用物理或化學作用去除原子。

常見技術:

反應離子刻蝕(RIE):結合等離子體和化學反應。

電感耦合等離子體刻蝕(ICP):高密度等離子體實現高深寬比刻蝕。

深硅刻蝕(DRIE):用于制造高深寬比的硅結構(如MEMS器件)。

特點:

精度高、各向異性好,適合復雜圖形和深孔。

設備昂貴,參數控制復雜。

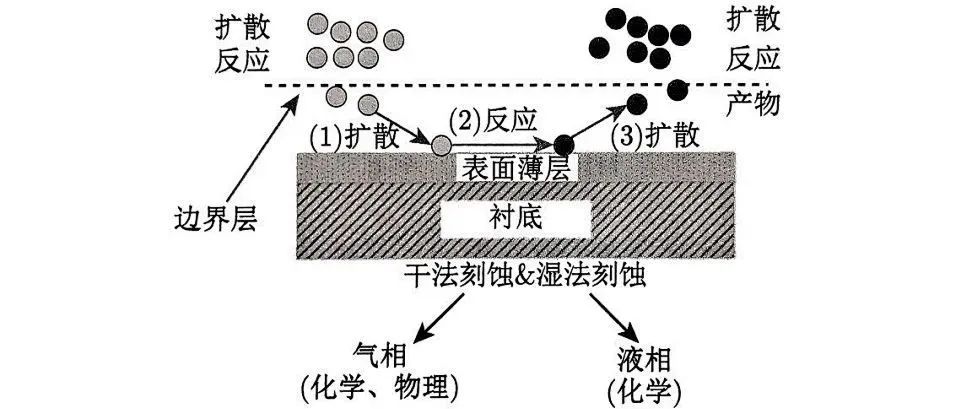

2. 刻蝕的核心機制

無論是濕法還是干法刻蝕,其核心機制包括以下兩種作用:

(1)化學腐蝕(Chemical Etching)

原理:刻蝕氣體或液體與材料發生化學反應,生成揮發性產物(如氣體或可溶物質)。

例子:

氟基氣體(如SF?、CF?)與硅反應生成SiF?(氣體)。

氫氟酸(HF)與二氧化硅(???2SiO2?)反應生成SiF?和水。

特點:依賴化學反應速率,選擇性高但各向異性差。

(2)物理濺射(Physical Sputtering)

原理:通過高能離子轟擊材料表面,物理擊出原子或分子。

例子:氬離子(Ar?)轟擊金屬或介質層,去除材料。

特點:各向異性好,但對掩膜層和底層材料損傷較大。

3. 刻蝕的關鍵參數

選擇性:只蝕刻目標材料,不損傷掩膜層或底層材料。例如,刻蝕二氧化硅時不損傷下方的硅襯底。

各向異性:控制橫向腐蝕,確保垂直方向刻蝕。干法刻蝕各向異性強,濕法刻蝕各向同性明顯。

深寬比:刻蝕深度與寬度的比值,高深寬比能力用于深孔或高密度結構(如TSV、FinFET)。

均勻性:保證晶圓內不同位置的刻蝕速率一致,避免圖形尺寸偏差。

4. 刻蝕的典型工藝流程

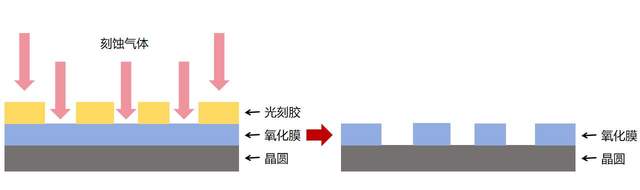

光刻定義圖案:通過光刻將設計圖案轉移到光刻膠或硬質掩膜上。

刻蝕:根據掩膜圖案,去除不需要的材料(如硅、金屬或介質層)。

去掩膜:移除剩余的光刻膠或硬質掩膜,完成圖形化。

5. 刻蝕的應用實例

晶體管制造:刻蝕多晶硅柵極、源漏極和溝道區域。

互連層:在金屬層或介質層上開孔(如接觸孔、通孔),實現上下層的電連接。

MEMS器件:通過深硅刻蝕制造懸空結構、腔體或微流體通道。

TSV(穿透硅通孔):在硅片上蝕刻深孔,用于3D芯片的垂直互連。

審核編輯 黃宇

-

芯片

+關注

關注

463文章

54007瀏覽量

465937 -

刻蝕

+關注

關注

2文章

220瀏覽量

13776

發布評論請先 登錄

集成電路制造工藝中的刻蝕技術介紹

濕法蝕刻的最佳刻蝕條件是什么

晶圓濕法刻蝕技術有哪些優點

濕法刻蝕的工藝指標有哪些

濕法刻蝕的主要影響因素一覽

MEMS制造中玻璃的刻蝕方法

芯明天壓電納米技術如何幫助刻蝕機打造精度天花板

一文詳解濕法刻蝕工藝

芯片刻蝕原理是什么

芯片刻蝕原理是什么

評論