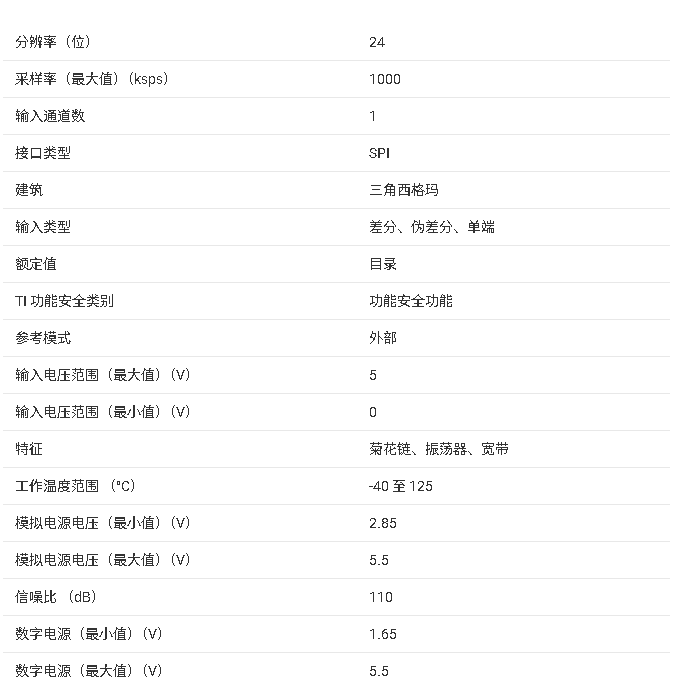

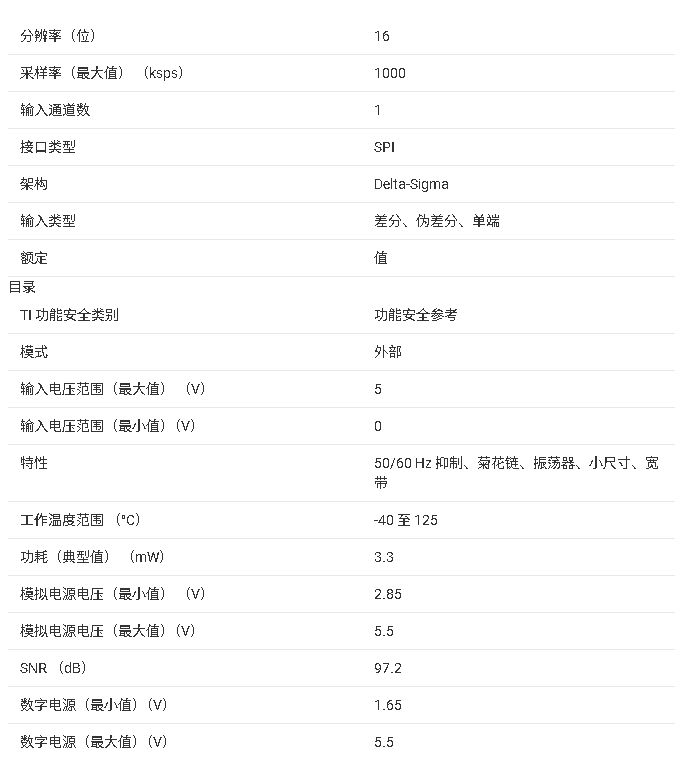

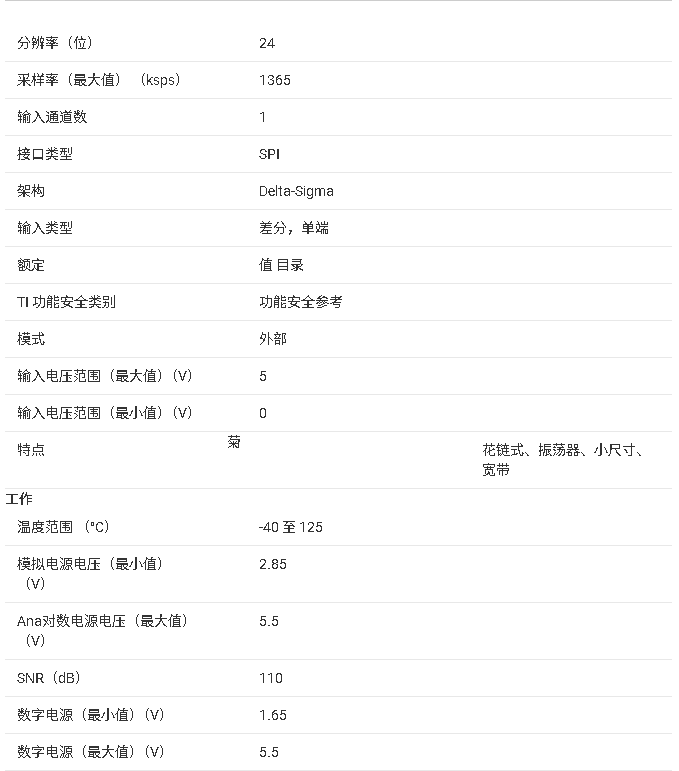

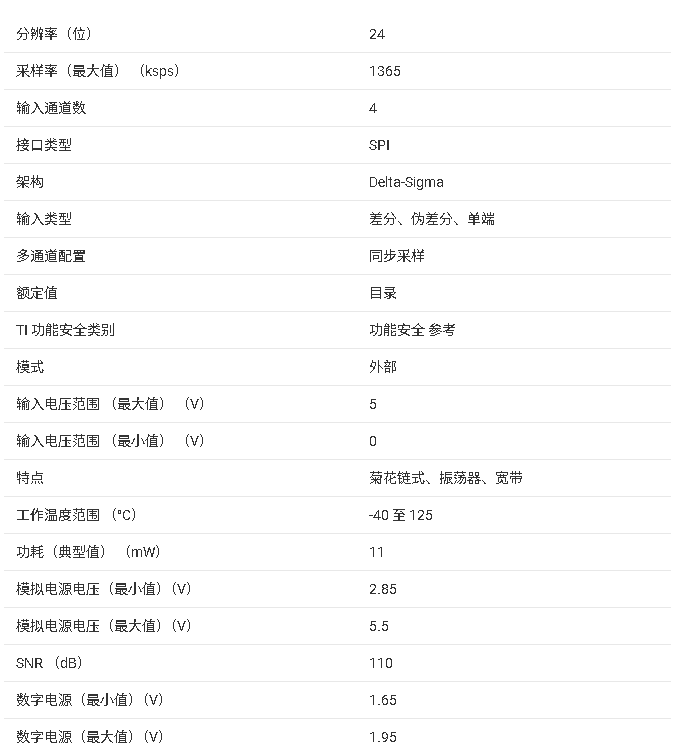

ADS127L11是德州儀器在2021年發布的高分辨率高采樣率ΣΔADC,在評估其噪聲和有效分辨率的時候可以運用本文論述的基于Histogram Analysis的方法。

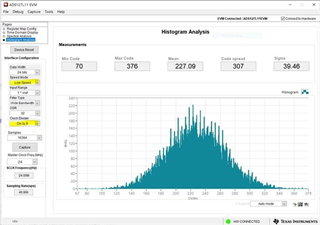

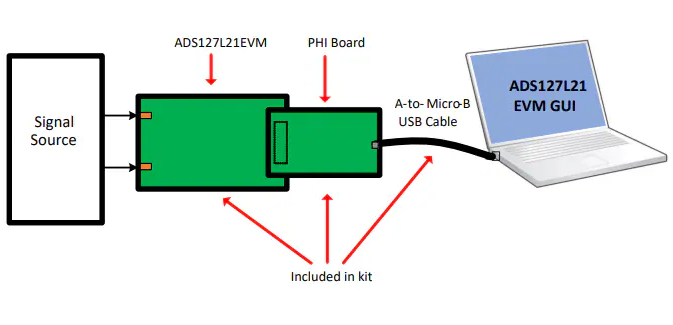

首先給ADS127L11EVM輸入一個穩定的直流電壓源,該直流源需要深度去耦以減少輸入的噪聲影響,然后對其進行大量的重復采樣。采樣的統計結果會顯示在ADS127L11EVM-PDK GUI的Histogram Analysis界面中。如圖1統計了16384次采樣結果。

圖1. ADS127L11EVM-PDK GUI的Histogram Analysis

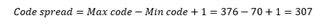

Code spread是ADC輸出code的峰峰值,在圖1中為307。

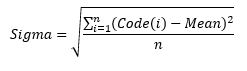

在統計結果中,還有一個名為Sigma(σ)的參數,它的定義為統計結果的標準差。

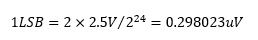

其中Code(i)是每次采樣的結果,n是采樣樣本量16384,Mean是所有樣本的平均值,在圖1中為227.09。我們可以利用Sigma計算出有效分辨率。選擇ADC的輸入范圍為±2.5V,則滿幅度范圍為FSR為5V,1LSB的值為,

可以運用Code spread和Sigma分別計算出噪聲的峰峰值(Vpp)和均方根值(Vrms)。

運用可以計算出有效分辨率,

運用可以計算出無噪聲代碼分辨率Noise Free Code Resoltuion。超過這個位數的輸出代碼是沒有明確解析的,所以要保守的評估ADC的分辨率可以用這個指標。

需要注意本文計算的有效分辨率和有效位數ENOB是有區別的。ENOB的定義是在輸入滿量程正弦波的時候,通過測量信納比(SINAD)得到的。

還要注意ADS127L11能支持高的采樣率,尤其在High Speed Mode的時候,需要為參考輸入和ADC輸入選擇合適的buffer(比如THS4551)以提供足夠的驅動能力,否則Histogram Analysis就會引入因驅動能力不足而導致的誤差。REF6225集成了buffer,適合用于ADS127L11的參考。

ADS127L11EVM默認的輸入時鐘是24MHz。在使用Low Speed Mode的時候需要將Clock Divider設置為Div by 8以滿足該模式最高3.2MHz時鐘頻率的要求。

審核編輯:湯梓紅

-

德州儀器

+關注

關注

123文章

1998瀏覽量

145382 -

adc

+關注

關注

100文章

7932瀏覽量

556729 -

測量

+關注

關注

10文章

5692瀏覽量

116926

發布評論請先 登錄

ADS127L01 24 位高速寬帶 ADC 核心信息總結

ADS127L11 24位、400kSPS、Δ-Σ ADC技術手冊

ADS117L11 技術文檔總結

ADS127L21 技術文檔總結

ADS1014L/ADS1015L 系列模數轉換器技術文檔總結

ADS127L21B 產品技術文檔總結

ADS127L18四通道 / 八通道同步采樣 24 位 ADC 產品文檔總結

ADS127L14/ADS127L18 ADC 產品文檔總結

ADS117L14/ADS117L18 核心信息總結

深入解析德州儀器ADS127L11 24位Δ-Σ ADC的技術特性與應用

德州儀器ADS127L21高精度24位ΔΣ模數轉換器技術解析

ADS127L21EVM-PDK評估套件技術解析與應用指南

Texas Instruments ADS127L18EVM-PDK 評估模塊(EVM)數據手冊

Texas Instruments ADS127L21B寬頻Δ-ΣADC數據手冊

Texas Instruments ADS127L18 24 位模數轉換器數據手冊

理解和運用ADS127L11EVMGUI中的HistogramAnalysis

理解和運用ADS127L11EVMGUI中的HistogramAnalysis

評論