1.概述

隨著互聯網時代的到來,人類所產生的數據發生了前所未有的、爆炸性的增長。IDC預測,全球數據總量將從2019年的45ZB增長到2025年的175ZB[1]。同時,全球數據中近30%將需要實時處理,因而帶來了對FPGA等硬件數據處理加速器的需求。如圖1所示。

在這樣的數據高速增長的情況下,用于傳輸數據的網絡帶寬和處理數據所需要的算力也必須急速增長。傳統的CPU已經越來越不堪重負,所以用硬件加速來減輕CPU的負擔是滿足未來性能需求的重要發展方向。未來的硬件發展需求對于用于加速的硬件平臺提出了越來越高的要求,可以概括為三個方面:算力、數據傳輸帶寬和存儲器帶寬。Achronix的新一代采用臺積電7nm工藝的Speedster 7t FPGA芯片根據未來硬件加速和網絡加速的需求,在這三個方面都做了優化,消除了傳統FPGA的瓶頸。下面我們重點說一說為了提高存儲器帶寬,Achronix通過采用硬核GDDR6控制器所帶來的優勢。2.

GDDR6的發展

在GDDR的設計之初,其定位是針對圖形顯示卡所特別優化的一種DDR內存。因為2000年后電腦游戲特別是3D游戲的發展和火爆,使運行電腦游戲的顯卡需要有大量的高速圖像數據交互需求,GDDR在這種情況下應運而生。第一個GDDR標準是基于DDR的GDDR2,隨后發展到了基于DDR3的GDDR5,在一段時間中非常流行。

2016年,GDDR5X正式發布,它引入了具有16n預取的四倍數據速率模式,但代價是訪問粒度從GDDR5的32Byte提高到了64Byte。2018年,GDDR6發布,數據速率達到了16Gbps,帶寬幾乎是GDDR5X的兩倍,同時采用了雙通道設計,訪問粒度和GDDR5一樣是32Byte。

3.GDDR6和DDR4/5的比較

GDDR一直以來是針對圖形顯示卡所優化的一種DDR內存。因為顯卡處理圖像數據,特別是3D圖像數據對顯存帶寬的要求更高,GPU和GDDR之間的數據交換非常頻繁。而DDR內存專注于與CPU進行數據交換的效率,因此對于整體存取性能、低延遲更為看重,所以在CPU和傳統的FPGA中基本都是用DDR4。

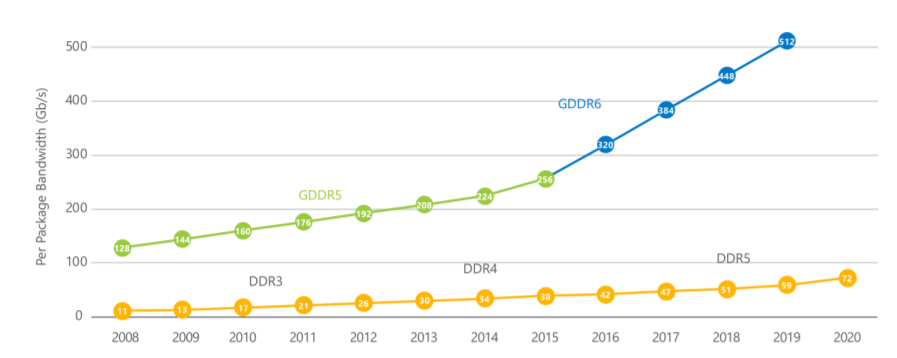

隨著硬件加速需求對于存儲器的帶寬提出了越來越高的要求,傳統的DDR4帶寬顯然已經無法滿足要求,Achronix看重了GDDR6在數據存儲中的帶寬優勢,創新地將GDDR6引入到了FPGA,徹底解決了傳統FPGA存儲帶寬不夠的瓶頸。2020年7月15日,JEDEC存儲協會正式發布了DDR5 SDRAM的標準(JESD79-5),內存的頻率相對DDR4的標準頻率有了大幅的提升,總傳輸帶寬也提升了38%,但是還是和GDDR6的帶寬有一定的差距。GDDR6和DDR4/5的帶寬對比。

圖2 GDDR與DDR帶寬發展對比

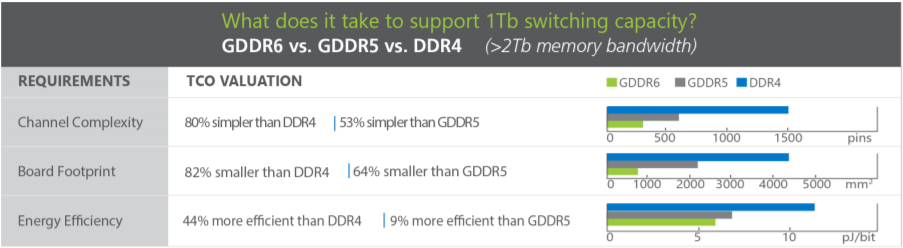

如果實現同一個大帶寬存儲的應用,在提供相同的存儲器帶寬的情況下,無論在設計復雜度,PCB占用面積,還是在功耗方面,與DDR4相比,GDDR6的性能都有很大的提高,如圖3所示[2]。

圖3 GDDR6和DDR4性能對比4.

GDDR6和HBM2的比較

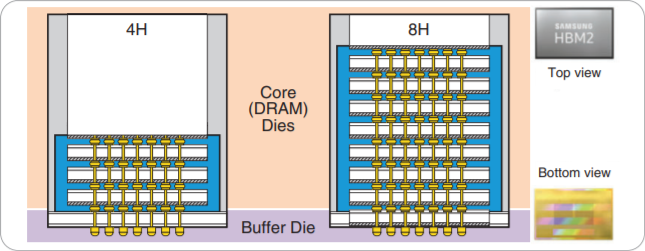

HBM全稱High Bandwidth Memory,最初的標準是由JEDEC在2013年發布。2016年1月,HBM的第二代HBM2正式成為工業標準。HBM的出現也是為了解決存儲器帶寬問題。與GDDR6不同的是,HBM內存一般是由4個或者8個HBM的Die堆疊形成,我們稱之為一個Stack。如圖4所示[4]。

圖4 HBM Die的堆疊

我們以市面上帶有HBM2的高端 FPGA為例,這個系列的FPGA集成了1~2個這樣的HBM2 Stack。兩個Stack之間是相互獨立的,各自有自己的地址空間。

每個Die都有獨立的兩個128bit的Channel,所以4個Die 8個通道就是1024bit的位寬,HBM2的頻率是900MHz,按DDR的方式訪問,一個Stack總共帶寬是 900(MHz)x 2(DDR)x 1024(位寬)/8 = 230GB/s,兩個Stack最高可以到460GB/s的帶寬。

Achronix的Speedster 7t FPGA集成了8個GDDR6的硬核,每個GDDR6的硬核支持雙通道。總的帶寬是 16Gbps x 16(位寬)x 2(通道)x 8(控制器)/8 = 512 GB/s,略高于帶HBM2的FPGA存儲器帶寬。

從成本上來看,目前GDDR6與HBM2相比有著很大的優勢,HBM2技術工藝要求高,目前芯片的良率和產量都會受到很大的影響。同時GDDR6使用起來更靈活,使用片外的DRAM,可以根據應用要求,選擇不同速率,不同容量的GDDR6顆粒。HBM2的優勢在于集成度高,不占用PCB板的面積。圖5是DDR4、GDDR6和HBM2在成本上的一個綜合比較。

編輯:jq

-

FPGA

+關注

關注

1662文章

22480瀏覽量

638521 -

存儲器

+關注

關注

39文章

7750瀏覽量

172106 -

帶寬

+關注

關注

3文章

1048瀏覽量

43532 -

HBM

+關注

關注

2文章

432瀏覽量

15876

原文標題:GDDR6給FPGA帶來的大帶寬存儲優勢以及性能測試(上)

文章出處:【微信號:Achronix,微信公眾號:Achronix】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

深入解析IGLOO2 FPGA與SmartFusion2 SoC FPGA:性能、特性與應用

探索Arria V系列FPGA:高性能與低功耗的完美結合

RIGOL超便攜示波器的性能與優勢

AMD 推出第二代 Kintex UltraScale+ 中端FPGA,助力智能高性能系統

高性能網絡存儲設計:NVMe-oF IP的實現探討

昆侖芯R200 AI加速卡技術規格解析

CW32L010F8P600的優勢

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

探究GDDR6給FPGA帶來的大帶寬存儲優勢以及性能測試(上)

探究GDDR6給FPGA帶來的大帶寬存儲優勢以及性能測試(上)

評論