任何適合產品實現的算法,都是將簡易實現作為第一目標。CORDIC算法是建立在適應性濾波器、FFT、解調器等眾多應用基礎上計算超越函數的方法。其核心思想是二分逐次逼近。

CORDIC(Coordinate Rotation Digital Computer)算法即坐標旋轉數字計算方法,是J.D.Volder1于1959年首次提出,主要用于三角函數、雙曲線、指數、對數的計算。該算法通過基本的加和移位運算代替乘法運算,使得矢量的旋轉和定向的計算不再需要三角函數、乘法、開方、反三角、指數等函數。

本文是基于使用Verilog HDL設計實現Cordic算法,實現正弦、余弦、反正切函數的實現。將復雜的運算轉化成RTL擅長的加減法和乘法,而乘法運算可以用移位運算代替。Cordic算法有兩種模式,旋轉模式和向量模式。可以在圓坐標系、線性坐標系、雙曲線坐標系使用。本文初步實現在圓坐標系下的兩種模式的算法實現。

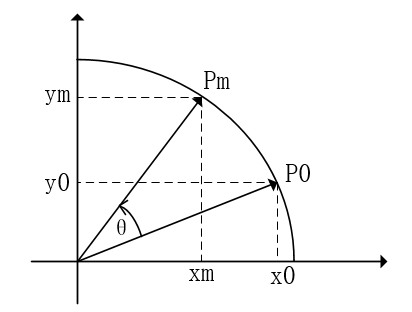

旋轉模式,迭代位移算法。假設有一點P0(x0,y0),經過逆時針旋轉角度θ,到達點Pm(xm,ym),我們根據數學運算可以得到公式如下:

xm = x0cosθ - y0sinθ

= cosθ(x0 – y0tanθ)

ym = x0sinθ +y0cosθ

=cosθ(x0tanθ+y0)

如果不考慮旋轉后的向量模值,只考慮旋轉角度,即去掉cosθ,得到如下方程式。這里旋轉的角度的正確的,但xm和ym的值增加。cosθ值是小于等于1的,它的倒數值大于等于1,所以xm和ym模值增大了。去掉cosθ項可以方便我們后面的坐標平面旋轉的計算。這里稱為偽旋轉。

xm = x0 – y0tanθ ym =x0tanθ+y0

Cordic的方法核心就是偽旋轉,將旋轉角θ細化成若干個大小固定的角度θi,規定θi滿足tanθi = 2^-i,通過一系列的迭代旋轉,每次旋轉θi,i為迭代次數,規定∑θi的范圍即旋轉角度θ的范圍為[-99.7, 99.7]。如果θ的大于這個范圍則可通過三角運算操作轉化到該范圍的角度。

我們通過事先將所有每次旋轉的角度計算出來,由于每次旋轉的角度是固定的,所以經過i次旋轉的∑θi可能會超過θ,所以就必須設置一個方向值di,如果旋轉角度之和已經小于θ,則di為1,下次旋轉繼續為逆時針旋轉,如果旋轉角度之和大于θ,則di為-1,下次旋轉為順時針。設置zi+1為旋轉剩余角度,zi+1 = z0 – di *zi,z0 = θ,隨著i值的增大,zi+1會趨向于0時,即旋轉結束。di與zi的符號位相同。

采用偽旋轉的方法,每次提出一個cosθi,旋轉結束后會產生一個∏cosθi的累乘,一旦我們確定了迭代次數,∏cosθi就是一個常數,迭代公式可寫為。這是將cosθi提出、tanθi 替換成 2^-i后的結果。di與zi的符號位相同。

xi+1 = xi - di * yi * 2^-i yi+1 = yi + di * xi * 2^-i zi+1 = z0 - di * θi

設迭代i = n - 1,那么旋轉n次后得到Pm的坐標應該為(xn * ∏cosθi, yn * ∏cosθi)。因為每次迭代都會提出一個cosθi,旋轉n次后的xn和yn就會少乘一個∏cosθi,所以實際上最終的Pm坐標角度近似于(xn * ∏cosθi, yn * ∏cosθi)。

xn * ∏cosθi = x0cosθ - y0sinθ yn * ∏cosθi = y0cosθ + x0sinθ xn = 1/∏cosθi (x0cosθ – y0sinθ) yn = 1/∏cosθi (y0cosθ +x0sinθ)

伸縮因子,KN = 1 / ∏cosθi,已知迭代次數,我們可以預先計算KN的值。如下這是使用MATLAB計算出的迭代結果數值。

xn =KN (x0cosθ – y0sinθ) yn = KN (y0cosθ +x0sinθ)

從上表可以得出,我們預先計算出KN的值,然后令x0 = ∏cosθi,y0 = 0,則上述公式可化簡為

xn = cosθ yn = sinθ 即可實現正弦、余弦操作了。旋轉模式

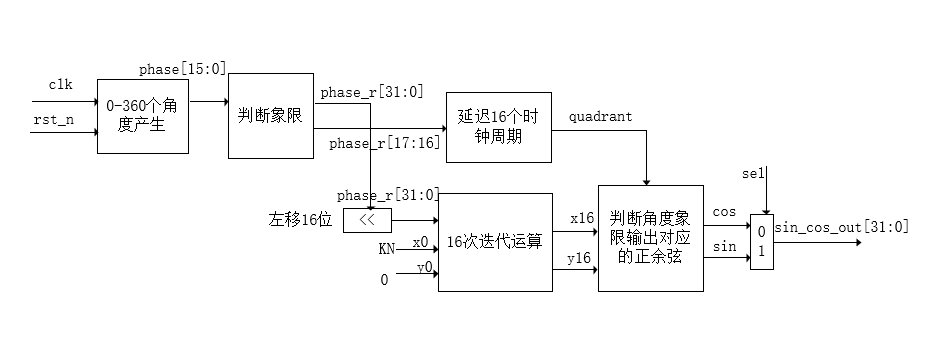

Cordic算法旋轉模式使用Verilog HDL的實現流程

確定迭代次數,將每次迭代的角度計算出來,預先定義為參數,為了避免浮點運算,將角度值向左移位16位,取整數部分。

根據迭代公式進行迭代計算,本設計取16次迭代,從上表可以看出,當迭代次數越大時,1/∏cosθi會趨向于一個確定值。如果對結果精度要求更高,可以設置更高的迭代次數,根據迭代次數,可以將伸縮因子KN = 1/∏cosθi計算出來。同樣將其左移16位。

xi+1 = xi - di * yi * 2^-i yi+1 = yi + di * xi * 2^-i zi+1 = z0 - di * θi

設置x0 = ∏cosθi,y0 = 0,則求出x16 = cosθ,y16 = sinθ。

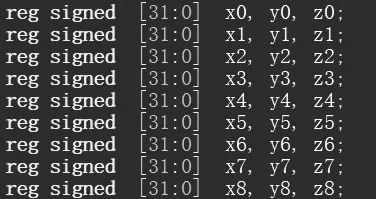

這里需要注意的是,我們在進行迭代運算的時候,將2^-i變成移位運算,對于正余弦來說是有正負的,所以在一開始定義的時候,就應該定義成有符號數,Verilog中也可以定義有符號數,最高位表示符號位,定義如下

迭代寄存器定義為有符號數,那么我們移位運算就不能用>>邏輯右移<<邏輯左移或來移位了,而是用>>>算術右移和<<<算術左移。邏輯左移也就相當于算數左移,右邊統一添0?,邏輯右移,左邊統一添0?,算數右移,左邊添加的數和符號有關。

例如1010_1010, []是添加的位 邏輯左移一位:0101_010[0] 算數左移一位:0101_010[0] 邏輯右移一位:[0]101_0101 算數右移一位:[1]101_0101

迭代運算采用16級流水線進行運算,最終需要判斷輸出的正余弦值在哪個象限,前面講旋轉角度θ的范圍為[-99.7,99.7],不在這個范圍我們要進行三角運算使其滿足這個范圍,當輸入的角度小于90度即可進行計算,當輸入角度大于90度小于180度,將輸入角度減去90度并設定當前角度處于第二象限,然后進行計算,當輸入角度大于180度小于270度,將輸入的角度減去180度設置當前角度處于第三象限,進行計算,當輸入的角度大于270度,減去270設置當前角度處于第四象限,進行計算。象限的設定通過quarant寄存器實現。

如果角度在第一象限,sin(x) = sin(a),cos(x) = sin(a)最后的結果x16 = cosθ, y16 = sinθ,這里我想起了那句口訣,一全正,二正弦,三正切,四余弦

如果角度在第二象限,

sin(x) = sin(a+90) = cos(a),

cos(x) = cos(a+90) = -sin(a)

如果角度在第三象限,

sin(x) = sin(a+180) = -sin(a),

cos(x) = cos(a+180) = -cos(a)

如果角度在第四象限,

sin(x) = sin(a+270) = cos(a),

cos(x) = cos(a+270) = -sin(a)

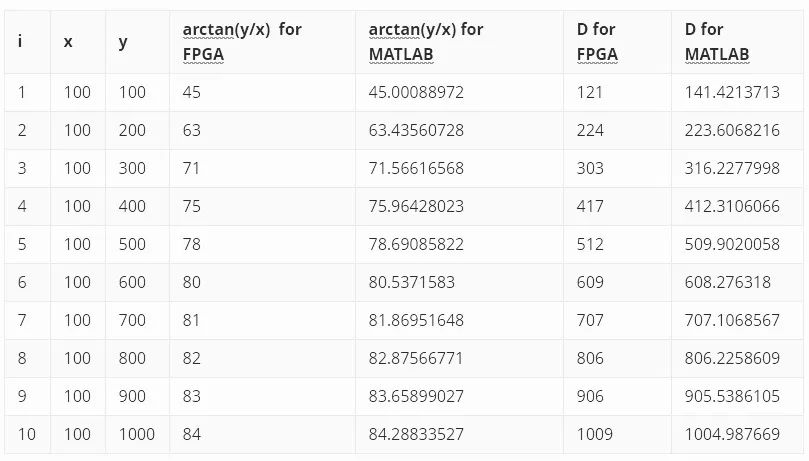

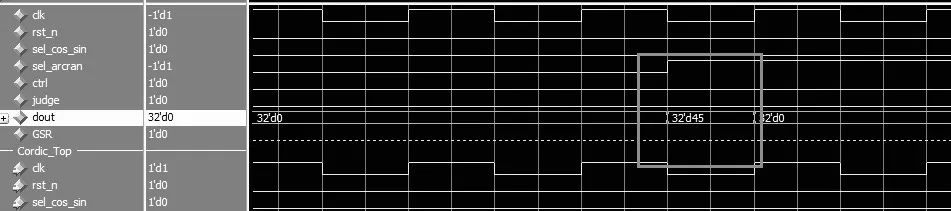

對于正數,我們直接賦值輸出,負數,這里使用有符號數表示,將其取反加1即可。最終使用modelsim對算法進行仿真,從波形圖上看已經初步實現了sin,cos函數。

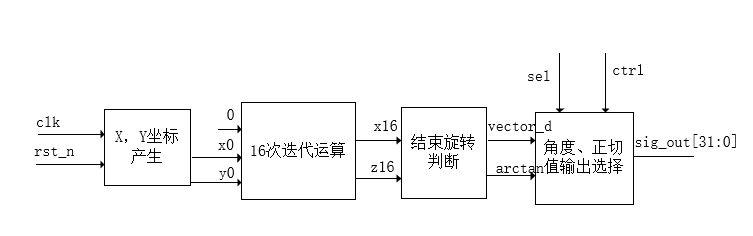

向量模式

Cordic算法在向量模式下的計算方法和旋轉模式基本上是類似的,設有一點P0(x0, y0),經過旋轉一定角度到與x軸重合,得到點Pm(xm, ym),即ym = 0。

xm = x0cosθ - y0sinθ

= cosθ(x0 – y0tanθ)

ym = y0cosθ + x0sinθ

= cosθ(y0 +x0tanθ) = 0

我們設置x0 = x, y0 = y, z0 = 0,迭代次數為16,經過16次迭代后得到zn = θ = arctan(y/x)和坐標所代表的向量的模值d = xm = xn * ∏cosθi,di與yi方向相反,即當時結束運算。實現方法為判斷yi的符號位,符號位為1,di為1,符號位為0,di為-1。

xi+1 = xi - di * yi * 2^-i

yi+1 = yi + di * xi * 2^-i

zi+1 = z0 - di * θi

關于反正切函數,由于在[-99.7°,99.7°]范圍內,所以我們輸入向量P0(x0, y0)時,需要保證其在第一、四象限。

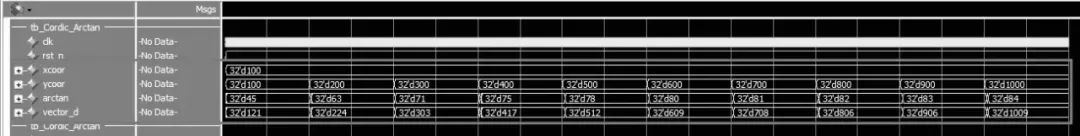

下面是使用MATLAB計算出來的數據和FPGA計算出來的數據進行比較。

從FPGA計算出的結果與MATLAB來比較,和實際結果之間的誤差還是挺小的,畢竟是硬件計算出來的數據,向量的誤差就比較大了,如果對于精度比較高的計算,我們可以通過提高迭代次數來提高精度。

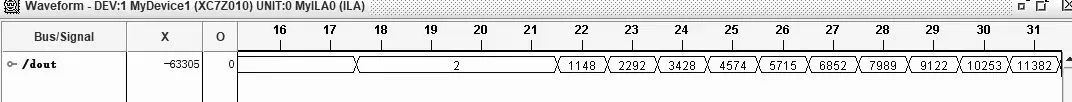

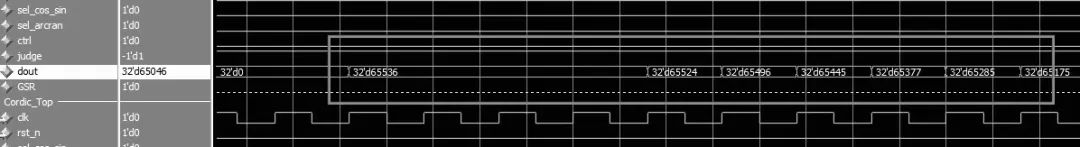

使用ISE進行綜合并下載工程到開發板上實驗結果比較。

旋轉模式

Sin的理論數據

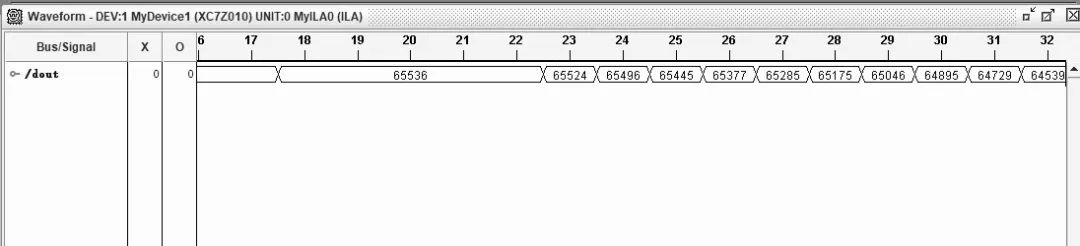

Chipscope抓取到的數據

Cos的理論數據

Chipscope抓取到的數據

向量模式

Arctan(y/x)理論數值

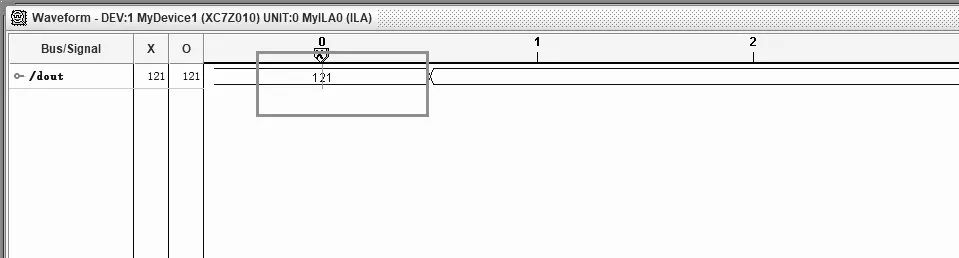

Chipscope抓取到的數據

坐標的模值的理論數據

責任編輯:haq

-

Verilog

+關注

關注

30文章

1374瀏覽量

114648 -

HDL

+關注

關注

8文章

332瀏覽量

49038

原文標題:基于Verilog的Cordic算法實現

文章出處:【微信號:bianpinquan,微信公眾號:變頻圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Verilog HDL語法學習筆記

FPGA 入門必看:Verilog 與 VHDL 編程基礎解析!

CORDIC模塊——提高計算能力的性價比神器

【產品介紹】Modelsim:HDL語言仿真軟件

使用NucleiStudio生成tb仿真需要的.verilog文件

SM4算法實現分享(一)算法原理

復雜的軟件算法硬件IP核的實現

AES加解密算法邏輯實現及其在蜂鳥E203SoC上的應用介紹

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

使用Simulink自動生成浮點運算HDL代碼(Part 1)

基于CORDIC算法的NCO實現

CORDIC算法原理及實現

【微五科技CF5010RBT60開發板試用體驗】Cordic數學計算測試

vivado IP核cordic中sin和cos的計算

使用Verilog HDL設計實現Cordic算法

使用Verilog HDL設計實現Cordic算法

評論