MRAM,即磁阻式隨機訪問存儲器的簡稱,兼備SRAM的高速讀寫性能與閃存存儲器的非易失性。STT-MRAM是通過自旋電流實現信息寫入的一種新型MARM,屬于MRAM的二代產品,解決了MRAM寫入信息存在的問題。

STT-MRAM存儲單元的核心仍然是一個MTJ(磁性隧道結),由兩層不同厚度的鐵磁層及一層幾個納米厚的非磁性隔離層組成,它是通過自旋電流實現信息寫入的。目前,STT-MRAM已經從幾家代工廠(GlobalFoundries、英特爾、三星、臺積電和聯電)中脫穎而出,成為一種非常有吸引力的IP選擇。

STT-MRAM具有以下幾個出色的特性:

STT-MRAM的開發步驟包括以下幾項:

第一步是材料的堆棧工程——例如,晶體結構、原子組成、厚度和每個層邊界的界面特性。需要通過詳細的“自旋極化”計算確定以下材料特性:

第二步是擴展電子級、“基態、零K”材料模擬。

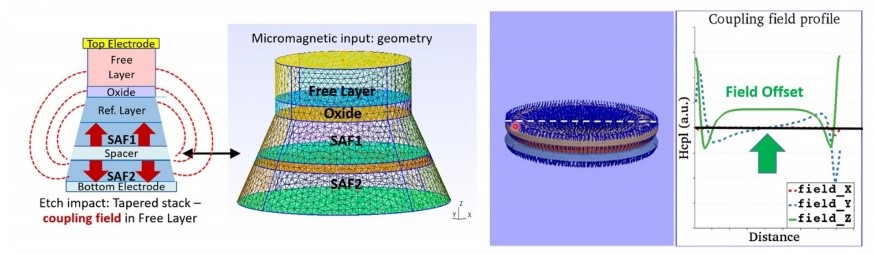

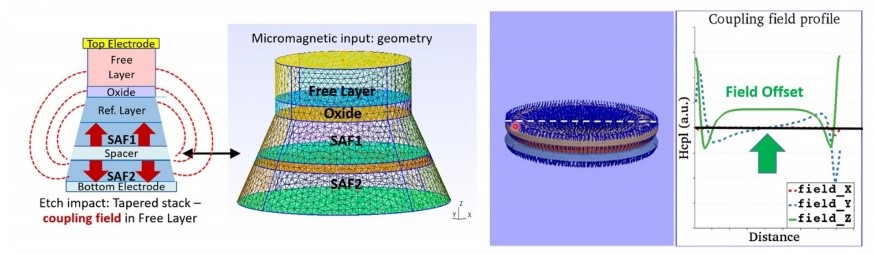

第三步是將 MTJ 物理維度引入到工藝開發中。下圖說明了磁性“耦合場”在制造后如何存在于錐形、非完全圓柱形 MTJ 中。

最后一步是將之前對材料、溫度相關性和 MTJ 尺寸的分析抽象為合適的“緊湊型器件模型”, MRAM陣列設計人員可以用陣列解碼的 SPICE 模型結合位單元存取晶體管、寫入驅動器和讀取傳感設備。

與當前的嵌入式閃存相比,STT-MRAM 在以下幾個方面都具有優勢:

所有這些特性優勢都是在嚴格的環境條件下應用,例如-40℃~125℃——對應于帶有eMRAM IP的工業應用SoC。

制造方式實際上也是STT-MRAM優于閃存的點。以臺積電32Mb嵌入式STT-MRAM為例,閃存需要12個或更多額外的掩模,只能在硅基板上實現,并且以頁面模式寫入。由于MTJ器件能夠通過三個左右額外的掩膜嵌入芯片的線路后端(BEOL)互連層,因此STT-MRAM在后段(BEOL)金屬層中實現僅需要2-5個額外的掩模,并且可以以字節模式寫入。

將STT-MRAM與最新的通用存儲候選進行比較,STT-MRAM的讀寫時間分別為2和20 ns,而相變RAM(PRAM)的讀取時間為20~50ns,寫入的時間為30ns。此外,STT-MRAM的耐久性也是要優于PRAM的。

當然STT-MRAM也有自身的一些問題。在基于STT-MRAM的許多應用中,磁場干擾是一個潛在的問題。因此 STT-MRAM 陣列的磁抗擾度 (MI) 是一個新的可靠性參數。在最近的 2021 年 VLSI 研討會上,GLOBALFOUNDRIES 的 MRAM 負責人 Vinayak Bharat Naik 解讀了采用 22FDX-SOI 工藝技術制造的 MRAM 陣列的磁抗擾度實驗分析結果。值得注意的是,該技術還具有非常吸引人的 RF 特性。因此,可能存在帶有電感元件的片上 RF IP,即便這些電感元件會發出顯著的場強。下面看看STT-MRAM對于外部場強和片上場強的反應。

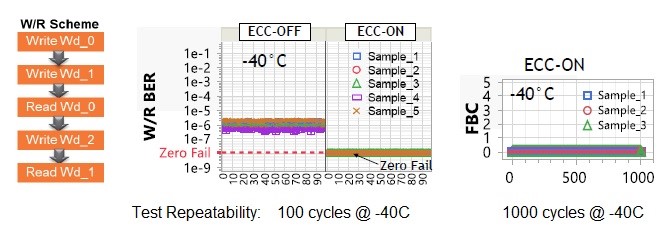

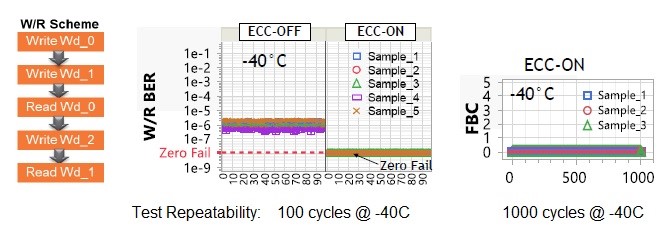

外部場強源自 SoC 封裝之外。Vinayak 展示了應用于 STT-MRAM 測試站點的實驗設置和 MI 分析結果。下圖顯示了(ECC 校正的)存儲器讀寫 BER 為零,活動 MI 大于 250 Oe。

另外,Vinayak 還強調,MTJ 層內磁化疇的各向異性表明外部磁場和 STT-MRAM 測試點表面之間的入射角可能會影響抗干擾性。

SoC 芯片內的抗磁性能有兩個方面:

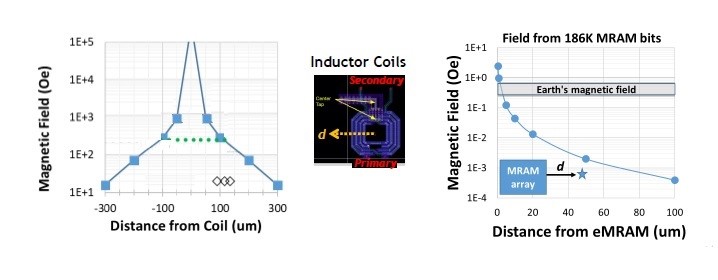

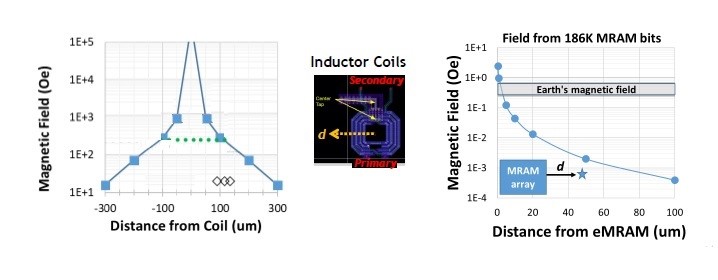

Vinayak 分享了分析數據,顯示感應線圈的磁場強度與分離距離的關系,如下所示。右上方的圖表顯示了源自嵌入式 STT-MRAM 陣列的磁場。在示例中,MRAM陣列場非常小,因此對LC諧振回路振蕩頻率的影響可以忽略不計。

嵌入式MRAM 確實引入了一個新的可靠性問題——陣列對來自 SoC 封裝外部或芯片上電感電路的磁場的“抗擾度”。在制造環節,為了解決磁干擾性問題,制造商選擇在封裝上沉積0.3mm厚的磁屏蔽層。實驗表明在移動設備的商用無線充電器的磁場強度為3500Oe的情況下,暴露100小時的誤碼率可以從> 1E6 ppm降低到1ppm。另外,在650 Oe的磁場下,在125°C下的數據保存時間超過10年。

目前MRAM軟件技術正在世界各地的實驗室中開發,但是隨著STT-MRAM產品成本的降低,無論是嵌入式產品還是獨立產品,MRAM軟件技術都可能成為MRAM取代最快的靜態隨機存取存儲器應用的手段,提供更高的非易失性存儲器密度。

談到應用,STT-MRAM可以在許多嵌入式應用中替代NOR閃存和SRAM。非易失性存儲使用NOR閃存存儲代碼,并將數據傳輸到SRAM充當緩沖區或高速緩存。例如低端手機同時使用NOR和SRAM,可以很容易地用單個STT-MRAM芯片替換它們。

同時,STT-MRAM具有重要的軍事應用,在抗惡劣環境高性能計算機、軍用衛星、導彈、火箭、航天飛行器控制和數據存儲系統中都需要具有超高密度、超大容量、超低能耗、隨機存儲、非易失性、結構簡單、抗輻照能力強等優點的存儲器系統,這些特性STT-MRAM都具備。

本文由電子發燒友編輯整理自公開資料和semiwiki技術文章,轉載請注明!

STT-MRAM存儲單元的核心仍然是一個MTJ(磁性隧道結),由兩層不同厚度的鐵磁層及一層幾個納米厚的非磁性隔離層組成,它是通過自旋電流實現信息寫入的。目前,STT-MRAM已經從幾家代工廠(GlobalFoundries、英特爾、三星、臺積電和聯電)中脫穎而出,成為一種非常有吸引力的IP選擇。

STT-MRAM具有以下幾個出色的特性:

- 儲存時間長

- 高密度

- 隨機訪問

- 接近零泄漏功率

- 低寫誤碼率

STT-MRAM的開發步驟包括以下幾項:

第一步是材料的堆棧工程——例如,晶體結構、原子組成、厚度和每個層邊界的界面特性。需要通過詳細的“自旋極化”計算確定以下材料特性:

- 磁各向異性 (K)

- 磁飽和 (Ms)

- 隧道磁阻性(TMR)

第二步是擴展電子級、“基態、零K”材料模擬。

第三步是將 MTJ 物理維度引入到工藝開發中。下圖說明了磁性“耦合場”在制造后如何存在于錐形、非完全圓柱形 MTJ 中。

圖源:semiwiki

最后一步是將之前對材料、溫度相關性和 MTJ 尺寸的分析抽象為合適的“緊湊型器件模型”, MRAM陣列設計人員可以用陣列解碼的 SPICE 模型結合位單元存取晶體管、寫入驅動器和讀取傳感設備。

與當前的嵌入式閃存相比,STT-MRAM 在以下幾個方面都具有優勢:

- 耐久性(讀/寫周期數)

- 數據保留(非易失性陣列存儲)

- 讀/寫循環性能

- 成本

所有這些特性優勢都是在嚴格的環境條件下應用,例如-40℃~125℃——對應于帶有eMRAM IP的工業應用SoC。

制造方式實際上也是STT-MRAM優于閃存的點。以臺積電32Mb嵌入式STT-MRAM為例,閃存需要12個或更多額外的掩模,只能在硅基板上實現,并且以頁面模式寫入。由于MTJ器件能夠通過三個左右額外的掩膜嵌入芯片的線路后端(BEOL)互連層,因此STT-MRAM在后段(BEOL)金屬層中實現僅需要2-5個額外的掩模,并且可以以字節模式寫入。

將STT-MRAM與最新的通用存儲候選進行比較,STT-MRAM的讀寫時間分別為2和20 ns,而相變RAM(PRAM)的讀取時間為20~50ns,寫入的時間為30ns。此外,STT-MRAM的耐久性也是要優于PRAM的。

當然STT-MRAM也有自身的一些問題。在基于STT-MRAM的許多應用中,磁場干擾是一個潛在的問題。因此 STT-MRAM 陣列的磁抗擾度 (MI) 是一個新的可靠性參數。在最近的 2021 年 VLSI 研討會上,GLOBALFOUNDRIES 的 MRAM 負責人 Vinayak Bharat Naik 解讀了采用 22FDX-SOI 工藝技術制造的 MRAM 陣列的磁抗擾度實驗分析結果。值得注意的是,該技術還具有非常吸引人的 RF 特性。因此,可能存在帶有電感元件的片上 RF IP,即便這些電感元件會發出顯著的場強。下面看看STT-MRAM對于外部場強和片上場強的反應。

外部場強源自 SoC 封裝之外。Vinayak 展示了應用于 STT-MRAM 測試站點的實驗設置和 MI 分析結果。下圖顯示了(ECC 校正的)存儲器讀寫 BER 為零,活動 MI 大于 250 Oe。

圖源:semiwiki

另外,Vinayak 還強調,MTJ 層內磁化疇的各向異性表明外部磁場和 STT-MRAM 測試點表面之間的入射角可能會影響抗干擾性。

SoC 芯片內的抗磁性能有兩個方面:

- 源自電感線圈的場,例如用于LC諧振電路,導致STT-MRAM錯誤率。

- 源自MTJ陣列本身的場,影響LC槽功能。

Vinayak 分享了分析數據,顯示感應線圈的磁場強度與分離距離的關系,如下所示。右上方的圖表顯示了源自嵌入式 STT-MRAM 陣列的磁場。在示例中,MRAM陣列場非常小,因此對LC諧振回路振蕩頻率的影響可以忽略不計。

圖源:semiwiki

嵌入式MRAM 確實引入了一個新的可靠性問題——陣列對來自 SoC 封裝外部或芯片上電感電路的磁場的“抗擾度”。在制造環節,為了解決磁干擾性問題,制造商選擇在封裝上沉積0.3mm厚的磁屏蔽層。實驗表明在移動設備的商用無線充電器的磁場強度為3500Oe的情況下,暴露100小時的誤碼率可以從> 1E6 ppm降低到1ppm。另外,在650 Oe的磁場下,在125°C下的數據保存時間超過10年。

目前MRAM軟件技術正在世界各地的實驗室中開發,但是隨著STT-MRAM產品成本的降低,無論是嵌入式產品還是獨立產品,MRAM軟件技術都可能成為MRAM取代最快的靜態隨機存取存儲器應用的手段,提供更高的非易失性存儲器密度。

談到應用,STT-MRAM可以在許多嵌入式應用中替代NOR閃存和SRAM。非易失性存儲使用NOR閃存存儲代碼,并將數據傳輸到SRAM充當緩沖區或高速緩存。例如低端手機同時使用NOR和SRAM,可以很容易地用單個STT-MRAM芯片替換它們。

同時,STT-MRAM具有重要的軍事應用,在抗惡劣環境高性能計算機、軍用衛星、導彈、火箭、航天飛行器控制和數據存儲系統中都需要具有超高密度、超大容量、超低能耗、隨機存儲、非易失性、結構簡單、抗輻照能力強等優點的存儲器系統,這些特性STT-MRAM都具備。

本文由電子發燒友編輯整理自公開資料和semiwiki技術文章,轉載請注明!

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

閃存

+關注

關注

16文章

1898瀏覽量

117291 -

存儲

+關注

關注

13文章

4787瀏覽量

90056 -

MRAM

+關注

關注

1文章

250瀏覽量

32912

發布評論請先 登錄

相關推薦

熱點推薦

串行NETSOL自旋轉移扭矩磁阻隨機存取存儲器STT-MRAM

S3A3204R0M是自旋轉移扭矩磁阻隨機存取存儲器(STT-MRAM)。它具有SPI總線接口、XIP(就地執行)功能和基于硬件/軟件的數據保護機制。SPI(串行外設接口)是帶有命令、地址和數據信號

嵌入式開發是否會成為下一個被看好的領域?

聊嵌入式開發會不會成為下一個風口,現在確實是個挺熱門的話題。各種論壇、投資報告都在講物聯網、智能硬件、AIoT的萬億市場,仿佛只要跟嵌入式沾邊,就能乘著東風起飛。但如果套用我們剛才聊的那套邏輯,就會發現,這事兒還真“不好說”,得

NETSOL代理Parallel STT-MRAM系列存儲芯片

STT-MRAM系列存儲芯片,專為需要快速數據存取與長期穩定保存的嚴苛應用而設計,是替代傳統NOR Flash、FeRAM與nvSRAM等方案的理想選擇。

什么是嵌入式應用開發?

系統中,用于控制、監測或通信等特定用途。與一般計算機系統不同,嵌入式系統通常具有較小的存儲容量、處理能力和功耗,且需要滿足特定的實時性、可靠性和安全性要求?。

應用領域

嵌入式系統

發表于 01-12 16:13

BlackBerry QNX與眾森軟件進一步深化戰略合作

今日,深圳市眾森軟件有限公司(以下簡稱"眾森軟件")正式宣布與全球領先的實時操作系統與嵌入式軟件供應商 QNX(BlackBerry有限公司旗下部門QNX)進一步深化戰略合作。此次合作將進一步推動

stt-marm存儲芯片的結構原理

在存儲技術快速演進的今天,一種名為STT-MRAM(自旋轉移矩磁阻隨機存取存儲器)的新型非易失存儲器,正逐步走入產業視野。它不僅繼承了

嵌入式與FPGA的區別

器件的基礎上進一步發展的產物,是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解.決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

FPGA是硬件電路設計,嵌入式是

發表于 11-20 07:12

Everspin串口MRAM芯片常見問題

在嵌入式存儲應用中,串口MRAM芯片憑借其非易失性、高速度及高耐用性受到廣泛關注。作為磁性隨機存儲器技術的代表,Everspin磁性隨機存儲

芯盛智能嵌入式eMMC E210系列斬獲2025年度嵌入式存儲產品金獎

11月18日, 一年一度中國數據與存儲峰會在北京順利召開,備受關注的2025存儲風云榜同期揭曉。作為領先的存儲控制器與解決方案提供商,芯盛智能受邀參會,憑借自主研發的

串行接口MRAM存儲芯片面向工業物聯網和嵌入式系統的應用

、BBSRAM、NVSRAM及NOR存儲器件,專為應對工業物聯網、嵌入式系統及高性能存儲應用的嚴苛需求而設計。旨在通過其高性能、高可靠性及廣泛的適用性,為下一代

MRAM存儲器EMD4E001G-1Gb的優勢介紹

在當今對數據持久性與系統可靠性要求極高的企業基礎設施和數據中心中,Everspin推出的自旋轉移扭矩MRAM(STT-MRAM)存儲器——EMD4E001G-1Gb,憑借其卓越的性能與獨特的技術優勢,成為眾多高性能

VSCode環境下的用PlatformIO IDE進行RISC-V嵌入式開發的方法

簡介:本教程以點亮RV-STAR開發板上的板載LED為目標,從工具安裝開始一步一步詳細介紹了VSCode環境下的用PlatformIO IDE進行RISC-V嵌入式開發的方法

系統環境

發表于 10-20 12:30

Linux嵌入式和單片機嵌入式的區別?

:使用Linux操作系統,可以運行各種復雜的應用程序和驅動程序。

4. 資源需求 :

單片機嵌入式 :對硬件資源的需求較低,通常只需要一個單片機芯片,內存和存儲空間較小。

Linux嵌入

發表于 06-20 09:46

嵌入式超聲電機微步距控制檢測系統設計

摘 要:設計了一種行波超聲電機的嵌入式微步距控制檢測系統,該系統分為三大部分:嵌入式上位機、電機控制器和檢測系統。以 ARM9微控制器作為主控芯片,將Iinux系統和 Qtopia圖形

發表于 06-11 14:43

嵌入式存儲的下一步:STT-MRAM

嵌入式存儲的下一步:STT-MRAM

評論