在 2021 年 6 月的 VLSI 技術和電路研討會上,舉辦了一個關于“面向 2nm-CMOS 和新興存儲器的先進工藝和器件技術”的短期課程。在本文中,我將回顧前兩個介紹前沿邏輯器件的演講。這兩個演示文稿是互補的,并提供了對邏輯技術可能發展的出色概述。

臺積電:未來十年的 CMOS 器件技術

平面 MOSFET 的柵極長度 (Gate length:Lg) 縮放限制在大約 25nm,因為單表面柵極(single surface gate)對亞表面泄漏( sub surface leakage)的控制很差。 添加更多的柵極(例如在 FinFET 中),將使其中的溝道被限制在三個柵極之間,從而能夠將 Lg 縮放到溝道厚度的大約 2.5 倍。FinFET 已經從英特爾最初采用的高度傾斜鰭壁(highly sloped fin walls )的 22 納米發展到今天更加垂直的壁(vertical walls)和臺積電為其 5 納米工藝實施的高遷移率溝道 FinFET。

更高的鰭會增加有效溝道寬度 (effective channel width:Weff),Weff = 2Fh + Fth,其中 Fh 是鰭(Fin)高度,Fth 是鰭(Fin)厚度。增加 Weff 會增加重載電路(heavily loaded circuits)的驅動電流,但過高的鰭會浪費有源功率(active power)。直而薄的鰭片有利于短溝道效應(short channel effects),但 Fw 受到遷移率降低和閾值電壓可變性(threshold voltage variability)增加的限制。在他們的 5nm 技術中實施高遷移率溝道(作者指出,用于 pFET 鰭片的 SiGe)使 TSMC 的驅動電流提高了約 18%。

隨著器件按比例縮小,寄生電阻和電容又將成為一個新問題。CPP(Contacted Poly Pitch)決定標準cell寬度(見圖 1),它是由 Lg、接觸寬度 (Contact Width :Wc) 和墊片厚度 ( Spacer Thickness:Tsp) 組成,CPP = Lg + Wc + 2Tsp。減少 Wc 會增加寄生電阻,除非進行工藝改進以改善接觸,而減少 tsp 會增加寄生電容,除非使用較慢的介電常數間隔物。

Fin depopulation 減少了單元尺寸,增加了邏輯密度并提供了更高的速度和更低的功率,但它確實降低了驅動電流。

從 FinFET 過渡到堆疊的水平納米片 (stacked Horizontal Nanosheets:HNS),通過改變片寬(sheet width:見圖 3)和通過堆疊更多片來增加 Weff 的能力來提高靈活性。

添加sheets與 Weff 相加,Wee = N*2(W+H),其中 N 為sheets的數量,W 為sheets的寬度,H 為sheets的高度(厚度)。最終,sheets的數量受到底部sheets性能的限制。sheets之間的間距隨著寄生電阻和電容的減小而降低,但必須足夠大以使柵極金屬(gate metals)和電介質(dielectric)進入間隙(gap)。在 HNS 堆棧下方有一個底部寄生臺面器件( bottom parasitic mesa device),可以通過注入或介電層進行控制。

在 FinFET 中,nFET 電子遷移率高于 pFET 空穴遷移率。在 HNS 中,遷移率更加不平衡,電子遷移率更高,空穴遷移率更低。可以通過用 SiGe 包覆溝道(cladding the channel )或使用應變松弛緩沖器( Strain Relaxed Buffer)來提高空穴遷移率,但這兩種技術都會增加工藝復雜性。

Imec 引入了一個稱為 Forksheet (FS) 的概念,其中在 nFET 和 pFET 之間放置了一個介電層,從而減少了 np 間距,從而形成了更緊湊的標準單元。

除了具有 FS 的 HNS,還有CFET(Complementary FET ),后者堆疊 nFET 和 pFET,從而無需水平 np 間距。

CFET 選項包括單片集成(monolithic integration),其中的 nFET 和 pFET 器件都制造在同一晶圓上。此外還有順序集成(equential integration),其中的 nFET 和 pFET 制造在單獨的晶圓上,然后結合在一起,這兩種選擇都有多個挑戰仍在研究中。

除了 CFET,演講者還談到了將晶體管集成到后端 (Back End Of Line:BEOL) 互連中的 3D 集成。這些選項需要具有多晶硅溝道(polysilicon channels )或氧化物半導體的低溫晶體管,這會帶來各種性能和集成挑戰。 在前端 (Front End Of Line:FEOL) 中,正在探索 CFET 之外的選項,例如高遷移率材料、隧道 FET (Tunnel FETs:TFET)、負電容 FET (Negative Capacitance FETs:NCFET)、低溫 CMOS (Cryogenic CMOS)和低維材料(dimensional materials)。

低維材料采用納米管或二維材料的形式,這些材料提供比 HNS 更短的 Lg 和更低的功率,但仍處于早期研究階段。低維材料也適用于 HNS/CFET 方法,可選擇堆疊許多層。

IMEC:HNS/FS/CFET 選項

隨著 FinFET 達到極限,鰭變得越來越高、越來越薄、越來越近。鰭片數量減少正在降低驅動電流并增加可變性。

當今最先進的技術是每個設備有 2 個鰭片的 6 軌單元(track cell)。轉向單鰭和更窄的 np 間距將需要新的器件架構來提高性能。

為了繼續 CMOS 縮放,我們需要從 FinFET sot HNS 過渡到具有 FS 和 CFET 的 HNS。

從 FinFET 過渡到 HNS 提供了幾個優勢,大的 Weff,改進的短溝道效應,這意味著更短的 Lg 和更好的設計靈活性,因為能夠改變片寬。

演講者繼續詳細介紹 HNS 處理以及一些挑戰和可能的解決方案。除了四個主要模塊外,HNS 工藝與 FinFET 工藝非常相似。

盡管 HNS 流程類似于 FinFET 流程,但不同的關鍵模塊很困難。釋放蝕刻和實現多個閾值電壓特別困難。關于 HNS 所需的流程模塊更改的細節,有很多很好的信息,這超出了像這樣的評論文章的范圍。沒有明確討論的一件事是,為了將 HNS 工藝擴展到 5 軌單元,需要埋入式電源軌 (Buried Power Rails:BPR),這是另一個仍在開發中的困難工藝模塊。

正如在之前的演示中所見,FS 可以實現 HNS 的進一步擴展。

FS 工藝需要插入介電壁以減小 np 間距。

除了 FS,CFET 通過堆疊器件提供零水平 np 間距。

CFET 對于 SRAM 縮放特別有趣。SRAM 縮放已經放緩并且跟不上邏輯縮放。CFET 提供了將 SRAM 縮放恢復到歷史趨勢的潛力。

如前所述,有兩種 CFET 制造方法,單片和順序。

來源:內容由半導體行業觀察(ID:icbank)編譯自「semiwiki」

責任編輯:lq6

-

CMOS

+關注

關注

58文章

6217瀏覽量

242890 -

電阻

+關注

關注

88文章

5781瀏覽量

179579 -

電容

+關注

關注

100文章

6487瀏覽量

159403 -

存儲器

+關注

關注

39文章

7739瀏覽量

171696

原文標題:關注 | 臺積電談2nm的實現方式

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【案例5.1】存儲器選型的考慮要點

SK海力士在CES 2026展示面向AI的下一代存儲器解決方案

FZH120 一種存儲器交換LED顯示控制的驅動芯片

QSPI PSRAM偽靜態隨機存儲器選型攻略

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

簡單認識高帶寬存儲器

VirtualLab:CMOS傳感器仿真

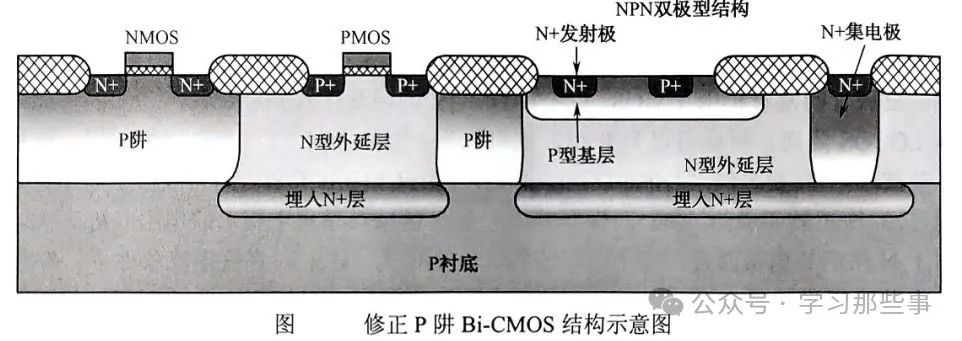

BiCMOS工藝技術解析

VirtualLab:CMOS傳感器仿真

SK海力士僅選擇器存儲器(SOM)的研發歷程

【CW32模塊使用】AT24C02-EEPROM存儲器

一種面向2nm-CMOS和新興存儲器的先進工藝和器件技術

一種面向2nm-CMOS和新興存儲器的先進工藝和器件技術

評論