相應的設計結構和設計內容也變得日益復雜

目前的應用開發速度已無法滿足企業的需求

如何簡化設計進程,提高應用開發效率

成為當下亟需解決的問題

賽靈思 Versal 自適應計算加速平臺的設計方法論

是幫助精簡 Versal 器件設計進程的一整套最佳實踐

遵循這些步驟和最佳實踐進行操作

將有助于以最快且最高效的方式實現期望的設計目標

多計算引擎支持不同系統設計類型

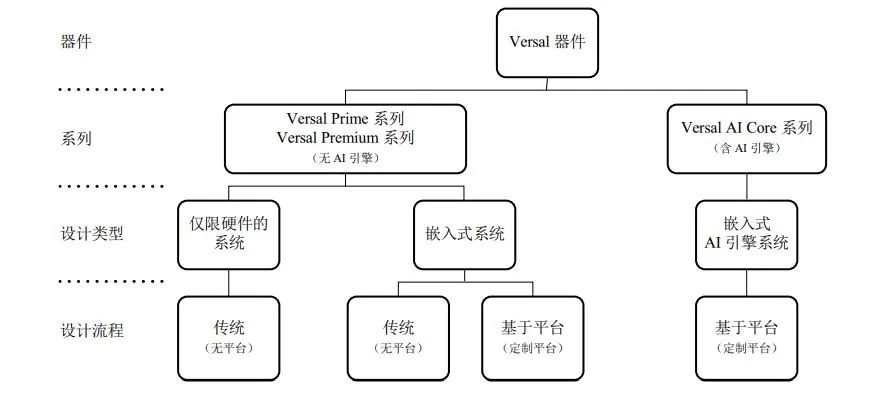

Versal ACAP 屬于異構計算平臺,具有多個計算引擎。在 Versal ACAP 上可映射各種應用,包括對無線系統、機器學習推斷和視頻處理算法進行信號處理。除了多個計算引擎外,Versal ACAP 還可使用高速串行 I/O、片上網絡 (NoC)、 DDR4/LPDDR4 存儲器控制器和多重速率以太網介質訪問控制器 (MRMAC) 來提供超高系統帶寬。Versal 器件分類為 Versal Prime 系列、Premium 系列和 AI Core 系列。

下圖顯示了每種 Versal 器件系列所支持的不同系統設計類型和設計流程。

圖:系統設計類型

適用所有系統的設計流程

系統設計方法論要求基于目標應用明確所有系統要求。其中包括識別具有正確特性(例如,DDRMC IP 數量、AI 引擎 等)的相應 Versal 器件。您還必須考量功耗和發熱要求。選擇相應的器件后,下一步即可著手系統設計,包括在器件上進行目標應用的軟硬件協同設計、系統驗證以及初始化和調試。

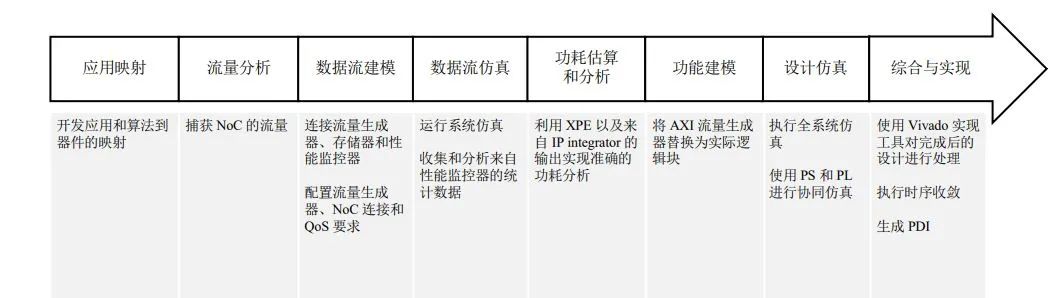

為確保充分利用 Versal ACAP 中可用的多種多樣的計算元件,并使用最高效的實現流程,賽靈思建議采用下圖所示的系統設計方法論流程,此流程適用于所有系統設計類型。

圖:系統設計方法流程

系統設計時的考慮因素

合理可行的設計流程解決方案需要將各種關鍵變量考慮在內,在僅限硬件的系統設計中,關鍵注意事項之一設計中的數據流。通常這些設計都具有下列組件:

? 多個高速 I/O 接口

? 內部數據緩沖和存儲,具有由片上 RAM 和外部 DDR 存儲器組成的存儲器層級

? 內部數據處理邏輯

對于能夠處理外部和內部流量帶寬和時延要求的設計,為其創建 DDRMC-NoC 配置至關重要。賽靈思建議先執行流量分析以評估并最終明確流量,然后再繼續執行設計的整體集成和實現階段。除此以外,報告中還涵蓋了嵌入式系統設計值得考量的特殊注意事項,根據隨附的是嵌入式系統還是服務器系統,每個步驟所面臨的難題也不盡相同。

編輯:jq

-

存儲器

+關注

關注

39文章

7738瀏覽量

171659 -

數據

+關注

關注

8文章

7335瀏覽量

94760 -

RAM

+關注

關注

8文章

1399瀏覽量

120550 -

DDR

+關注

關注

11文章

755瀏覽量

69106 -

AI

+關注

關注

91文章

39774瀏覽量

301372

原文標題:用戶指南 | Versal ACAP:精簡設計進程的最佳實踐

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

手機主板散熱導熱膠薄層涂布最佳實踐 |鉻銳特實業

BMS設計中如何選擇MOSFET——關鍵考慮因素與最佳實踐

長電科技榮獲2025年上市公司可持續發展最佳實踐案例

立訊精密榮獲2025年上市公司可持續發展最佳實踐案例

思瑞浦獲評“2025年上市公司董事會最佳實踐案例”

愛芯元智榮獲2025金輯獎最佳技術實踐應用獎

安波福榮獲2025年度最佳實踐獎之產品領導力大獎

AMD Versal自適應SoC內置自校準的工作原理

達實智能榮獲中國企業管理“十大最佳實踐”獎

生產環境中Kubernetes容器安全的最佳實踐

Linux網絡管理的關鍵技術和最佳實踐

AMD第二代Versal AI Edge和Versal Prime系列加速量產 為嵌入式系統實現單芯片智能

Versal 600G DCMAC Subsystem LogiCORE IP產品指南

適用于Versal的AMD Vivado 加快FPGA開發完成Versal自適應SoC設計

Versal ACAP:精簡設計進程的最佳實踐

Versal ACAP:精簡設計進程的最佳實踐

評論