到目前為止,在市場上有三種基于臺(tái)積電N5工藝的產(chǎn)品:Mate 40 Pro中的華為麒麟9000 5G SoC, iPhone 12系列中的蘋果A14 SoC,以及新的MBA/MBP和Mac Mini中的蘋果M1 SoC,現(xiàn)在這個(gè)列表中又新添一名成員,它就是基于臺(tái)積電5nm制程工藝 112G SerDes連接芯片。近日,Marvell宣布了其基于DSP的112G SerDes解決方案的授權(quán)。

現(xiàn)代網(wǎng)絡(luò)基礎(chǔ)架構(gòu)依賴于高速的 SerDes 連接,并且能夠以各種速率在不同協(xié)議下工作,代表性的有以太網(wǎng)、光纖、存儲(chǔ)和連接結(jié)構(gòu)。此前的產(chǎn)品已支持高達(dá) 56G 的連接,但最新 IP 已支持將它翻倍。盡管 Marvell 并不是第一家提供 112G 連接方案的廠商,但卻是首個(gè)實(shí)現(xiàn)了通過硬件驗(yàn)證和授權(quán) 5nm 制程的企業(yè)。

有大量數(shù)據(jù)顯示與其它112G解決方案相比,其不僅滿足各種標(biāo)準(zhǔn)、還具有更低的能耗和錯(cuò)誤率,特別是對(duì)高速、高可靠性的基礎(chǔ)架構(gòu)應(yīng)用有相當(dāng)實(shí)際的意義。Marvell 宣稱,其新方案可顯著降低每比特位傳輸?shù)哪芎模噍^于基于臺(tái)積電 7nm 工藝(N7)的競品低了 25%,并且具有嚴(yán)格的功率 / 熱功耗限制、以及大于 40dB 的插入損耗。

通常數(shù)據(jù)支持基于一系列 0 或 1 操作位的 NRZ 調(diào)制,但 Marvell 啟用了 2 比特位的操作(00、01、10 或 11),又稱 PAM4 脈沖幅度調(diào)制。這樣可讓帶寬輕松翻倍,但也確實(shí)需要一些額外的電路。,PAM4以前在較低的SerDes速度和112G時(shí)已經(jīng)啟用,但在TSMC N5上卻沒有使用。當(dāng)我們使用更快的速度時(shí),PAM4將成為支持它們的必要條件。普通讀者可能會(huì)發(fā)現(xiàn),NVIDIA的RTX 3090使用了基于 7nm 工藝的 PAM4 信號(hào)調(diào)制,可讓美光 GDDR6X 閃存芯片提供超過 1000 GB/s 的帶寬。如有必要,還可以過在NRZ模式下運(yùn)行,以獲得更低的功耗。

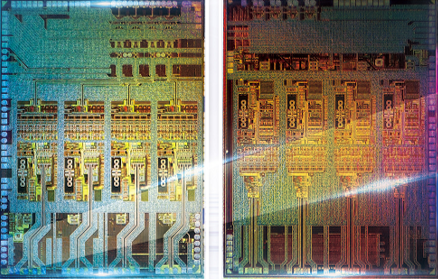

圖片來自美光公司

Marvell表示,該公司已經(jīng)與多個(gè)市場的ASIC定制客戶合作實(shí)施112G方案部署。該公司表示,除了新的112G SerDes外,還將推出一整套基于5nm的PHY、交換機(jī)、DPU、定制處理器、控制器和加速器,而這只是第一步。

原文標(biāo)題:Marvell發(fā)布基于臺(tái)積電5nm制程工藝 112G SerDes連接芯片

文章出處:【微信公眾號(hào):ssdfans】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

芯片

+關(guān)注

關(guān)注

463文章

54305瀏覽量

468432 -

臺(tái)積電

+關(guān)注

關(guān)注

44文章

5806瀏覽量

176956

原文標(biāo)題:Marvell發(fā)布基于臺(tái)積電5nm制程工藝 112G SerDes連接芯片

文章出處:【微信號(hào):SSDFans,微信公眾號(hào):SSDFans】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

2nm“諸神之戰(zhàn)”打響!性能飆升+功耗驟降,臺(tái)積電攜聯(lián)發(fā)科領(lǐng)跑

今日看點(diǎn):臺(tái)積電敦促客戶預(yù)訂 2nm 制程產(chǎn)能;廣州再添兩大百億級(jí)半導(dǎo)體項(xiàng)目

1.4nm制程工藝!臺(tái)積電公布量產(chǎn)時(shí)間表

全球首款4×112G 算力中心模擬CDR電芯片由上海米硅突破!

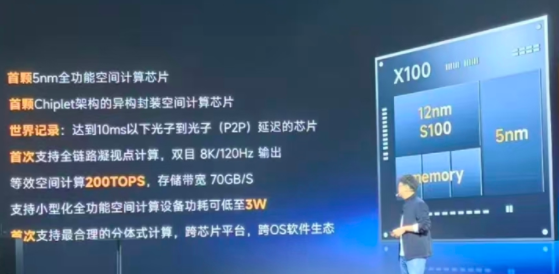

中國首顆全功能空間計(jì)算芯片發(fā)布 極智G-X100 5nm工藝

基于TE Connectivity QSFP-DD 112G連接器數(shù)據(jù)手冊(cè)的技術(shù)解析

TE Connectivity QSFP 112G SMT連接器與屏蔽罩技術(shù)解析

臺(tái)積電2納米制程試產(chǎn)成功,AI、5G、汽車芯片,誰將率先受益?

臺(tái)積電2納米制程試產(chǎn)成功,AI、5G、汽車芯片

看點(diǎn):臺(tái)積電2納米N2制程吸引超15家客戶 英偉達(dá)擬向OpenAI投資1000億美元

臺(tái)積電2nm工藝突然泄密

貿(mào)澤即日起開售適用于數(shù)據(jù)中心和網(wǎng)絡(luò)應(yīng)用的 全新TE Connectivity QSFP 112G SMT連接器

晟聯(lián)科受邀出席臺(tái)積電技術(shù)研討會(huì),高速接口IP組合及解決方案助推海量數(shù)據(jù)暢行

基于臺(tái)積電5nm制程工藝 112G SerDes連接芯片發(fā)布

基于臺(tái)積電5nm制程工藝 112G SerDes連接芯片發(fā)布

評(píng)論