異構 3D 系統(tǒng)級封裝集成

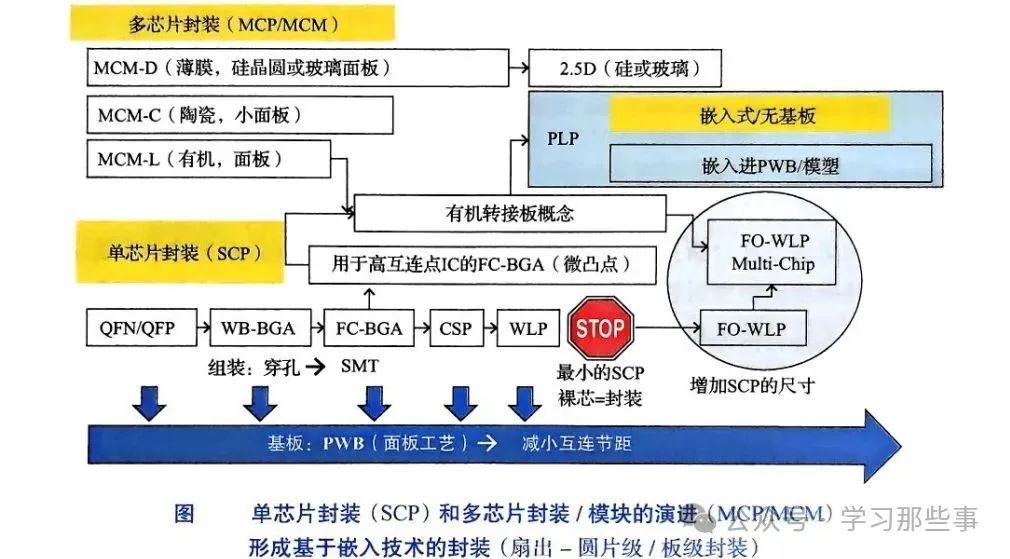

3D 集成與封裝技術的進步使在單個封裝(包含采用多項技術的芯片)內構建復雜系統(tǒng)成為了可能。

過去,出于功耗、性能和成本的考慮,高級集成使用單片實施。得益于封裝與堆疊技術的創(chuàng)新,設計人員可以將他們的系統(tǒng)集成至單個封裝內,封裝內的芯片通過精選的制程技術來優(yōu)化特定功能。

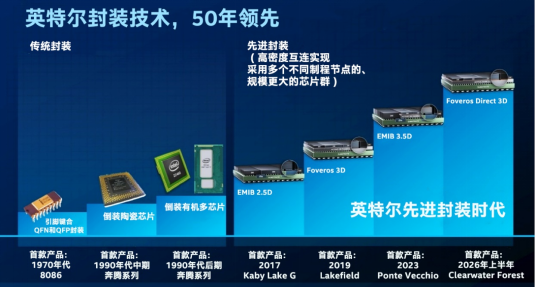

新興系統(tǒng)要求極高的互聯(lián)帶寬和極小的接口功耗/位。為了實現(xiàn)它,英特爾提供了兩個關鍵要素 - 超短程接口標準和 3D 集成封裝技術。

高級接口總線 (AIB)

英特爾高級接口總線 (AIB) 是一個管芯到管芯 PHY 級標準,支持使用芯片知識產權 (IP) 模塊庫以模塊化的方式進行系統(tǒng)設計。

AIB 使用類似于 DDR DRAM 接口的前向時鐘并行數(shù)據(jù)傳輸機制。AIB 獨立于制程與封裝技術,如英特爾嵌入式多管芯互連橋接 (EMIB) 或 TSMC 的 CoWoS。

目前,英特爾提供了 AIB 接口免版稅許可,以支持廣泛的芯片生態(tài)系統(tǒng)、設計方法或服務提供商、代工廠、封裝和系統(tǒng)廠商。

合理的異構系統(tǒng)級封裝 (SiP) 示例,結合了傳感器、專有 ASIC、FPGA、CPU、內存和將 AIB 用作 chiplet 接口的 I/O

使用 EMIB 的多管芯集成

英特爾 產品使用創(chuàng)新的嵌入式多管芯互聯(lián)橋接 (EMIB) 封裝技術,異構集成模擬設備、內存、CPU、ASIC 芯片以及單片 FPGA 架構。英特爾 FPGA 系統(tǒng)級封裝 (SiP) 技術旨在提供能在單個封裝內高效混合功能和/或制程節(jié)點的產品。這些新產品類別滿足了目前以及未來的系統(tǒng)功能要求,包括:

提升性能/帶寬

使用 AIB 和 EMIB 集成 SiP,實現(xiàn)了芯片間最高的互聯(lián)密度。其結果是實現(xiàn)了 SiP 組件之間的高帶寬連接。而且,與外部通信的用戶信號使用標準 FCBGA 走線,從而改善了信號和電源完整性。

低功耗

配套芯片組的位置彼此相鄰,因此,互聯(lián)走線非常短。這實現(xiàn)了較低的功耗/位。

小外形封裝

能夠在單個封裝內異構集成組件,減小了外形。這幫助用戶節(jié)省了寶貴的電路板空間,減少了電路板層和物料清單 (BOM) 成本。

更高的靈活性、可擴展性和易用性

由于組件已經(jīng)集成在封裝中,因此,SiP 有助于在 PCB 層面上降低布線復雜度。此外,SiP 提高了在芯片技術中采用不同管芯尺寸的能力。結果是非常靈活的可擴展解決方案,而且使用非常方便。

加快產品上市速度

SiP 能夠集成已經(jīng)成熟的技術,在產品型號中重新使用常用設備或者邏輯塊,從而促使產品及時面市。這節(jié)省了寶貴的時間和資源,從而幫助客戶盡快將其產品推向市場。

原文標題:輕松降低PCB布線復雜度,這個多管芯集成技術大幅提升新品上市速度

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1660文章

22411瀏覽量

636265 -

pcb

+關注

關注

4404文章

23877瀏覽量

424233 -

英特爾

+關注

關注

61文章

10301瀏覽量

180432

原文標題:輕松降低PCB布線復雜度,這個多管芯集成技術大幅提升新品上市速度

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

銳寶智聯(lián)入選英特爾首批尊享級合作伙伴

吉方工控獲評英特爾首批尊享級合作伙伴

英特爾288核新至強處理器揭秘:Intel 18A制程,3D堆疊與鍵合,EMIB封裝……

英特爾先進封裝,新突破

英特爾發(fā)布全新GPU,AI和工作站迎來新選擇

英特爾以系統(tǒng)級代工模式促進生態(tài)協(xié)同,助力客戶創(chuàng)新

英特爾持續(xù)推進核心制程和先進封裝技術創(chuàng)新,分享最新進展

英特爾代工:明確重點廣合作,服務客戶鑄信任

英特爾先進封裝:助力AI芯片高效集成的技術力量

英特爾異構3D系統(tǒng)級封裝集成

英特爾異構3D系統(tǒng)級封裝集成

評論