功耗是芯片制造工藝演進時備受關注的指標之一。比起7nm工藝節點,5nm工藝可以使產品性能提高15%,晶體管密度最多提高1.8倍。三星獵戶座1080、華為麒麟9000、驍龍888和蘋果的A14芯片都采取了5nm工藝制程。然而,5nm手機芯片功耗過高的問題卻于近期被媒體頻頻報道。這也不禁令人產生質疑:先進制程是否只是噱頭?芯片廠商是否還有必要花費高價和大量時間,在芯片先進制程方面持續進行研發和投入?

先進制程只是噱頭?

數據顯示,28nm工藝的設計成本為0.629億美元。隨著制程工藝的推進,芯片的設計成本迅速上升。7nm工藝節點的成本暴增至3.49億美元,5nm工藝所需成本更是高達4.76億美元。另有數據顯示,臺積電每片5nm晶圓的代工費用約為17000美元,這一數字幾乎是7nm芯片所需費用的兩倍。因為成本的壓力,許多晶圓代工廠無法參與到先進制程工藝的賽道。目前,具備先進制程芯片生產能力的代工廠,僅有臺積電、三星和英特爾三家。然而,高昂的付出卻仍然無法解決功耗問題,先進制程工藝是否只是噱頭?

“手機芯片的制程數值越小,意味著芯片晶體管尺寸進一步微縮,芯片中元器件的排列也更加密集。這使得單位面積內,芯片可集成的晶體管數目增多。此次手機芯片制程由7nm提升至5nm,使得芯片上集成的晶體管數目得到顯著提升。以華為麒麟9000芯片為例,和上一代采用7nm工藝制程的麒麟990(5G版)相比,華為麒麟9000的晶體管數目足足多了50億,總數目提高至153億。晶體管數目越多,芯片相應的運算和存儲能力也就越強,這使得芯片在程序運行加載速度、數據處理性能等方面都獲得了較為顯著的提升。除此之外,5nm手機SoC芯片更強調5G能力,5G基帶芯片的集成使其在通信性能方面獲得了明顯提升。”復旦大學微電子學院教授周鵬向記者說道。

隨著摩爾定律的發展,半導體產業本身就是一部關于創新的著作,里面凝聚了許多迭代創新的技術,當然也包括了試錯的過程。周鵬認為,5nm技術節點是目前先進半導體技術的集大成者。現階段,5nm技術才剛推出第一代工藝,它所面對的問題主要源于工藝的不穩定性。在每一代工藝節點的研發中,新產品都會面臨類似的問題,這種問題的解決還需要更多研發時間的投入和技術上的改進迭代。

Gartner研究副總裁盛凌海也指出,任何新的工藝都需要有一個磨合期。隨著技術的更新迭代,出現的問題將得到解決。手機芯片剛剛開啟5nm時代,推出5nm手機芯片的廠商成為第一批“吃螃蟹的人”。然而,沒有吃到“螃蟹黃”,并不意味著“螃蟹肉”就不夠鮮美。隨著時間的推移和技術的演進,5nm芯片會體現更多優勢,讓諸多手機廠商吃到“螃蟹黃”。

為何會出現功耗問題?

為何采用先進工藝制造的芯片產品容易出現功耗問題?周鵬介紹,目前的芯片產品越來越追求高性能,功耗的增加主要來源于“漏電”這一不可控現象。他表示,構成芯片的基本單元——晶體管可被視為一個控制電流的電子開關。它可以把功耗分成兩部分,即靜態功耗和動態功耗。動態功耗是指在開關過程中產生的功耗,而靜態功耗是指開關在關閉時,泄漏電流產生的功耗。如今5nm手機芯片出現功耗過高的問題,主要是泄漏電流導致的靜態功耗增加。

為提高芯片的性能,就需要把電子開關對電流通斷的控制能力提高,以加快開關的速度。這意味著,開關要在更小尺寸的情況下通過更大的電流。開關的尺寸越小,對制備工藝的要求就越高,這使得開關在關閉狀態下,會有更多泄露電流。這部分產生的功耗是不可控的,是否產生功耗將直接由工藝的穩定性決定。要想使產品的性能提升,就需要更小的芯片制程,而芯片制程越小,就會為制造工藝帶來更大的挑戰。由于難以保障工藝的穩定性,漏電現象會愈發明顯,功耗也會變大。

也有聲音稱,此次5nm芯片出現功耗問題,意味著FinFET工藝結構將不再適用于5nm芯片制程。用于3nm工藝節點的GAA工藝結構,有望提前被用在5nm芯片中。

自英特爾于2011年首次推出基于FinFET結構的22nm工藝以來,FinFET工藝結構已經在先進集成電路芯片中應用了十年。周鵬介紹,FinFET結構的提出是為了克服平面MOSFET結構下,由于源極和漏極越來越近、氧化物越來越薄所導致的漏電問題。它的優勢主要體現在兩個方面。一方面是可以使晶體管在更小的平面結構尺寸下,緩解漏電的問題;另一方面則是將晶體管的結構形態從二維層次突破到三維空間,提高了芯片的空間利用率。提出該結構的最終目的,是為了在單位面積內塞入更多的晶體管。

然而,隨著技術節點的進一步推進,FinFET結構也面臨越來越大的困難與挑戰。該結構的制備工藝十分復雜,會給工藝的穩定性方面帶來一定困擾,使漏電問題無法得到有效保障。相比于三面圍柵的FinFET結構,GAA技術采用的四面環柵結構,可以更好地抑制漏電流的形成和驅動電流的增大,更有利于實現性能和功耗之間的平衡。

但是,周鵬也指出:“工藝的不穩定問題對GAA結構來說也同樣存在,GAA和FinFET結構要解決的都是漏電問題。實現GAA工藝的難度并不比FinFET小,它的發展也需要一個技術改進的過程。GAA結構是在先進制程領域被普遍看好的工藝結構。但就目前5nm技術節點來說,不采用FinFET而采用GAA,仍是一個值得商榷的問題,畢竟GAA工藝也需要遵循一定的發展規律。”

摩爾定律將持續演進

芯片的制程越來越小,需要攻克的技術難點就越來越多,成本會變得越來越高昂,但這并不意味著摩爾定律將失效。芯片的制造工藝仍將不斷向更高制程演進。

對此,周鵬認為,芯片制程將跟隨摩爾定律的腳步不斷發展。盡管在發展的過程中,會面臨更多技術、成本帶來的問題,但是人們對芯片性能的追求已經超過了經濟成本的范疇。“在芯片發展的早期,人們面對的是一個經濟問題。這是因為集成電路芯片在發展初期,是一種需要盡快普及和應用的商業化產品,成本是其大規模應用和推廣時要面對的主要問題。每隔一段時間,單位面積的晶體管數量倍增,帶來的直接效應就是成本顯著降低。這推動了芯片的廣泛使用。尺寸微縮帶來的性能提升和功耗降低,也是為降低生產成本服務的。隨著芯片滲透至人類生活的方方面面,它已經不是可有可無的商品,而是一個必需品。人們對芯片的依賴程度越來越高,所以對芯片性能的要求已慢慢超過了對經濟成本的要求。人們愿意花更多的錢去體驗更好的性能。隨著技術天花板的到來,人們對性能的追求超過了經濟成本的范疇。”周鵬說道。

同時,周鵬認為,隨著芯片制程發展至5nm節點以下,晶體管溝道長度將進一步縮短,晶體管中電荷的量子遂穿效應將更容易實現。這些不受控制的隧穿電荷,將導致晶體管產生較大的漏電流,進而使得芯片的功耗問題變得更加嚴重。

當然,這些也不是無法攻克的難題。在未來的技術發展中,為了能夠更好地控制芯片功耗,具有更強溝道電流控制能力的GAA結構,將受到更多重視。事實上,早在三年前,三星便表示將在3nm制程中引入GAA技術,并計劃于2022年正式量產。臺積電也于去年宣稱,其在2nm制程研發中有重大突破,將選擇切入GAA技術。這些都能說明GAA技術在5nm節點之后的更小的制程中,會受到業界的普遍認可和青睞。

“但值得注意的是,在半導體領域當中,任何一種技術的迭代更新都需要經歷多年的試錯和改進。GAA結構雖然在5nm以下制程中具有較為明顯的優勢,但它是否能實現預期的高性能和低功耗,還要看其制程中面臨的技術難題能否被一一攻克。”周鵬說道。

芯片還將向更先進制程發展。只要將足夠的時間留給新技術去更新迭代,很多問題都會迎刃而解。

責任編輯:tzh

-

芯片

+關注

關注

463文章

54305瀏覽量

468420 -

半導體

+關注

關注

339文章

31114瀏覽量

265940 -

晶體管

+關注

關注

78文章

10428瀏覽量

148373 -

5G

+關注

關注

1368文章

49199瀏覽量

634329

發布評論請先 登錄

估值700億,國產智能手機芯片第一股沖擊IPO!

小米自研3nm旗艦SoC、4G基帶亮相!雷軍回顧11年造芯路

三星發布Exynos 2600,全球首款2nm SoC,NPU性能提升113%

純硬件開關機芯片GEK100系列,不用擔心死機問題的開關機芯片,及一鍵開關機芯片的發展趨勢分析

1600TOPS!美國新勢力車企自研5nm芯片,轉用激光雷達硬剛特斯拉

為什么單片機芯片上需要多組VDD?

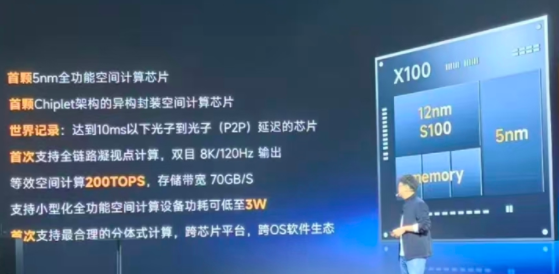

國內首顆5nm MR芯片問世: Chiplet架構、9ms P2P延遲打破紀錄

曝三星S26拿到全球2nm芯片首發權 三星獲特斯拉千億芯片代工大單

手機芯片:從SoC到Multi Die

今日看點丨蔚來自研全球首顆車規5nm芯片!;沃爾沃中國區啟動裁員計劃

AI?時代來襲,手機芯片面臨哪些新挑戰?

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現流片成功

5nm手機芯片功耗過高?

5nm手機芯片功耗過高?

評論