AMD的RX 6000系列顯卡用上了7nm RDNA2架構,能效比再次提升50%,性能也摸到了RTX 3090的水平,而今天預計會推出RDNA3架構顯卡了。

RDNA3架構會有什么樣的改進?性能、能效提升是可以預期的,關鍵是怎么做到?日前有傳聞稱AMD申請了小芯片chiplets架構設計的專利,有可能是用于RDNA3架構顯卡的。

AMD的思路是利用“高帶寬被動交聯”(high bandwidth passive crosslink)來解決這些障礙,將第一個GPU小芯片與CPU處理器直接耦合在一起(communicably coupled),而其他GPU小芯片都通過被動交聯與第一個GPU小芯片耦合,而所有的GPU小芯片都放置在同一個中介層(interposer)之上。

簡單來說,GPU如果用上這種小芯片架構設計,那么GPU的運算核心也可以跟IO核心分離,類似Zen2/Zen3上那樣,運算單元就可以堆更多核心。

考慮到RDNA2的流處理器單元都已經8192個了,AMD通過小芯片架構來堆疊1萬以上的核心更容易了,畢竟這個方向是繞不過的。

GPU使用小芯片架構有利有弊,設計當然會復雜,但是考慮到未來的先進工藝越來越貴,制造單一大核心芯片成本居高不下,所以外媒稱AMD采用小芯片GPU方案的一個目的就是省錢——不用制造大核心GPU芯片了,良率大幅提升,經濟性更好,這條路已經在Zen2、Zen3上成功驗證了。

責任編輯:PSY

-

芯片

+關注

關注

463文章

54010瀏覽量

466053 -

amd

+關注

關注

25文章

5684瀏覽量

139968 -

顯卡

+關注

關注

16文章

2520瀏覽量

71503 -

芯片堆疊

+關注

關注

0文章

19瀏覽量

14879

發布評論請先 登錄

LCD液晶面板激光修復工藝助力制程良率提升

晶圓級封裝良率提升方案:DW185半導體級低黏度晶圓助焊劑

國產芯片真的 “穩” 了?這家企業的 14nm 制程,已經悄悄滲透到這些行業…

線路板 PCBA 生產效率和良率有哪些提高方式?

華大九天Vision平臺重塑晶圓制造良率優化新標桿

廣立微DE-YMS系統助力紫光同芯良率管理

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

屹立芯創半導體除泡技術:提升先進封裝良率的關鍵解決方案

廣立微YAD貫穿全鏈路良率診斷分析

三星在4nm邏輯芯片上實現40%以上的測試良率

99.99%良率的秘密!華頡AOI如何破解汽車電子Pin針檢測難題?

臺積電2nm制程良率已超60%

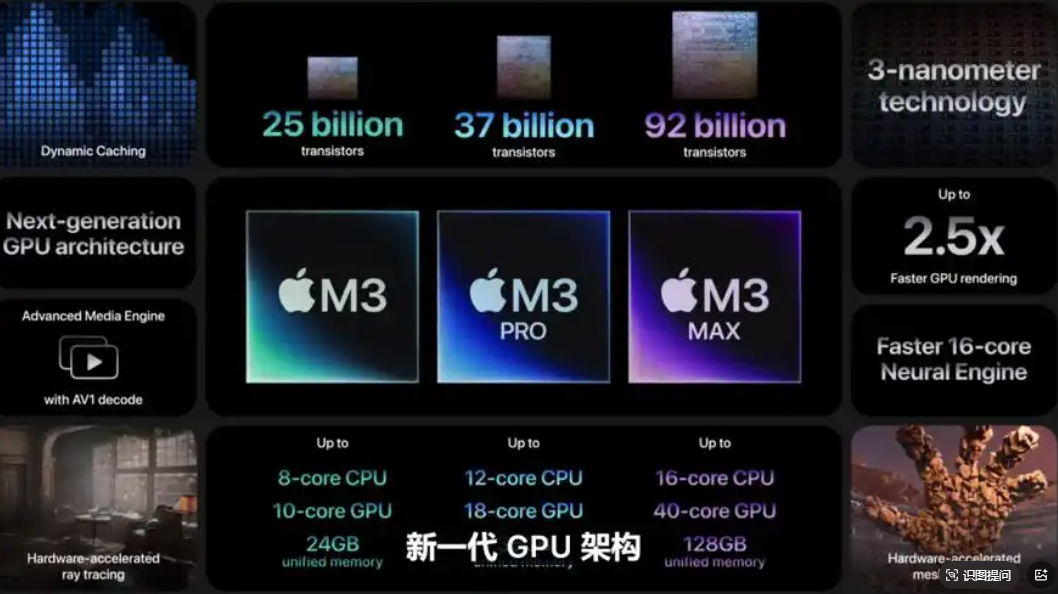

M3 Ultra 蘋果最強芯片 80 核 GPU,32 核 NPU

RDNA3顯卡或使用小芯片堆核 良率大幅提升

RDNA3顯卡或使用小芯片堆核 良率大幅提升

評論