IC Compiler II作為新思科技Fusion Platform的一部分,憑借其行業領先的容量和吞吐量,加速了超大規模Colossus IPU的實現,該IPU擁有超過590億個晶體管

RTL-to-GDS流程為AI硬件設計所需的創新優化技術提供了最佳性能、功耗和面積(PPA)

集成式黃金簽核技術通過零裕度流程提供了可預測且可收斂的融合設計

新思科技(Synopsys)近日宣布,其行業領先的IC CompilerII布局布線解決方案成功協助Graphcore實現第二代Colossus MK2 GC200智能處理單元(IPU)芯片的一次性流片成功。該IPU采用了業界先進的7nm工藝技術,集成594億個晶體管。新思科技IC Compiler II擁有針對AI硬件設計的超高容量架構和創新技術,其RTL-to-GDS流程與最先進的功耗優化能力,以及PrimeTime延遲計算器等嵌入式黃金簽核技術,為Graphcore設計團隊提供了優越的PPA和最快的設計收斂時間,從而加快了Graphcore大規模AI處理器設計的實現。

“新思科技的數字全流程解決方案(包括Design Compiler和IC Compiler II在內的業界一流RTL-to-GDS工具)提供了單一供應商所能提供的最全面設計平臺,這對我們最新的Colossus IPU按時流片至關重要。與新思科技的長期合作使我們能夠利用IC Compiler II的最前沿技術,實現先進AI處理器的性能與功率目標。我們相信,基于與新思科技在IC Compiler II和Fusion Compiler上的持續合作,我們將不斷拓展機器智能計算的極限。”

——Graphcore

硅業務副總裁

Phil Horsfield

Graphcore推出的第二代Colossus GC200 IPU是一款精密芯片,集成了1472個獨立處理器核和超過900兆字節的片上存儲,為數據中心規模的AI應用提供卓越的并行處理能力。新思科技的IC Compiler II擁有適配AI設計的多項功能,其頂級互連規劃、邏輯重構、擁塞驅動的mux優化、全流程并發時鐘以及數據優化,為復合AI加速芯片中典型的高度重復、基于MAC的拓撲,提供了同類設計的最佳PPA。

此外,它還具有自適應抽象化和分布式實現的原生高容量數據模型,可以在快速周轉時間內高效處理數十億個實例設計。IC Compiler II具有獨特的最終簽發引擎主干,可提供最高的相關性和超高度收斂的設計,從而進一步加快設計周轉時間。

“AI計算的設計復雜性極限正在不斷被突破,比如Graphcore最新推出的Colossus IPU,它成功利用了IC CompilerII中最新的AI優化技術,同時滿足了最復雜芯片的多個設計目標,這進一步鞏固了作為下一代AI設計首選布局布線工具的領先地位。”

——Neeraj Kaul

工程設計事業部副總裁

新思科技

責任編輯:lq

-

處理器

+關注

關注

68文章

20255瀏覽量

252338 -

晶體管

+關注

關注

78文章

10396瀏覽量

147774 -

AI芯片

+關注

關注

17文章

2128瀏覽量

36783

原文標題:594億顆晶體管的7nm工藝AI芯片,一次性流片成功的王牌武器—ICCII

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

技術報告 | Gate 和 Fin Space Variation 對應力調制及 FinFET 性能的影響

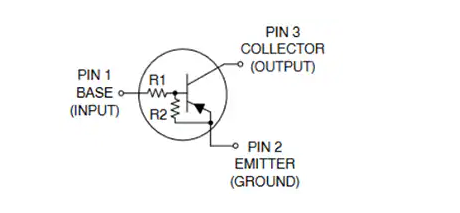

深入解析onsemi偏置電阻晶體管(BRT)NSBAMXW系列技術特性與應用

業界先進的7nm工藝技術,集成594億個晶體管

業界先進的7nm工藝技術,集成594億個晶體管

評論