文章來(lái)源:學(xué)習(xí)那些事

原文作者:前路漫漫

本文介紹了晶體管是什么。

概述

隨著集成電路科學(xué)與工程的持續(xù)發(fā)展,當(dāng)前集成電路已涵蓋二極管、晶體管、非易失性存儲(chǔ)器件、功率器件、光子器件、電阻與電容器件、傳感器件共 7 個(gè)大族,衍生出 100 多種不同類型的器件,推動(dòng)集成電路技術(shù)滲透到人們衣食住行的各個(gè)領(lǐng)域。本章將圍繞集成電路的核心器件 —— 晶體管展開,闡述其如何憑借優(yōu)異性能與不斷演進(jìn)的結(jié)構(gòu),成為信息時(shí)代不可或缺的重要推動(dòng)力。

1947 年 12 月,美國(guó)貝爾實(shí)驗(yàn)室成功演示了首個(gè)具有放大功能的點(diǎn)接觸鍺晶體管,這一成果標(biāo)志著影響全人類生產(chǎn)與生活的半導(dǎo)體產(chǎn)業(yè)正式誕生,也開啟了信息時(shí)代的大門。晶體管是 20 世紀(jì)最重要的發(fā)明之一,其英文名稱 “Transistor” 源于 “Transfer-resistor” 的縮寫,意為 “轉(zhuǎn)換電阻器” 或 “跨阻器”。本節(jié)將簡(jiǎn)要介紹晶體管器件的相關(guān)基礎(chǔ)知識(shí)點(diǎn)。

晶體管的基本功能

相較于早期的電子管,晶體管具有功耗低、壽命長(zhǎng)、性能可靠等顯著優(yōu)勢(shì);基于晶體管發(fā)展的集成電路技術(shù),在體積、成本與可靠性方面具備其他技術(shù)難以比擬的優(yōu)勢(shì),因此迅速取代電子管在電子系統(tǒng)中的核心地位。

與電子管類似,晶體管在電子系統(tǒng)中主要承擔(dān) “增益” 與 “開關(guān)” 兩大核心作用:

增益:當(dāng)向晶體管施加一個(gè)隨時(shí)間變化、幅值為 V?的電壓信號(hào)時(shí),可輸出一個(gè)隨時(shí)間變化、幅值為 V?的電壓信號(hào)。定義電壓增益 A?為 A? = V? / V?,該定義同樣適用于電流增益(如 A? = I? / I?)或功率增益(如 A? = P? / P?)。顯然,增益(或損耗)本身是無(wú)量綱的,但為方便實(shí)際應(yīng)用,常以分貝(dB)作為計(jì)量單位。

開關(guān):晶體管的關(guān)閉與打開狀態(tài),分別對(duì)應(yīng)數(shù)字二進(jìn)制中的邏輯 “0” 與邏輯 “1”。晶體管的增益特性,能讓每一次邏輯運(yùn)算過程實(shí)現(xiàn)有效再生放大 —— 即便信號(hào)經(jīng)過數(shù)百萬(wàn)個(gè)晶體管邏輯門傳遞,仍可保持信號(hào)幅值高于背景噪聲水平。由于微處理器需集成上億個(gè)晶體管,即便單個(gè)晶體管的損耗極小,累積損耗也會(huì)導(dǎo)致信號(hào)嚴(yán)重失真,因此晶體管的開關(guān)特性與增益特性共同構(gòu)成了超大規(guī)模集成電路的技術(shù)基石。

相較于機(jī)械開關(guān),晶體管具有響應(yīng)速度快、動(dòng)作準(zhǔn)確性高的優(yōu)勢(shì),是放大電路、開關(guān)電路、穩(wěn)壓電路、信號(hào)調(diào)制電路及振蕩器等各類數(shù)字與模擬電路的基礎(chǔ)器件。此外,晶體管的改型器件也是其他集成電路器件大族的核心基礎(chǔ),例如非易失性存儲(chǔ)器(NVM)中的浮柵金屬 - 氧化物 - 半導(dǎo)體場(chǎng)效應(yīng)晶體管(FGMOSFET)、功率器件中的絕緣柵雙極型晶體管(Insulated Gate Bipolar Transistor,IGBT)等。

晶體管的基本結(jié)構(gòu)

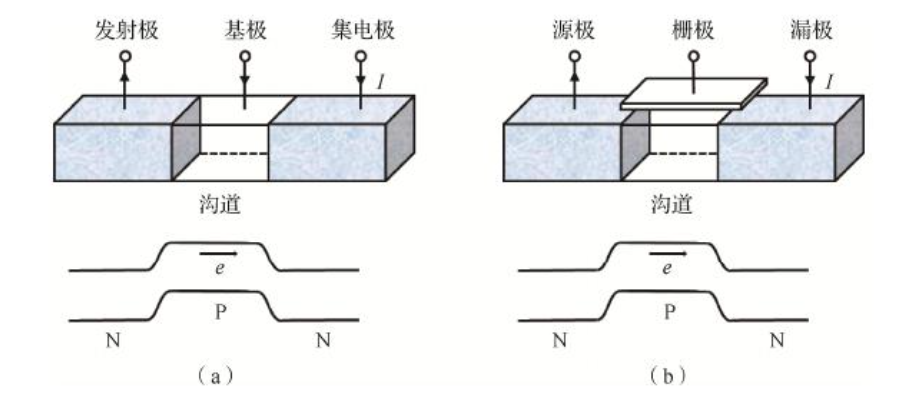

晶體管的基本結(jié)構(gòu)特征是 P 型與 N 型半導(dǎo)體區(qū)域交替排布,并在區(qū)域之間形成導(dǎo)電溝道(簡(jiǎn)稱 “溝道”)。借助輸入信號(hào)調(diào)控溝道內(nèi)電流的 “導(dǎo)通” 與 “截止” 狀態(tài),可分別對(duì)應(yīng)二進(jìn)制邏輯中的 “1” 與 “0”。從結(jié)構(gòu)與工作原理劃分,晶體管主要分為兩大族:勢(shì)效應(yīng)晶體管(Potential-Effect Transistor,PET)與場(chǎng)效應(yīng)晶體管(Field-Effect Transistor,F(xiàn)ET)。

PET 與 FET 的核心區(qū)別在于溝道調(diào)制方式:PET 采用直接電接觸(電子注入)方式調(diào)控溝道,使溝道在調(diào)制過程中獲得額外電流。典型的 PET 器件如雙極結(jié)型晶體管(Bipolar Junction Transistor,BJT),其結(jié)構(gòu)包含一個(gè)基極(Base,B)—— 基極直接作用于溝道,可調(diào)控從發(fā)射極(Emitter,E)到集電極(Collector,C)的電流(見圖 1 (a))。而 FET 采用間接調(diào)控方式(通過橫向電場(chǎng))作用于溝道,使溝道在調(diào)制過程中補(bǔ)充額外電子或空穴。典型的 FET 器件如金屬 - 氧化物 - 半導(dǎo)體場(chǎng)效應(yīng)晶體管(MOSFET),其柵極(Gate,G)通過電容效應(yīng)影響溝道,進(jìn)而改變從源極(Source,S)到漏極(Drain,D)的電流(見圖 1 (b))。

BJT 俗稱 “三極管”,是最早實(shí)現(xiàn)實(shí)用化的現(xiàn)代晶體管。早在 1947 年點(diǎn)接觸晶體管問世一個(gè)月后,肖克利便提出了 “三明治” 結(jié)構(gòu)的 BJT 設(shè)計(jì)構(gòu)想;1950 年,蒂爾(G.Teal)與斯帕克斯(M.Sparks)成功制造并測(cè)試了鍺基 NPN 型 BJT。從實(shí)用角度看,點(diǎn)接觸式晶體管制造工藝繁瑣、穩(wěn)定性欠佳且產(chǎn)量極低;而結(jié)型晶體管(以 BJT 為代表)更適配現(xiàn)代集成電路制造工藝,能大幅降低生產(chǎn)成本,逐漸獲得市場(chǎng)認(rèn)可,為眾多半導(dǎo)體公司的崛起奠定了基礎(chǔ)。不過,以 BJT 為代表的 PET 需通過基極控制電流,由此帶來(lái)較高能耗與較大芯片占用面積,制造及設(shè)計(jì)成本偏高,目前主要應(yīng)用于模擬集成電路領(lǐng)域。

相比之下,以 MOSFET 為代表的 FET 具有柵極漏電流更小、單元能耗更低的優(yōu)勢(shì),更適用于超大規(guī)模集成電路(VLSI),現(xiàn)已成為集成電路中最核心的器件之一。

場(chǎng)效應(yīng)晶體管的發(fā)展歷程

晶體管誕生后發(fā)展勢(shì)頭迅猛,科研人員持續(xù)研發(fā)出各類新型晶體管:1950 年,日本學(xué)者西澤潤(rùn)一(J.Nishizawa)與渡邊寧(Y.Watanabe)共同發(fā)明了結(jié)型場(chǎng)效應(yīng)晶體管(Junction Field-Effect Transistor,JFET);1952 年,基于晶體管技術(shù)的助聽器與收音機(jī)正式投入市場(chǎng) —— 這標(biāo)志著晶體管開始從實(shí)驗(yàn)室走向?qū)嶋H應(yīng)用,推動(dòng)電子設(shè)備向小型化、低功耗方向發(fā)展。1954 年,貝爾實(shí)驗(yàn)室的坦恩鮑姆(M.Tanenbaum)制備出首個(gè)硅晶體管;同年,德州儀器的戈登?蒂爾(Gordon Teal)實(shí)現(xiàn)了硅晶體管的商業(yè)化生產(chǎn),推動(dòng)晶體管從實(shí)驗(yàn)室成果向產(chǎn)業(yè)應(yīng)用邁出關(guān)鍵一步。1956 年,通用電氣的工程師發(fā)明了晶閘管(Thyristor),為電力電子領(lǐng)域提供了新型核心器件。1959 年,貝爾實(shí)驗(yàn)室的卡恩(D.Kahng)與艾塔拉(M.Atalla)成功發(fā)明金屬 - 氧化物 - 半導(dǎo)體場(chǎng)效應(yīng)晶體管(MOSFET),這一成果將 1925 年李林菲爾德(J.Lilienfeld)提出的場(chǎng)效應(yīng)晶體管概念首次轉(zhuǎn)化為實(shí)際器件,為后續(xù)集成電路的規(guī)模化發(fā)展奠定了重要基礎(chǔ)。

盡管晶體管從 20 世紀(jì) 50 年代起逐步取代真空電子管,但當(dāng)時(shí)其高昂的制造成本,導(dǎo)致晶體管器件及基于晶體管的電子系統(tǒng)并未廣泛普及。不過,晶體管的便攜性、高可靠性與耐用性,恰好契合軍用裝備的特殊需求;同時(shí),受美國(guó)當(dāng)時(shí)太空戰(zhàn)略的推動(dòng),晶體管器件(尤其是集成電路)被大量應(yīng)用于軍工與航天領(lǐng)域。美國(guó)軍方對(duì)新興晶體管產(chǎn)業(yè)的支持,直接加速了以晶體管為核心的半導(dǎo)體產(chǎn)業(yè)發(fā)展,催生了一批知名半導(dǎo)體技術(shù)企業(yè)。

1965 年,仙童半導(dǎo)體的戈登?摩爾(Gordon Moore)提出著名的 “摩爾定律”,明確了集成電路產(chǎn)業(yè) “集成度每 18-24 個(gè)月翻倍” 的發(fā)展方向,為行業(yè)提供了清晰的技術(shù)演進(jìn)指引。1967 年,卡恩(D.Kahng)與施敏(S.M.Sze)共同研制出浮柵金屬 - 氧化物 - 半導(dǎo)體場(chǎng)效應(yīng)晶體管(FGMOSFET),攻克了非易失性存儲(chǔ)的核心技術(shù)難題,奠定了現(xiàn)代存儲(chǔ)器件的發(fā)展基礎(chǔ)。1969 年,英特爾采用二氧化硅柵介質(zhì)與多晶硅柵電極,成功開發(fā)出首個(gè) P 型 MOSFET,進(jìn)一步完善了 MOSFET 的技術(shù)體系。1971 年,英特爾發(fā)布全球首款微處理器 4004,該芯片集成了 2000 多個(gè)晶體管,標(biāo)志著集成電路從 “邏輯器件” 向 “計(jì)算核心” 的跨越。

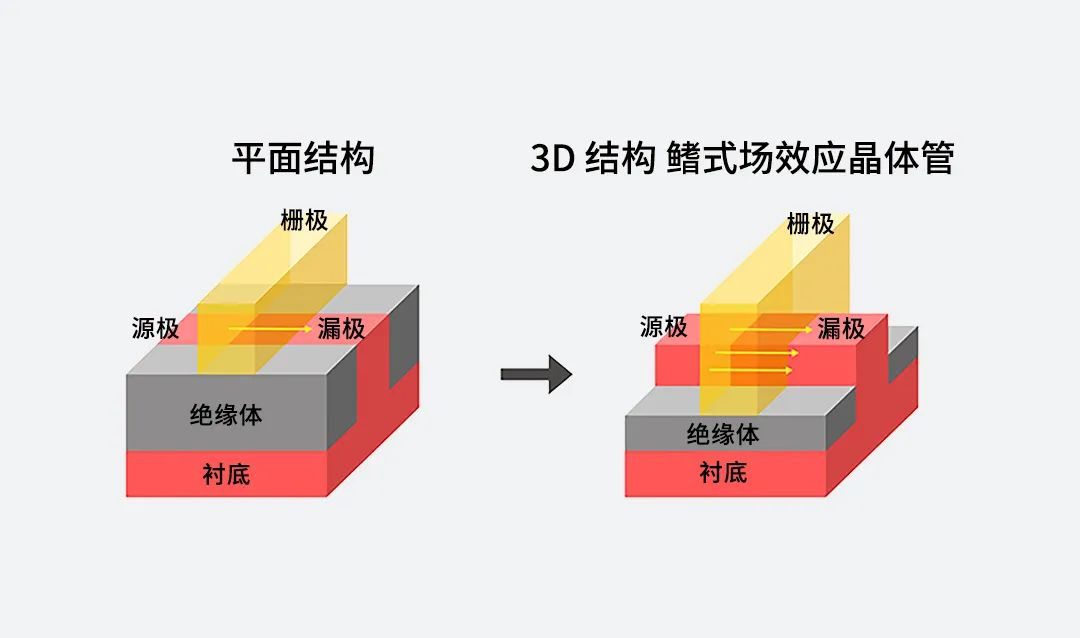

1998 年起,《半導(dǎo)體技術(shù)國(guó)際路線圖》(International Technology Roadmap for Semiconductors,ITRS)每?jī)赡臧l(fā)布一次,為全球半導(dǎo)體產(chǎn)業(yè)的技術(shù)研發(fā)與產(chǎn)能規(guī)劃提供權(quán)威指導(dǎo)。在此推動(dòng)下,半導(dǎo)體科技與產(chǎn)業(yè)發(fā)展日新月異,集成電路逐漸成為信息時(shí)代的核心支撐技術(shù)。隨著半導(dǎo)體技術(shù)的持續(xù)迭代,MOSFET 不僅在特征尺寸上不斷縮小、集成度持續(xù)提升,在器件結(jié)構(gòu)(如從平面結(jié)構(gòu)向鰭式場(chǎng)效應(yīng)晶體管 FinFET 演進(jìn))與材料體系(如高 k 柵介質(zhì)替代傳統(tǒng)二氧化硅)上也經(jīng)歷了多次重大革新,始終保持著對(duì)超大規(guī)模集成電路發(fā)展的核心驅(qū)動(dòng)作用

-

集成電路

+關(guān)注

關(guān)注

5452文章

12571瀏覽量

374517 -

二極管

+關(guān)注

關(guān)注

149文章

10406瀏覽量

178400 -

晶體管

+關(guān)注

關(guān)注

78文章

10395瀏覽量

147723

原文標(biāo)題:晶體管簡(jiǎn)述

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

晶體管的結(jié)構(gòu)特性

電子管與晶體管在結(jié)構(gòu)和應(yīng)用上的區(qū)別

SiC-MOSFET功率晶體管的結(jié)構(gòu)與特征比較

IGBT絕緣柵雙極晶體管的基本結(jié)構(gòu)與特點(diǎn)

晶體管的發(fā)展歷程概述

什么是晶體管 晶體管的分類及主要參數(shù)

晶體管的結(jié)構(gòu)及性能特點(diǎn)有哪些?

CMOS晶體管,CMOS晶體管是什么意思

晶體管是誰(shuí)發(fā)明的_晶體管發(fā)明時(shí)間

雙極晶體管的基本結(jié)構(gòu)

詳解晶體管的發(fā)展歷程與作用和分類及其結(jié)構(gòu)

探究晶體管發(fā)展歷程

天線與晶體管發(fā)展歷程

PNP晶體管符號(hào)和結(jié)構(gòu) 晶體管測(cè)試儀電路圖

晶體管的基本結(jié)構(gòu)和發(fā)展歷程

晶體管的基本結(jié)構(gòu)和發(fā)展歷程

評(píng)論