SPI是單片機外設電路中常用的一種通訊方式,適用于近距離通信,通常用于芯片間的通訊,有四根線。在SPI通訊中總線時鐘和總線相位也兩個比較重要的概念,一般在使用SPI通信時都使用默認設置,所以容易把這兩個參數忽略。和大家分享一下SPI通訊、時鐘極性以及時鐘相位的基礎知識。 什么是SPI通訊總線 SPI總線的英文全稱為S“Serial Periphral Interface”,意思是串行外設接口,由于通訊距離比較短,適用于芯片級別的短距離通訊。SPI的通訊分為主機和從機,屬于高速全雙工的總線通訊方式,SPI有四根線,分別為:

MISO:主設備輸入與從設備輸出線;

MOSI:主設備輸出與從設備輸入線;

SCK:串行同步時鐘信號線;

SS:從機片選信號線,也用CS來表示。

SPI總線的主機和從機的系統連接圖如下圖所示。

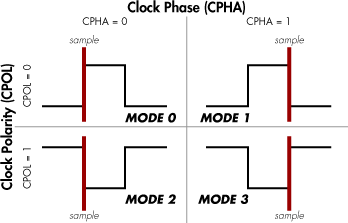

SPI總線時鐘的極性含義解釋 SPI的時鐘極性用CPOL來表示。SPI總線通訊的時基基準是時鐘信號線SCK,SCK既有高電平,又有低電平,SPI的時鐘極性用來表示時鐘信號在空閑時是高電平還是低電平。情況說明如下:

當CPOL=0:SCK信號線在空閑時為低電平;

當CPOL=1:SCK信號線在空閑時為高電平;

SPI總線時鐘的相位含義解釋

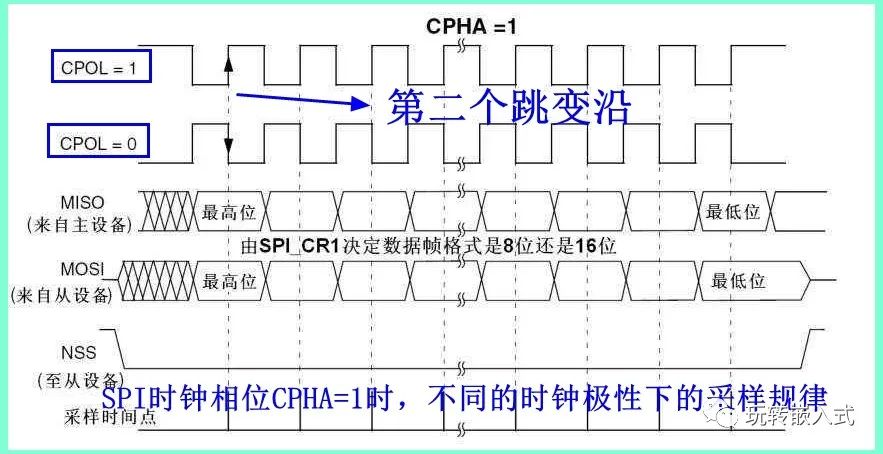

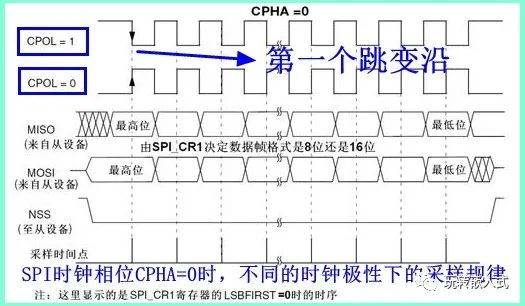

時鐘的相位用CPHA來表示,用來決定何時進行信號采樣,在第一個跳變沿還是第二個跳變沿,至于是上升沿還是下降沿則由CPOL相位極性來表示。下面分兩種情況來介紹。如下圖所示。

上圖表示CPHA=1時的情形,即在SCK時鐘的第二個邊沿進行數據的采樣,至于是上升沿采樣還是下降沿采樣取決于時鐘極性CPOL的值。如果CPHA=1,CPOL=1,則在SCK時鐘的第二個邊沿為上升沿時進行數據采樣。如果CPHA=1,CPOL=0,則在SCK時鐘的第二個邊沿為下降沿時進行數據采樣。 CPHA=0時的情形如下圖所示。

上圖表示CPHA=0時的情形,即在SCK時鐘的第一個邊沿進行數據的采樣,至于是上升沿采樣還是下降沿采樣取決于時鐘極性CPOL的值。如果CPHA=0,CPOL=1,則在SCK時鐘的第一個邊沿為下降沿時進行數據采樣。如果CPHA=0,CPOL=0,則在SCK時鐘的第一個邊沿為上升沿時進行數據采樣。 總結一下,SPI的時鐘極性決定了SCK在空閑時是低電平還是高電平;而相位極性則決定了在第一個邊沿還是第二個邊沿進行數據采樣。SPI的時鐘極性CPOL和相位極性CPHA是相互影響相互決定的,以上概念可能很繞口難以理解,但是對SPI進行一次編程之后,所有的內容都好理解了。

責任編輯:xj

原文標題:SPI編程時,時鐘相位(CPHA)和時鐘極性(CPOL)怎么理解?

-

時鐘

+關注

關注

11文章

1971瀏覽量

134987 -

SPI

+關注

關注

17文章

1885瀏覽量

101227 -

編程

+關注

關注

90文章

3716瀏覽量

97182

原文標題:SPI編程時,時鐘相位(CPHA)和時鐘極性(CPOL)怎么理解?

文章出處:【微信號:gh_c472c2199c88,微信公眾號:嵌入式微處理器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

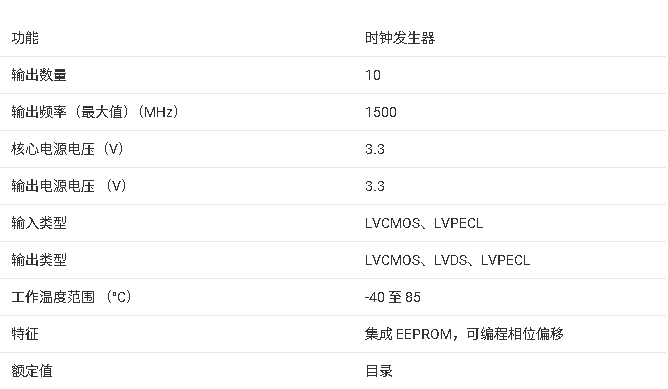

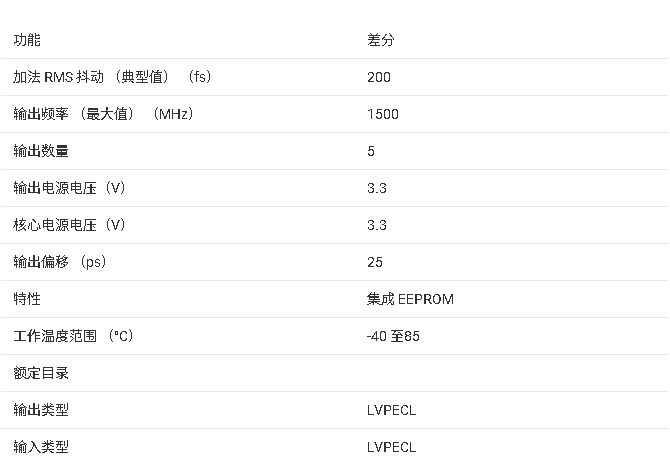

核芯互聯正式推出新一代高性能低相位噪聲可編程任意時鐘發生器CLG6965

CDCE18005:高性能可編程時鐘緩沖器的深度剖析

?CDCE72010 高性能時鐘同步器、抖動清除器和時鐘分配器總結

?CDCE18005可編程時鐘緩沖器技術文檔摘要

?CDC3RL02 低相位噪聲雙通道時鐘扇出緩沖器總結

嵌入式接口通識知識之SPI接口

當波特率設置為高時,SPI 時鐘延長,數據丟失問題怎么解決?

FPGA時序約束之設置時鐘組

AD9547雙路/四路輸入網絡時鐘發生器/同步器技術手冊

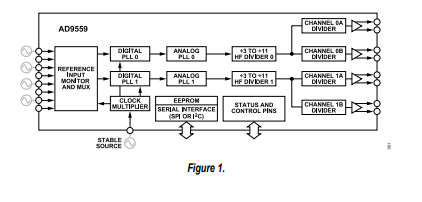

AD9559雙路PLL四通道輸入多服務線路卡自適應時鐘轉換器技術手冊

AD9554四路PLL、四通道輸入、八通道輸出多服務線路卡自適應時鐘轉換器技術手冊

SPI編程時,如何理解時鐘相位和時鐘極性

SPI編程時,如何理解時鐘相位和時鐘極性

評論