一顆芯片從無到有,從有需求到最終應(yīng)用,經(jīng)歷的是一個漫長的過程,作為人類科技巔峰之一的芯片,凝聚了人們的智慧,而芯片產(chǎn)業(yè)鏈也是極其復(fù)雜的,在此,我大致把它歸為四個部分(市場需求--芯片設(shè)計--芯片制造--測試封裝),然后再一一的做詳細介紹。

市場需求

這個無需多講,目前芯片應(yīng)用已經(jīng)滲透到我們生活的方方面面,早晨上班騎的共享單車,到公司刷的IC卡,工作時偷偷地打游戲,手機卡了還要換更快的手機,可以說IC的市場需求一直都在。

芯片設(shè)計

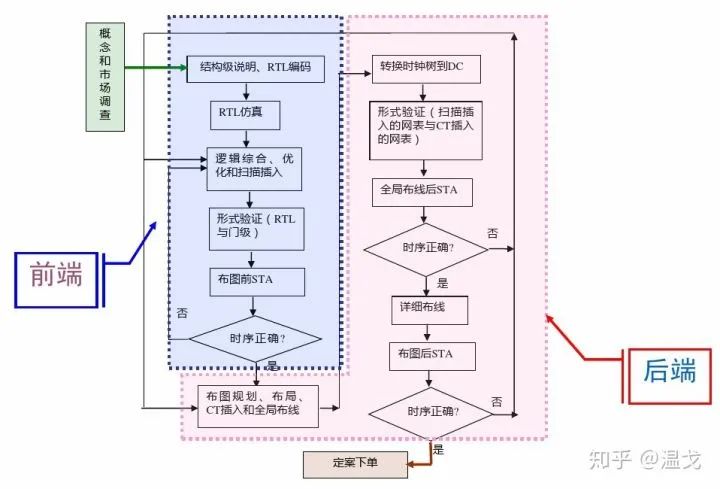

芯片設(shè)計又可以分為兩部分,芯片前端設(shè)計和芯片后端設(shè)計,整體流程如下圖:

芯片前端設(shè)計前端設(shè)計也就是從輸入需求到輸出網(wǎng)表的過程:主要分為以下六個步驟:

RTL設(shè)計

驗證

靜態(tài)時序分析

覆蓋率

ASIC邏輯綜合

時序分析和驗證時出現(xiàn)的錯誤可能需要反復(fù)重做前面幾步才能解決,是一個多次迭代優(yōu)化的過程。 下面我來仔細介紹一下這六個步驟。1、RTL設(shè)計在設(shè)計之前我們先要確定芯片的工藝,比如是選擇TSMC還是SMIC,是7nm,還是5nm,而工藝的選擇也是受很多因素的制約(如下圖),而芯片工藝的選擇,就是對這些因素的權(quán)衡。

IC設(shè)計的第一步就是制定Spec,這個步驟就像是在設(shè)計建筑前,要先畫好圖紙一樣,在確定好所有的功能之后在進行設(shè)計,這樣才不用再花額外的時間進行后續(xù)修改。IC 設(shè)計也需要經(jīng)過類似的步驟,才能確保設(shè)計出來的芯片不會有任何差錯。

由文檔來寫RTL 而用RTL實現(xiàn)的各種功能模塊,來組成一個實現(xiàn)具體功能的IP,SOC芯片最終由SOC integration工程師把各個IP集成到一起。 IP又分為模擬IP和數(shù)字IP,大概可以做如下的分類:

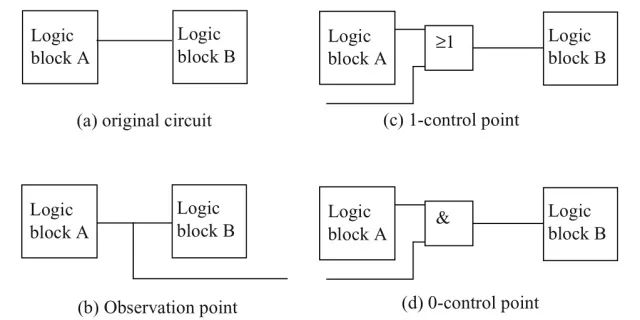

在芯片功能設(shè)計完備后,我們還要做可測性設(shè)計DFT(Design For Test)。 關(guān)于DFT的具體介紹,請直達以下兩個傳送門: 芯片設(shè)計中,DFT崗位是什么體驗? https://www.zhihu.com/question/401109345/answer/1387028607 https://zhuanlan.zhihu.com/p/159273941

RTL設(shè)計最后要做的就是代碼的設(shè)計規(guī)則檢查。 通過lint, Spyglass等工具,針對電路進行設(shè)計規(guī)則檢查,包括代碼編寫風格,DFT,命名規(guī)則和電路綜合相關(guān)規(guī)則等。2、驗證驗證是保證芯片功能正確性和完整性最重要的一環(huán)。驗證的工作量也是占整個芯片開發(fā)周期的50%-70%,相應(yīng)的,驗證工程師與設(shè)計工程師的數(shù)量大概在2-3:1。 從驗證的層次可以分位:模塊級驗證,子系統(tǒng)級驗證和系統(tǒng)級驗證。 從驗證的途徑可以分為:模擬(simulation),仿真和形式驗證(formality check)。

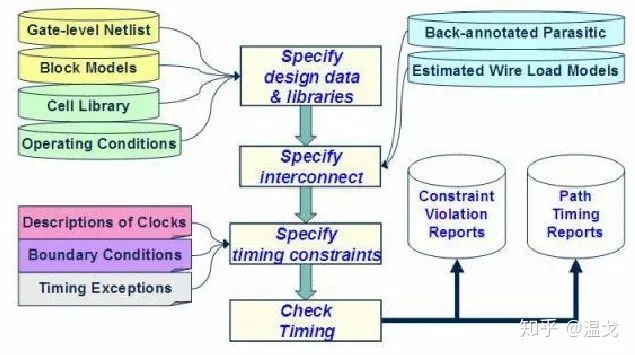

3、靜態(tài)時序分析(STA)靜態(tài)時序分析是套用特定的時序模型(timing model),針對特定電路,分析其是否違反designer給定的時序限制(timing constraint)。 目前主流的STA工具是synopsys的Prime Time。

時序分析流程圖 靜態(tài)時序分析的作用:

確定芯片最高工作頻率

通過時序分析可以控制工程的綜合、映射、布局布線等環(huán)節(jié),減少延遲,從而盡可能提高工作頻率。2. 檢查時序約束是否滿足可以通過時序分析來查看目標模塊是否滿足約束,如不滿足,可以定位到不滿足約束的部分,并給出具體原因,進一步修改程序直至滿足要求。3. 分析時鐘質(zhì)量時鐘存在抖動、偏移、占空比失真等不可避免的缺陷。通過時序分析可以驗證其對目標模塊的影響。4、覆蓋率覆蓋率作為一種判斷驗證充分性的手段,已成為驗證工作的主導(dǎo)。 從目標上,可以把覆蓋率分為兩類:

代碼覆蓋率

作用:檢查代碼是否冗余,設(shè)計要點是否遍歷完全。 檢查對象:RTL代碼

功能覆蓋率

作用:檢查功能是否遍歷 檢查對象:自定義的container 在設(shè)計完成時,要進行代碼覆蓋率充分性的sign-off, 對于覆蓋率未達到100%的情況,要給出合理的解釋,保證不影響芯片的工能。5、ASIC綜合邏輯綜合的結(jié)果就是把設(shè)計實現(xiàn)的RTL代碼翻譯成門級網(wǎng)表(netlist)的過程。 在做綜合時要設(shè)定約束條件,如電路面積、時序要求等目標參數(shù)。 工具:synopsys的Design compiler, 綜合后把網(wǎng)表交給后端。 至此我們前端的工作就結(jié)束啦,看到這里我先給各位看官個贊!

芯片后端設(shè)計后端設(shè)計也就是從輸入網(wǎng)表到輸出GDSII文件的過程:主要分為以下六個步驟:

邏輯綜合

形式驗證

時鐘數(shù)綜合

物理實現(xiàn)

時鐘樹綜合-CTS

寄生參數(shù)提取

版圖物理驗證

1.邏輯綜合在前端最后一步已經(jīng)講過了,在此不做贅述。2. 形式驗證

驗證芯片功能的一致性

不驗證電路本身的正確性

每次電路改變后都需驗證

形式驗證的意義在于保障芯片設(shè)計的一致性,一般在邏輯綜合,布局布線完成后必須做。 工具:synopsys Formality4. 物理實現(xiàn)物理實現(xiàn)可以分為三個部分:布局規(guī)劃 floor plan布局 place布線 route1、布圖規(guī)劃floor plan布圖規(guī)劃是整個后端流程中作重要的一步,但也是彈性最大的一步。因為沒有標準的最佳方案,但又有很多細節(jié)需要考量。 布局布線的目標:優(yōu)化芯片的面積,時序收斂,穩(wěn)定,方便走線。 工具:IC compiler,Encounter 布圖規(guī)劃完成效果圖:

2、布局布局即擺放標準單元,I/O pad,宏單元來實現(xiàn)個電路邏輯。 布局目標:利用率越高越好,總線長越短越好,時序越快越好。 但利用率越高,布線就越困難;總線長越長,時序就越慢。因此要做到以上三個參數(shù)的最佳平衡。 布局完成效果圖:

3、布線布線是指在滿足工藝規(guī)則和布線層數(shù)限制、線寬、線間距限制和各線網(wǎng)可靠絕緣的電性能約束條件下,根據(jù)電路的連接關(guān)系,將各單元和I/O pad用互連線連接起來。

5.時鐘樹綜合——CTS

Clock Tree Synthesis,時鐘樹綜合,簡單點說就是時鐘的布線。 由于時鐘信號在數(shù)字芯片的全局指揮作用,它的分布應(yīng)該是對稱式的連到各個寄存器單元,從而使時鐘從同一個時鐘源到達各個寄存器時,時鐘延遲差異最小。這也是為什么時鐘信號需要單獨布線的原因。

6. 寄生參數(shù)提取

由于導(dǎo)線本身存在的電阻,相鄰導(dǎo)線之間的互感,耦合電容在芯片內(nèi)部會產(chǎn)生信號噪聲,串擾和反射。這些效應(yīng)會產(chǎn)生信號完整性問題,導(dǎo)致信號電壓波動和變化,如果嚴重就會導(dǎo)致信號失真錯誤。提取寄生參數(shù)進行再次的分析驗證,分析信號完整性問題是非常重要的。 工具Synopsys的Star-RCXT7.版圖物理驗證這一環(huán)節(jié)是對完成布線的物理版圖進行功能和時序上的驗證,大概包含以下方面: LVS(Layout Vs Schematic)驗證:簡單說,就是版圖與邏輯綜合后的門級電路圖的對比驗證; DRC(Design Rule Checking):設(shè)計規(guī)則檢查,檢查連線間距,連線寬度等是否滿足工藝要求; ERC(Electrical Rule Checking):電氣規(guī)則檢查,檢查短路和開路等電氣規(guī)則違例; 實際的后端流程還包括電路功耗分析,以及隨著制造工藝不斷進步產(chǎn)生的DFM(可制造性設(shè)計)問題等。物理版圖以GDSII的文件格式交給芯片代工廠(稱為Foundry)在晶圓硅片上做出實際的電路。

GDSII效果版圖 最后進行封裝和測試,就得到了我們實際看見的芯片。

芯片設(shè)計的流程是紛繁復(fù)雜的,從設(shè)計到流片耗時長(一年甚至更久),流片成本高,一旦發(fā)現(xiàn)問題還要迭代之前的某些過程。

責任編輯:xj

原文標題:一款芯片產(chǎn)品從構(gòu)想到完成是怎樣的過程?

文章出處:【微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

芯片

+關(guān)注

關(guān)注

463文章

54010瀏覽量

466058 -

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

30737瀏覽量

264122 -

IC

+關(guān)注

關(guān)注

36文章

6411瀏覽量

185631 -

硅片

+關(guān)注

關(guān)注

13文章

410瀏覽量

35730

原文標題:一款芯片產(chǎn)品從構(gòu)想到完成是怎樣的過程?

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

燃氣表需要一顆溫濕度傳感器推薦啥?

從芯片到方案,靈活因應(yīng)多元 BLDC 驅(qū)動應(yīng)用需求

電動汽車無線充電系統(tǒng)標準

如何設(shè)計一顆車規(guī)級MCU芯片?從架構(gòu)到認證的全流程實戰(zhàn)指南

一顆芯片賣爆了是什么感覺

為什么有些電子產(chǎn)品主板上會有一顆CR2032紐扣電池?

存儲芯片從無到有的全過程,這些技術(shù)細節(jié)你肯定沒聽說過

絲桿模組從結(jié)構(gòu)到應(yīng)用,有哪些核心類型?

一顆優(yōu)質(zhì)的音頻功放芯片硬核素質(zhì)有哪些?優(yōu)質(zhì)音頻功放芯片的全維度評估框架

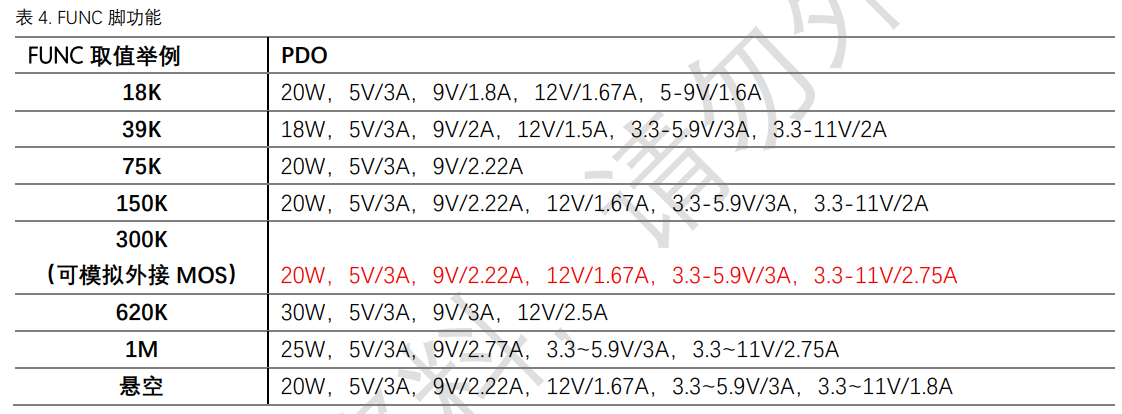

一顆快充芯片給我的6個啟發(fā):從規(guī)格書里讀懂精妙設(shè)計

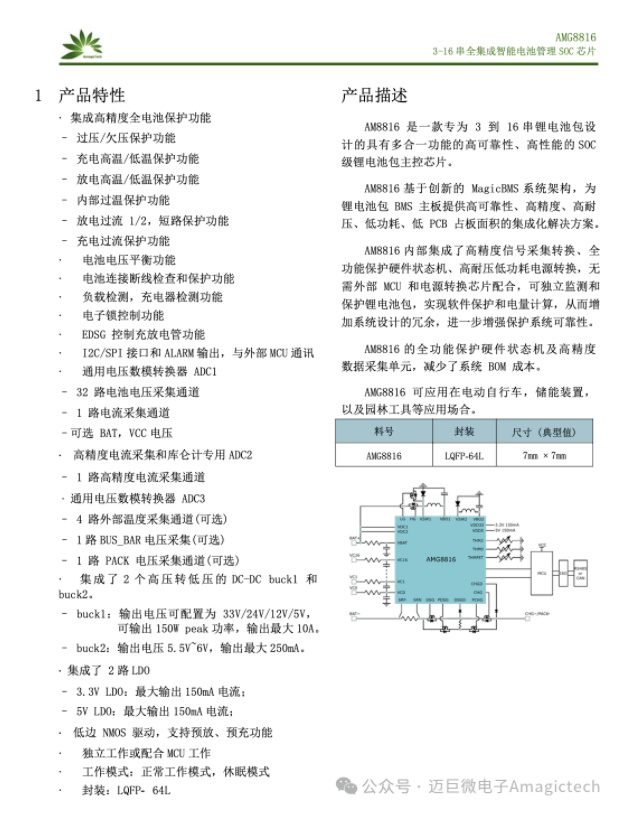

3-16串一顆芯片搞定 全解AMG8816全集成BMS主控的參數(shù)真相

DSP從入門到精通全集

從同步軌道到星鏈組網(wǎng)(上):衛(wèi)星通信的世紀跨越

汽車電子芯片數(shù)量大增:從 500 顆到 3000 顆,錫膏如何撐起可靠性大旗?

一顆芯片的從無到有,從有需求到最終應(yīng)用

一顆芯片的從無到有,從有需求到最終應(yīng)用

評論