在汽車電子的 “神經中樞” 里,車規級 MCU 芯片是無可替代的核心 —— 它主導著車身控制、電動助力轉向(EPS)、電子穩定程序(ESP)、電池管理系統(BMS)等關鍵場景的實時控制,直接關系到駕駛安全與車輛可靠性。與消費級 MCU 不同,車規級 MCU 需在 - 40℃~150℃的寬溫環境、10g 振動的機械應力、200V/m 的電磁干擾下穩定運行,同時滿足 ISO 26262 功能安全與 ISO/SAE 21434 信息安全的嚴苛要求。

本文結合頭部廠商的實踐經驗,從需求定義、架構設計、核心模塊開發到認證落地,拆解車規級 MCU 芯片的完整設計流程,為硬件工程師、嵌入式開發者提供可落地的技術指南。

一、設計前置:明確車規級 MCU 的核心需求與指標

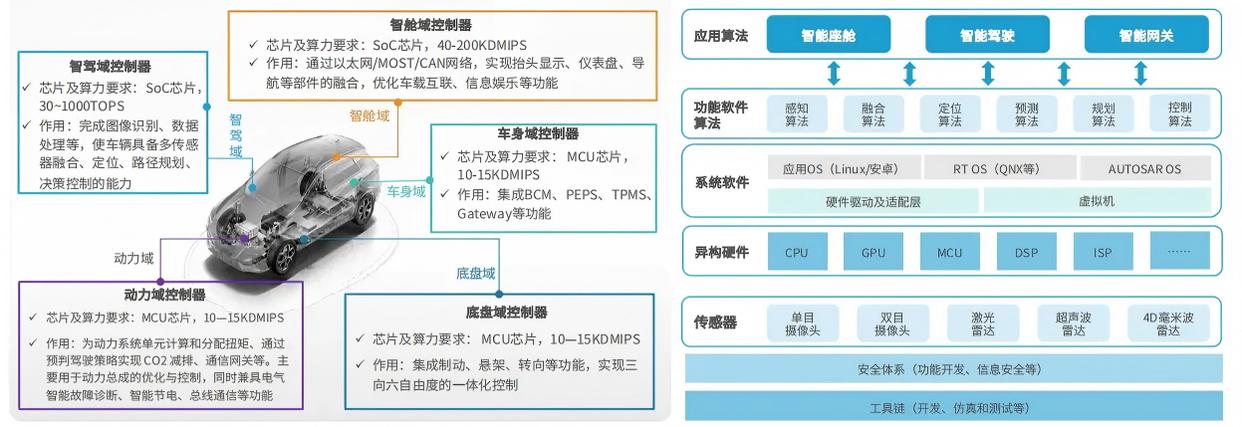

車規級 MCU 的設計始于 “需求錨定”—— 需結合應用場景(如動力域、車身域)、安全等級(ASIL-A 至 ASIL-D)、性能要求(算力、接口)等維度,定義不可妥協的核心指標。這一步是后續架構設計與模塊開發的 “總綱”,直接決定芯片的成敗。

1. 場景驅動的需求拆解

| 應用場景 | 核心功能需求 | 性能指標參考 | 安全等級要求 |

|---|---|---|---|

| 動力域(BMS) | 電芯電壓采集、均衡控制、充放電管理 | 12bit以上 ADC、支持 CAN FD | ASIL-B/D |

| 車身域(BCM) | 燈光控制、門窗驅動、傳感器信號處理 | 多IO口(≥100 個)、低功耗 | ASIL-A/B |

| 底盤域(ESP) | 輪速計算、剎車壓力控制、姿態穩定 | 鎖步核、1ms控制周期 | ASIL-D |

| 區域控制器 | 多協議轉換、負載管理、OTA本地執行 | 集成以太網PHY、支持虛擬化 | ASIL-B/C |

不同車載場景對 MCU 的需求差異顯著,需先明確芯片的定位與應用邊界:

以底盤域 ESP 控制為例,其核心需求可進一步拆解為:運算單元需支持 1ms 內完成輪速融合與壓力計算;通信接口需兼容 CAN FD(8Mbps 速率);安全層面需實現故障檢測率≥99.9%、響應時間≤100μs。

2. 不可妥協的車規核心指標

基于場景需求,需明確以下四類硬性指標,這些指標是后續測試與認證的核心依據:

環境適應性:寬溫(Grade 0 級為 - 40℃150℃)、抗振動(10g,5Hz2000Hz)、抗電磁干擾(CISPR 25 Class 3);

功能安全:ASIL 等級(如 ESP 需 ASIL-D)、故障診斷覆蓋率(硬件≥90%,軟件≥95%)、單點故障 metric(SPFM)≥90%(ASIL-D 級);

性能與接口:CPU 主頻(Cortex-R52 核可達 600MHz)、嵌入式存儲(NVM≥16MB,支持 ECC)、通信接口(CAN FD/CAN SIC、以太網 100BASE-T1/10BASE-T1S);

信息安全:支持 AES-256 加密、安全啟動、硬件防篡改,滿足 ISO/SAE 21434 威脅防護要求。

二、架構設計:車規級 MCU 的 “安全骨架” 搭建

架構設計是車規級 MCU 的 “靈魂”,需平衡安全性、實時性與成本,核心圍繞 “計算核心冗余化、功能模塊集成化、安全邊界清晰化” 三大原則展開,目前主流架構采用 “鎖步多核集群 + 安全島 + 專用外設” 的組合方案。

1. 計算核心:鎖步架構保障運算可靠性

車規級 MCU 的計算核心必須解決 “運算錯誤” 風險,Lockstep(鎖步)架構是 ASIL-B 及以上等級的標配 —— 將兩顆完全相同的 CPU 核心(如 Cortex-R52)并行運行,實時對比指令執行結果與輸出數據,一旦出現偏差立即觸發故障響應。

架構細節與工程實踐:

核間同步:通過硬件同步信號(如時鐘同源、復位同步)確保兩顆核心的執行時序偏差≤1ns;

結果校驗:在指令流水線末端設置 “比較器”,對運算結果、狀態寄存器值進行逐周期比對;

故障響應:偏差發生時,立即觸發本地復位(核心級)或通知安全管理單元(系統級),確保錯誤不擴散。

如可以采用 “Cortex-M7 + Cortex-M4” 異構鎖步設計,M7 核(1GHz)負責高性能計算,M4 核(400MHz)負責實時控制與結果校驗,兼顧算力與安全性。

2. 安全島:隔離式安全管理中樞

為避免安全功能與非安全功能的相互干擾,需在架構中劃分獨立的 “安全島”(Safety Island),作為全芯片的安全管控核心。安全島需具備 “硬件隔離、權限獨立、自主運行” 的特性,不受主核故障影響。

安全島核心模塊組成:

安全管理單元(SMU):統籌故障檢測與響應,接收來自鎖步核、外設、診斷模塊的故障信號,執行分級處理(如報警、降級、關斷);

加密引擎:集成 AES、RSA/ECC、SHA-2 等算法硬件加速器,支持國密算法(SM2/SM4),負責密鑰存儲與數據加密;

防篡改控制器:連接溫度、電壓、光強傳感器陣列,檢測物理拆解或異常訪問,觸發敏感數據銷毀;

獨立時鐘與電源:采用專用 RC 振蕩器與 LDO 供電,避免主系統電源 / 時鐘故障導致安全島失效。

安全島通常采用 “硬件熔斷(Fuse)+ 獨立總線” 設計,安全配置參數寫入 Fuse 后不可篡改,安全島與主核間通過單向總線通信,防止主核越權訪問。

3. 外設集成:滿足車載場景的連接與控制需求

車規級 MCU 的外設模塊需 “按需集成、冗余設計”,重點覆蓋通信接口、模擬前端、控制輸出三類核心外設,同時支持功能安全機制。

關鍵外設設計要點:

通信接口:

集成多通道 CAN FD 控制器,支持 CAN SIC 技術(降低信號反射,8Mbps 長線傳輸可靠);

嵌入以太網 PHY(100BASE-T1/10BASE-T1S),支持 gPTP 時間同步(微秒級對齊);

通信接口需具備 CRC 校驗、超時檢測、總線監控功能,符合 ISO 15765-4 標準。

模擬前端:

集成 12bit 以上 ADC(采樣率≥1MSPS),支持差分輸入與硬件過壓保護;

配備 PGA(可編程增益放大器)與溫度補償電路,確保寬溫下采樣精度≤±1%。

控制輸出:

提供多路 PWM 輸出(支持死區控制、故障關斷),用于電機驅動、閥門控制;

輸出通道需具備短路保護、過流檢測功能,響應時間≤10μs。

三、核心模塊開發:從硬件到軟件的安全落地

架構確定后,需進入模塊級開發階段 —— 硬件層面聚焦 “可靠性設計”,軟件層面聚焦 “安全編碼與驗證”,兩者協同實現芯片的安全目標。

1. 硬件模塊:可靠性與安全機制雙保障

硬件模塊開發需解決 “故障預防、故障檢測、容錯運行” 三大問題,重點關注電源、時鐘、存儲三類核心模塊。

(1)電源管理模塊(PMU)

電源是芯片運行的基礎,需設計多域供電與故障防護機制:

多域 LDO:核心域(VDD)、IO 域(VDDIO)、安全島域(VDD_S)分別采用獨立 LDO,輸出電壓精度 ±2%;

過壓 / 欠壓保護:每個 LDO 輸出端設置比較器,閾值通過 Fuse 鎖定,過壓時觸發鉗位電路,欠壓時觸發預警;

掉電預警:通過電容儲能檢測電壓下降速率(≥1V/ms),提前 50μs 生成預警,為安全島保存關鍵數據預留時間。

(2)時鐘管理模塊(CMU)

時鐘異常是導致芯片功能失效的主要原因之一,需實現全時鐘域的監控與校準:

多源時鐘冗余:主時鐘采用車規級晶振(±20ppm),備用時鐘采用 RC 振蕩器,支持無縫切換(切換時間≤10μs);

頻率監控:每個時鐘域配備計數器,將被監控時鐘與參考時鐘(32kHz 晶振)比對,偏差超過 ±1% 則觸發故障;

漂移校準:通過 PLL(鎖相環)的頻率控制寄存器,動態調整時鐘頻率,寬溫下偏差控制在 ±0.1% 以內。

(3)存儲模塊(NVM/RAM)

存儲模塊需保障數據的完整性與持久性,同時支持安全擦寫:

嵌入式 NVM:采用 NOR Flash,支持 ECC 校驗(糾正 1bit 錯誤,檢測 2bit 錯誤),擦寫壽命≥10 萬次,數據保存時間≥15 年;

安全 RAM:劃分獨立的安全數據區,支持奇偶校驗,空閑時自動清零,防止敏感數據殘留;

存儲保護:通過存儲保護單元(MPU)設置讀寫權限,非安全任務禁止訪問安全存儲區。

2. 軟件層面:安全編碼與全流程驗證

車規級 MCU 的軟件需 “安全優先于性能”,從編碼規范、測試驗證到運行時防護,構建全生命周期的安全體系。

(1)安全編碼與開發流程

編碼規范:嚴格遵循 MISRA C:2012 規范,禁止動態內存分配、隱式類型轉換、匯編語言,所有變量顯示初始化;

開發工具鏈:采用經 ISO 26262 認證的工具(如 S32 Design Studio、VectorCAST),確保工具鏈自身的可靠性;

版本管理:采用 Git+SVN 雙備份,每版代碼需關聯需求文檔與測試報告,支持全流程追溯。

(2)多層次測試驗證

單元測試:對每個函數 / 模塊進行測試,覆蓋正常、異常、邊界場景,ASIL-D 級要求 MC/DC 覆蓋率≥90%;

故障注入測試:模擬硬件故障(如時鐘停擺、電壓跌落)、軟件漏洞(如數組越界),驗證故障檢測率與響應時間;

系統級測試:搭建硬件在環(HIL)測試臺,模擬車載環境(溫度、電磁干擾),驗證芯片與外設的協同運行。

四、測試與認證:車規級 MCU 的 “通關憑證”

沒有通過車規認證的 MCU 無法進入車載供應鏈,測試與認證是芯片設計的 “最后一公里”,需覆蓋環境可靠性、功能安全、信息安全三大維度,核心認證包括 AEC-Q100、ISO 26262、ISO/SAE 21434。

1. 環境可靠性測試(AEC-Q100)

AEC-Q100 是車規芯片的基礎認證,需通過 7 大類測試,驗證芯片在惡劣環境下的可靠性:

| 測試項目 | 測試條件(Grade 0級) | 合格標準 |

|---|---|---|

| 高溫老化 | 150℃,1000 小時 | 無性能退化、無引腳腐蝕 |

| 溫度循環 | -40℃~150℃,1000 次循環 | 焊點無裂紋、功能正常 |

| 振動測試 | 10g,5Hz~2000Hz,3 軸各 8 小時 | 封裝無開裂、參數變化≤1% |

| 電磁兼容(EMC) | 輻射抗擾度200V/m,輻射發射≤40dBμV/m | 功能無中斷、數據無錯誤 |

測試需委托第三方實驗室(如 SGS、TüV)執行,測試數據作為認證申請的核心依據。

2. 功能安全認證(ISO 26262)

ISO 26262 認證需基于 ASIL 等級開展,核心是 “安全生命周期管理” 與 “安全驗證”,分為芯片級(SEooC)與系統級兩個層面:

認證關鍵環節:

安全分析:執行 FMEA(故障模式與影響分析)、FMEDA(故障模式影響及診斷分析),明確故障模式與檢測方法;

安全機制驗證:通過故障注入測試,驗證 Lockstep、ECC、BIST 等機制的有效性,確保故障檢測率達標;

文檔提交:提交安全計劃、設計文檔、測試報告、失效分析報告,接受認證機構(如 TüV 萊茵)的審核。

3. 信息安全認證(ISO/SAE 21434)

隨著汽車智能化升級,信息安全成為必選項,ISO/SAE 21434 認證需覆蓋 “威脅防護、漏洞管理、應急響應” 全流程:

核心認證要求:

威脅分析(TARA):識別芯片面臨的攻擊場景(如側信道攻擊、固件篡改),評估風險等級;

防護機制驗證:測試安全啟動、加密引擎、防篡改功能的有效性,如通過側信道攻擊工具驗證掩碼技術的防護效果;

漏洞管理:建立芯片全生命周期的漏洞監測與修復流程,支持 OTA 安全更新。

五、工程落地:從原型到量產的關鍵挑戰與應對

芯片設計完成后,需解決 “原型驗證、量產良率、供應鏈協同” 三大工程問題,才能真正實現商業化落地。

1. 原型驗證:硬件在環(HIL)測試臺的搭建

原型芯片需通過 HIL 測試臺模擬真實車載環境,驗證功能與安全:

環境模擬:通過溫度箱、振動臺、EMC 模擬器復現車載工況;

外設仿真:用板卡仿真傳感器(輪速、溫度)、執行器(電機、閥門)的輸入輸出信號;

自動化測試:編寫測試腳本(如 Python+CANoe),執行 10 萬次以上的循環測試,捕捉偶發故障。

2. 量產良率:車規級制造與測試保障

車規級 MCU 的量產需滿足 “高良率、高一致性”,制造環節需:

晶圓制造:采用車規級制程(如 16nm Auto),晶圓測試(CP)覆蓋電學參數、功能測試,篩選不良品;

封裝工藝:采用 QFN/LGA 封裝,添加金屬屏蔽層,封裝后測試(FT)包含環境應力測試;

質量管控:執行 AEC-Q001(分立器件)、AEC-Q002(電源)等標準,確保器件一致性。

3. 供應鏈協同:與車企、Tier1 的聯動

芯片廠商需與下游伙伴深度協同,確保芯片適配系統需求:

早期介入:在車企車型定義階段參與需求討論,明確芯片接口與安全需求;

提供參考設計:提供硬件開發板(如恩智浦 MR-VMU-RT1176)、軟件棧(Zephyr、ROS2),降低 Tier1 的開發難度;

支持認證:協助車企完成系統級 ISO 26262/21434 認證,提供芯片級安全證據。

六、總結:車規級 MCU 設計的核心原則與趨勢

車規級 MCU 的設計是 “安全、可靠、成本” 的平衡藝術,核心遵循三大原則:安全優先(鎖步、安全島等機制不可妥協)、場景驅動(外設與性能按需設計)、全周期管控(從需求到量產的安全驗證)。

未來,隨著汽車區域控制、智能駕駛的發展,車規級 MCU 將呈現三大趨勢:算力升級(多核異構、NPU 集成)、安全融合(功能安全與信息安全深度協同)、接口高速化(支持 CAN-XL、5G 以太網)。掌握這些趨勢與設計方法,才能在車規芯片賽道中打造出滿足市場需求的產品。

-

mcu

+關注

關注

147文章

19037瀏覽量

401498 -

汽車電子

+關注

關注

3045文章

9048瀏覽量

173032 -

電池管理系統

+關注

關注

43文章

611瀏覽量

35012

發布評論請先 登錄

CW32A系列(車規級 MCU)介紹

曦華科技車規級MCU CVM011x系列榮獲ISO 26262 ASIL-B認證

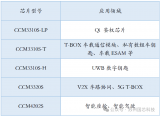

杰發科技車規級MCU在數字鑰匙領域的應用

國芯科技車規級MCU芯片CCFC2012BC出貨量突破千萬顆

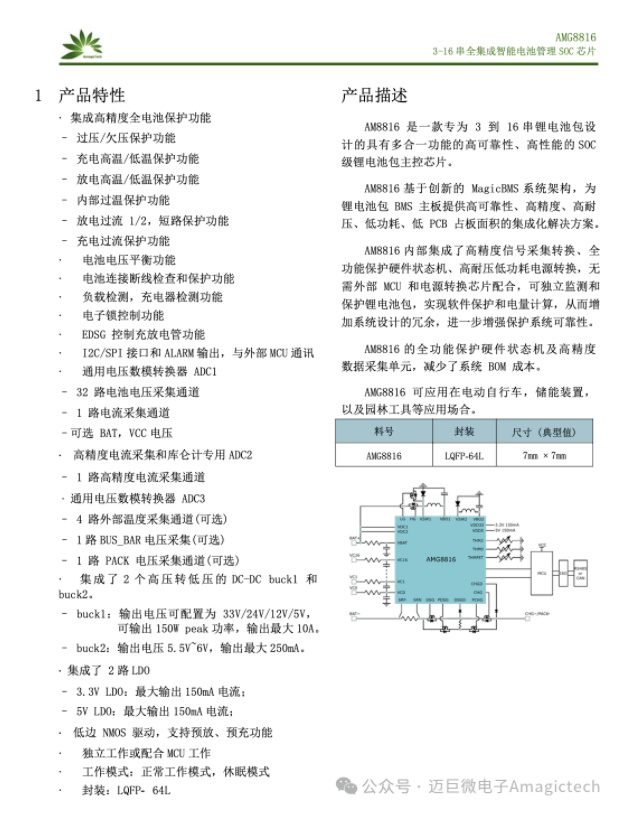

3-16串一顆芯片搞定 全解AMG8816全集成BMS主控的參數真相

如何設計一顆車規級MCU芯片?從架構到認證的全流程實戰指南

如何設計一顆車規級MCU芯片?從架構到認證的全流程實戰指南

評論