責任編輯:xj

原文標題:芯片解剖,逐層剝離

文章出處:【微信公眾號:上海季豐電子】歡迎添加關注!文章轉載請注明出處。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

芯片

+關注

關注

463文章

54010瀏覽量

466107 -

反應離子刻蝕

+關注

關注

0文章

6瀏覽量

1930

原文標題:芯片解剖,逐層剝離

文章出處:【微信號:zzz9970814,微信公眾號:上海季豐電子】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

熱點推薦

集成電路制造工藝中的刻蝕技術介紹

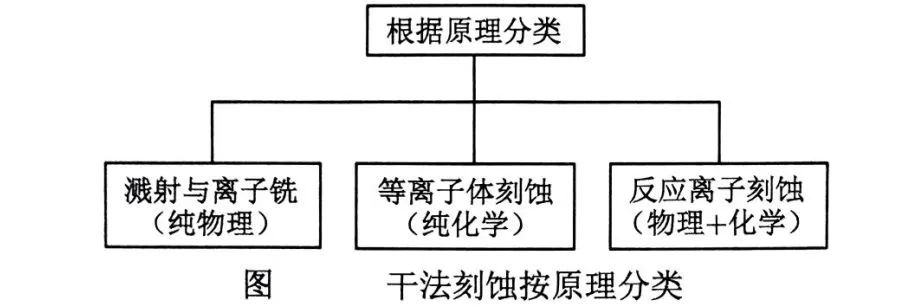

本文系統(tǒng)梳理了刻蝕技術從濕法到等離子體干法的發(fā)展脈絡,解析了物理、化學及協(xié)同刻蝕機制差異,闡明設備與工藝演進對先進制程的支撐作用,并概述國內外產業(yè)格局,體現(xiàn)刻蝕在高端

聚焦離子束(FIB)技術在芯片失效分析中的應用詳解

,形成雙束系統(tǒng)。該系統(tǒng)能夠在微納米尺度上對芯片樣品進行精確加工與高分辨率成像,是定位失效點、分析失效機理的重要工具。FIB的主要功能包括刻蝕、沉積和成像三個方面,下面

芯明天壓電納米技術如何幫助刻蝕機打造精度天花板

在半導體制造流程中,每一塊納米級芯片的誕生,背后都是一場在原子層面展開的極致精密較量。而在這場微觀世界的“精密之戰(zhàn)”中,刻蝕機堪稱光刻機的最佳搭檔,二者協(xié)同發(fā)力,推動著

干法刻蝕的評價參數(shù)詳解

在MEMS制造工藝中,干法刻蝕是通過等離子體、離子束等氣態(tài)物質對薄膜材料或襯底進行刻蝕的工藝,其評價參數(shù)直接影響器件的結構精度和性能。那么干法刻蝕

遠程等離子體刻蝕技術介紹

遠程等離子體刻蝕技術通過非接觸式能量傳遞實現(xiàn)材料加工,其中熱輔助離子束刻蝕(TAIBE)作為前沿技術,尤其適用于碳氟化合物(FC)材料(如聚四氟乙烯PTFE)的精密處理。

中微公司首臺金屬刻蝕設備付運

集成電路研發(fā)設計及制造服務商。此項里程碑既標志著中微公司在等離子體刻蝕領域的又一自主創(chuàng)新,也彰顯了公司持續(xù)研發(fā)的技術能力與穩(wěn)步發(fā)展的綜合實力。

芯片刻蝕原理是什么

芯片刻蝕是半導體制造中的關鍵步驟,用于將設計圖案從掩膜轉移到硅片或其他材料上,形成電路結構。其原理是通過化學或物理方法去除特定材料(如硅、金屬或介質層),以下是芯片刻蝕的基本原理和分類: 1. 刻蝕

半導體刻蝕工藝技術-icp介紹

ICP(Inductively Coupled Plasma,電感耦合等離子體)刻蝕技術是半導體制造中的一種關鍵干法刻蝕工藝,廣泛應用于先進集成電路、MEMS器件和光電子器件的加工。以下是關于ICP

半導體boe刻蝕技術介紹

泛應用。以下是其技術原理、組成、工藝特點及發(fā)展趨勢的詳細介紹: 一、技術原理 BOE刻蝕液是一種以氫氟酸(HF)和氟化銨(NH?F)為基礎的緩沖溶液,通過化學腐蝕作用去除半導體表面的氧化層(如SiO?、SiN?)。其核心反應機制包括: 氟化物離子攻擊: 氟化銨(NH?

【「芯片通識課:一本書讀懂芯片技術」閱讀體驗】芯片怎樣制造

芯片委托加工合同并拿到客戶的電路版圖數(shù)據(jù)后,首先要根據(jù)電路版圖數(shù)據(jù)制作成套的光掩膜版。

晶圓上電路制造

準備好硅片和整套的光掩膜版后,芯片制造就進入在警員上制造電路的流程。

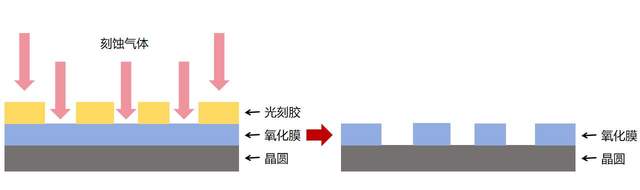

晶圓上電路制造流程:薄膜/氧化→平坦化→光刻膠涂布→光刻→刻蝕

發(fā)表于 04-02 15:59

【「芯片通識課:一本書讀懂芯片技術」閱讀體驗】了解芯片怎樣制造

工藝流程: 芯片設計,光掩模版制作,晶圓上電路制造,(薄膜氧化,平坦化,光刻膠涂布,光刻,刻蝕,離子注入擴散,裸片檢測)

發(fā)表于 03-27 16:38

中微公司ICP雙反應臺刻蝕機Primo Twin-Star取得新突破

近日,中微半導體設備(上海)股份有限公司(以下簡稱“中微公司”,股票代碼“688012.SH”)宣布通過不斷提升反應臺之間氣體控制的精度, ICP雙反應臺刻蝕機Primo Twin-Star 又取得新的突破,反應臺之間的刻蝕精度

濕法刻蝕:晶圓上的微觀雕刻

在芯片制造的精密工藝中,華林科納濕法刻蝕(Wet Etching)如同一把精妙的雕刻刀,以化學的魔力在晶圓這張潔白的畫布上,雕琢出微觀世界的奇跡。它是芯片制造中不可或缺的一環(huán),以其高效、低成本的特點

離子刻蝕機 解剖芯片

離子刻蝕機 解剖芯片

評論