來源:群星結局

總所周知,一般我們在對通信芯片互連的時候,要求兩者的IO接口電平標準是一樣的,而在學習FPGA與DDR互連的時候,查看網上的資料卻很少提及這方面,都是直接教你怎么連接,不明所以,所以這里簡單做了下筆記。

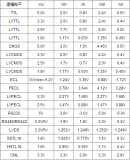

SSTL邏輯電平

SSTL邏輯電平一般用在DDR SDRAM存儲接口上,與DRAM標準協議有關:

SSTL_25 IO標準適用于DDR SDRAM存儲接口(2.5V);

SSTL_18 IO標準適用于DDR2 SDRAM存儲接口(1.8V);

SSTL_15 IO標準適用于DDR3 SDRAM存儲接口(1.5V);

SSTL_135 IO標準適用于DDR3L SDRAM存儲接口(1.35V);

SSTL_12 IO標準適用于DDR4 SDRAM存儲接口(1.2V);

一般CPU的IO和DDR都會默認兼容SSTL邏輯電平,所以不需要邏輯電平轉換。

SSTL電路結構

常見的LVTTL(Low-Voltage TTL)是由TTL發展而來,TTL一般指的是5V邏輯電平,LVTTL則小于3.6V。CMOS和LVCMOS電平同理。

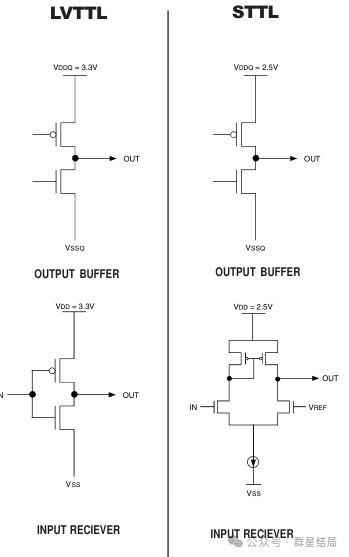

LVTTL和SSTL電路結構如下:

LVTTL的輸入和輸出都采用CMOS逆變器結構,由一對增強型NMOS和PMOS組成,結構簡單,但是由于這種結構在工藝、溫度上匹配較差,所以開啟閾值電壓較大,進而保證可靠的開關。

SSTL的輸出端和LVTTL類似,最大不同是輸入端采用差分電路,輸入信號與Vref參考電壓比較,使得在輸入電壓波動小的情況下也能實現較大的輸出,再給到后面的電路。

SSTL_15

這里以DDR3使用的SSTL_15為例,Xilinx的7系列FPGA的IO支持各種電平標準,其中就包括DDR3的SSTL_15,SSTL_15又分為SSTL_15和SSTL_15_R,區別在于驅動電流大小。

| SSTL_15 | SSTL_15_R | |

|---|---|---|

| Available I/O Bank Type | HR、HP | HR |

| Drive strength | full-strength | weaker-strength |

對于單片DDR3,使用SSTL_15_R有助于減小信號過沖和提高信號完整性,多片DDR3還是建議使用SSTL_15。

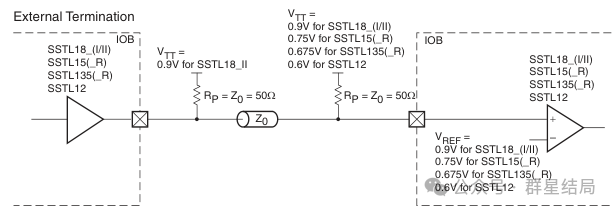

端接要求

對于HR BANK上的單端單向信號,因為內部沒有DCI功能(數字阻抗控制功能,DCI可以控制輸出驅動阻抗或者添加并行端接在驅動器或者接收器,精確匹配傳輸線阻抗,保證信號傳輸完整性,只有HP有這個功能),需要使用外部并聯端接匹配。對于SSTL_15,只需要在接收端加上拉電阻。

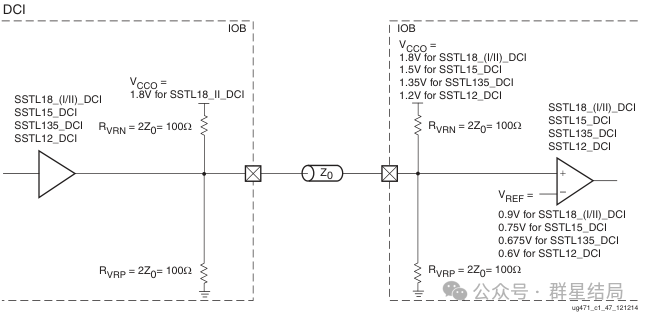

對于HP BANK上的單端單向信號,因為內部有DCI功能,不需要使用外部并聯終端匹配。

以上是單端單向信號,對應DDR3上就是地址總線、命令和控制線。

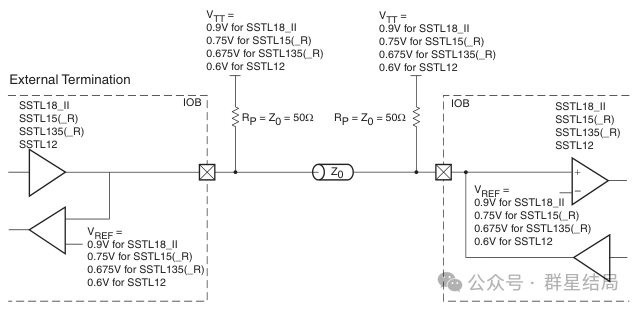

同理,對于HR BANK上單端雙向信號,需要在兩端都加上并聯端接:

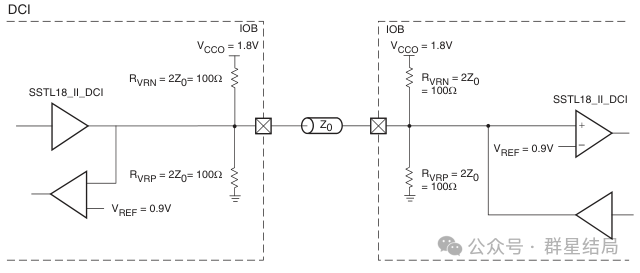

對于HP BANK上單端雙向信號:

以上是單端雙向信號,對應DDR3上就是數據總線。

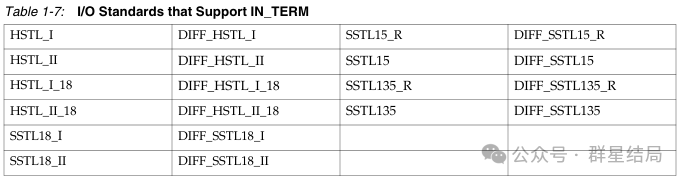

對于常見的A7系列,因為基本上都是HR BANK,所以沒有DCI功能,那么為什么大部分原理圖,DDR3的數據總線都沒有在FPGA一側增加并聯端接呢?這是因為HR BANK為IO增加了可選的IN_TERM屬性,可以為IO增加戴維南等效并聯端接,該選項的目標等效電阻值可以為40Ω、50Ω和60Ω;缺點是不能進行校準,會受到溫度和電壓變化的影響,而DCI就能校準外部電阻,克服這些問題。

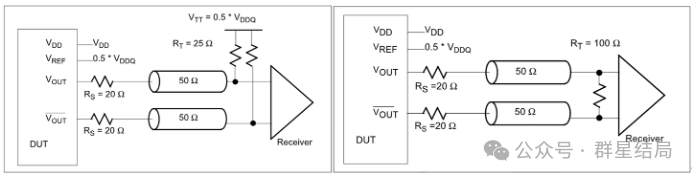

對于HR BANK上差分單向信號,有兩種端接方式,一種是在各自單端線路上加并聯端接,另一種是在差分線路之間加并聯端接:

對于HP BANK上差分單向信號則可以使用DCI功能。

以上差分單向信號就對應DDR3的時鐘線。

-

SDRAM

+關注

關注

7文章

449瀏覽量

57233 -

DDR3

+關注

關注

2文章

287瀏覽量

43880 -

接口

+關注

關注

33文章

9417瀏覽量

155991 -

邏輯電平

+關注

關注

0文章

203瀏覽量

14993

原文標題:DDR的邏輯電平標準

文章出處:【微信號:封裝與高速技術前沿,微信公眾號:封裝與高速技術前沿】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

邏輯電平介紹

快點PCB原創∣詳解信號邏輯電平標準

邏輯電平詳細介紹

DDR SRAM與HSTL電平標準

信號邏輯電平標準的詳細說明

信號邏輯電平的標準詳細說明

淺談DDR的邏輯電平標準

淺談DDR的邏輯電平標準

評論