基于Vitis Model Composer進行AI Engine(AIE)開發,核心優勢體現在AIE專屬優化、開發流程簡化、靈活的適配性、高效驗證及量產適配等方面,具體如下:

專屬優化的AI Engine庫,降低基礎開發成本:提供AIE專用DSPLib庫,包含FFT、FIR等預制模塊,適配AIE架構且同步開源生態,無需重復開發基礎算法。

靈活的AIE代碼導入方式,適配多樣開發需求:支持AIE Kernel、Class Kernel、Graph三種導入形式,兼容緩沖區/流數據訪問,適配不同開發場景。

簡化的AIE專屬開發流程,提升開發效率:在Simulink環境中直觀搭建設計,支持中間信號查看與調試,降低開發門檻。

自動化代碼生成,簡化編程流程:一鍵生成ADF graph、Makefile、Testbench等代碼,無需手動適配底層架構。

適配動態場景,配置高度靈活:支持Variable-sized Signals,可建模動態數據處理,支持自定義約束,靈活調整性能。

精準的AIE仿真與調試,保障設計正確性:支持功能與高精度仿真,快速驗證設計正確性,確保算法與硬件特性匹配。

01環境準備

Ubuntu 22.04

Vitis 2025.1(必須是選擇Vitis完整安裝流程,不能是Vivado ML Enterprise安裝)

Vitis Model Composer

MATLAB R2024b

02獲取Vitis_Libraries

gitclonehttps://gitee.com/light007/Vitis_Libraries.git

03下載依賴文件

gitclonehttps://gitee.com/qinzhusheng/vmc_duc.git

04啟動Model Composer

#!/bin/bash # 設置 Vitis 環境 source/tools/Xilinx//2025.1/Vitis/settings64.sh # 設置 Model Composer 環境 source/tools/Xilinx/2025.1/Model_Composer/settings64.sh # 設置 MATLAB 路徑 exportPATH=$PATH:/tools/MATLAB/R2024b/bin # 啟動 Model Composer model_composer

上述的路徑需要修改為實際運行環境的安裝路徑。

05在Simulink中創建空白模型

5.1在MATLAB Command Window輸入以下命令切換到工作目錄,$WORK_PATH需替換為實際目錄。

cd/$WORK_PATH/vmc_duc/lab

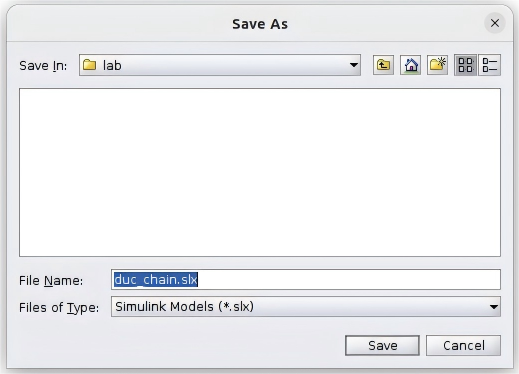

5.2在MATLAB Command Window輸入以下命令創建并打開空白模型。

new_system('duc_chain')

open_system('duc_chain')

按Ctrl+S保存到/$WORK_PATH/vmc/lab目錄內。

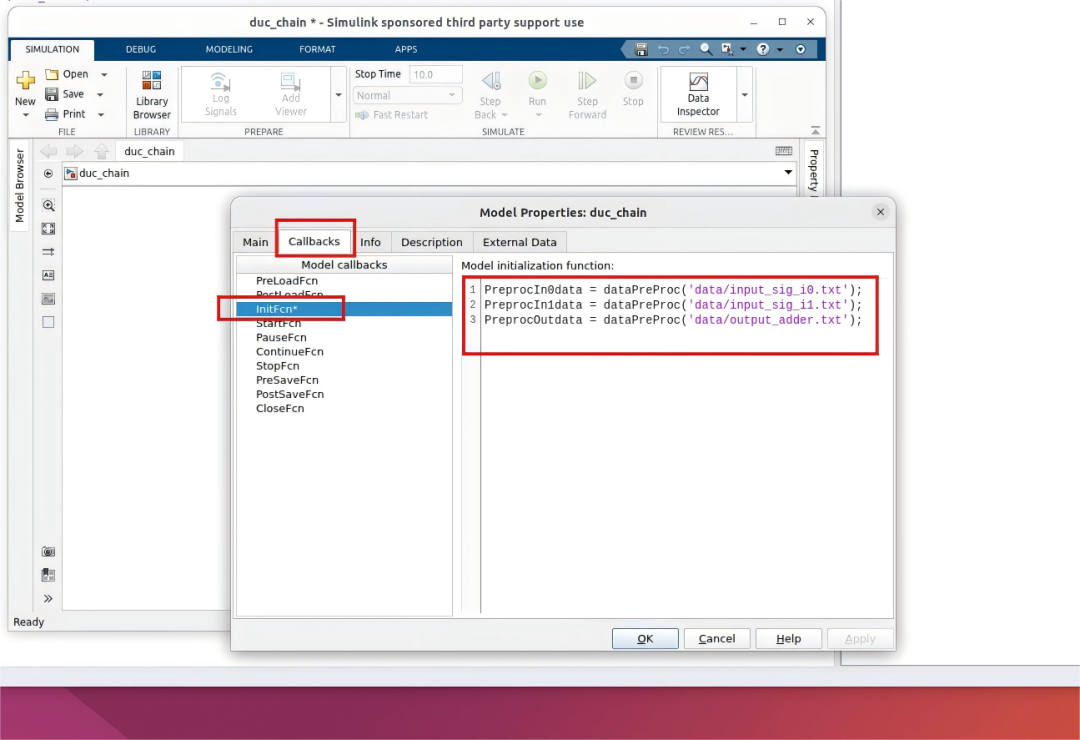

06添加模型初始化函數

6.1回到duc_chain.slx,右鍵空白處,選擇Model Properties,點擊Callbacks窗口,點擊InitFcn,在右側的框口中輸入下面的腳本:

PreprocIn0data= dataPreProc('data/input_sig_i0.txt');

PreprocIn1data= dataPreProc('data/input_sig_i1.txt');

PreprocOutdata= dataPreProc('data/output_adder.txt');

6.2點擊OK完成設置。

這些模型初始化函數在設計更新或模擬運行時會自動調用dataPreProc.m filter配置腳本。

該filter配置腳本會設置以下內容:

Input 0模塊的輸入數據變量PreprocIn0data

Input 1模塊的輸入數據變量PreprocIn1data

Golden_Adder 模塊的輸出數據變量PreprocOutdata

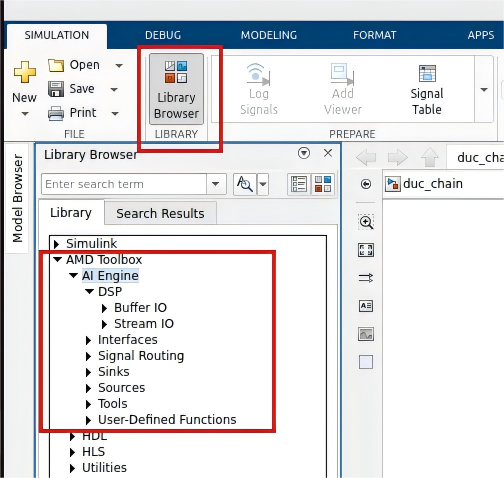

07查看AI Engine library

按Ctrl+Shift+L打開Library Browser,展開AMD Toolbox,可看到AI Engine的模型library。

AI Engine library包含:

用于導入Versal AI Engine使用的kernels和graphs

與FIRs、FFTs、Mixers和直接數字合成器相關的AI Engine DSP模塊

08添加FIR Resampler Filter

8.1依次展開AMD Toolbox>AI Engine>DSP>Buffer IO library,找到FIR Resampler Filter。

8.2按住左鍵將FIR Resampler Filter拖入到duc_chain.slx當中,雙擊進行配置,按圖中紅框部分進行修改,配置為一個3/2分數采樣器,實際采樣點數為71個。

Filter coefficients:

[-8,-15,2,27,38,-1,-67,-86,1,139,171,-2,-257,-309,2,443,522,-3,-724,-842,4,1144,1324,-4,-1789,-2078,5,2866,3402,-5,-5080,-6495,6,13412,27026,32762,27026,13412,6,-6495,-5080,-5,3402,2866,5,-2078,-1789,-4,1324,1144,4,-842,-724,-3,522,443,2,-309,-257,-2,171,139,1,-86,-67,-1,38,27,2,-15,-8]

8.3點擊OK完成配置。

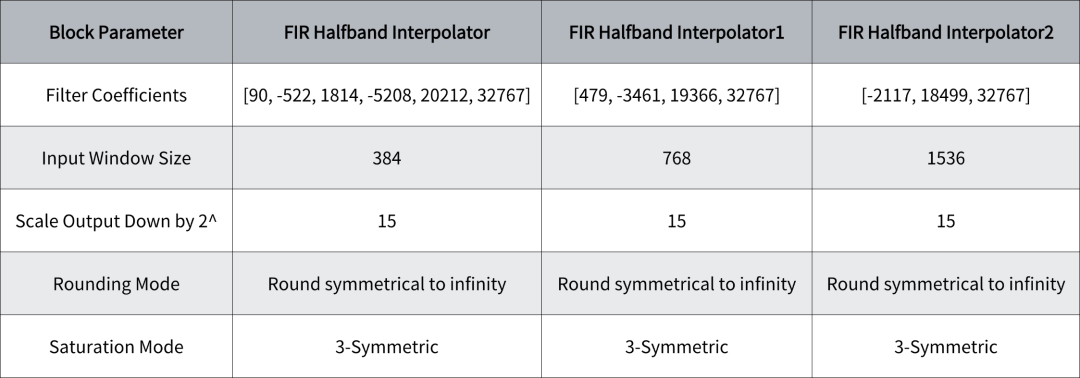

09添加三個FIR Halfband Interpolator blocks

9.1依次展開AMD Toolbox>AI Engine>DSP>Buffer IO library,找到FIR Halfband Interpolator。

9.2按住左鍵將FIR Halfband Interpolator拖入到duc_chain.slx當中,重復三次添加三個FIR Halfband Interpolator,依次雙擊配置,配置如下:

10添加Mixer

10.1依次展開AMD Toolbox>AI Engine>DSP>Buffer IO library,找到Mixer。

10.2按住左鍵將Mixer拖入到duc_chain.slx當中,配置如下:

Input window size (Number of samples): 3072

Rounding mode: Round symmetrical to infinity

Saturation mode: 3-Symmetric

Phase Increment: 715827883

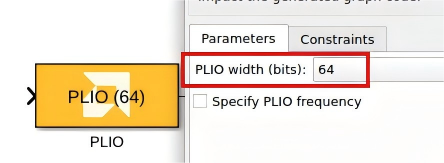

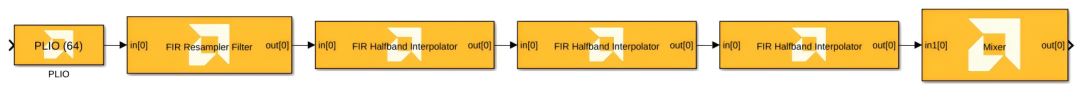

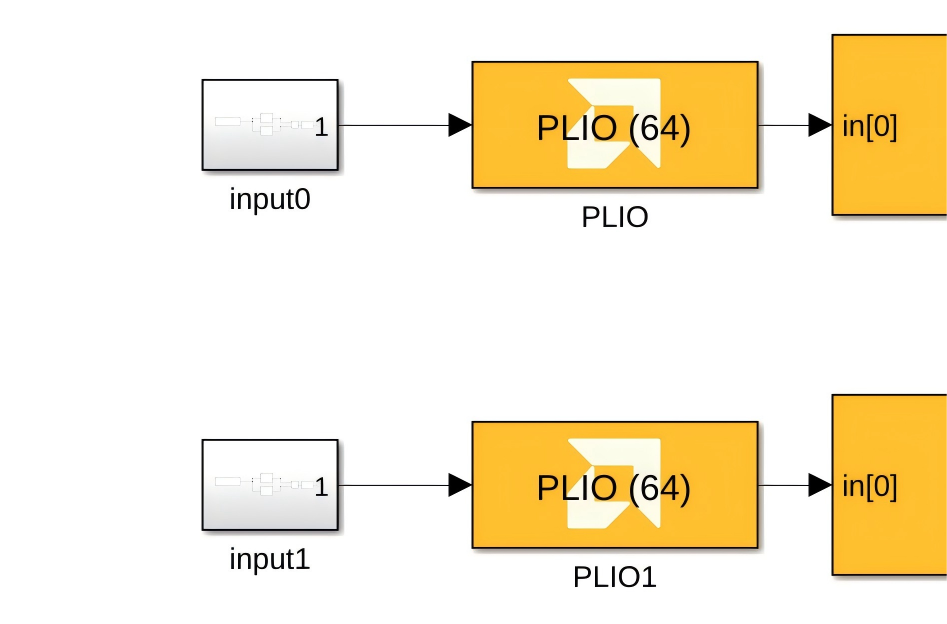

11添加PLIO

依次展開AMD Toolbox>AI Engine>Interfaces library,找到PLIO,按住左鍵將PLIO拖入到duc_chain.slx當中,雙擊修改如下配置:

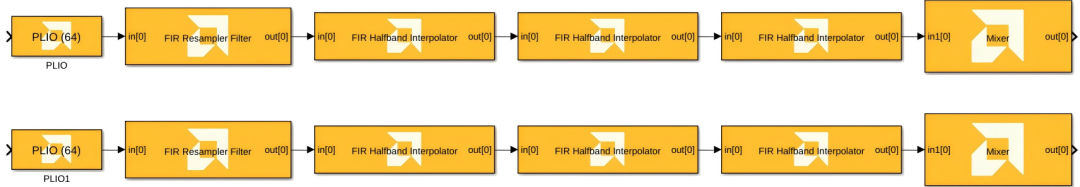

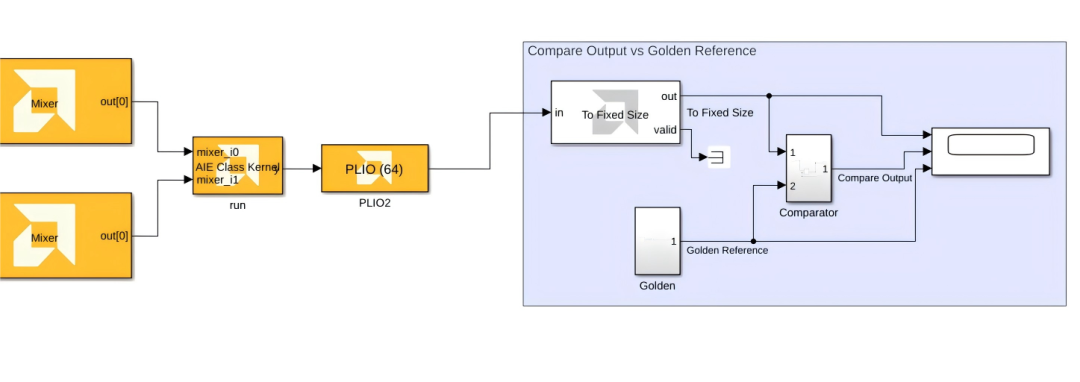

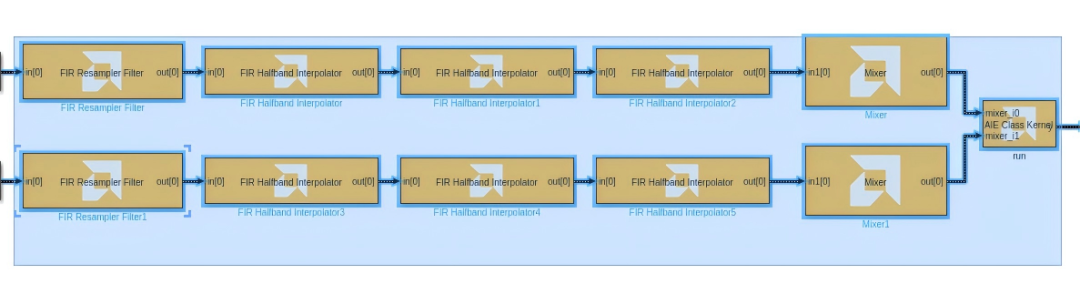

將各模塊按下圖連接。

按住左鍵框選上面的所有blocks,復制并粘貼出另一信號通道,如下圖所示:

雙擊粘貼出來的Mixer,把Phase Increment修改為3042268501。

12從Reference_design_blocks內復制信號輸入模塊

在MATLAB Command Window輸入以下命令打開本設計參考模塊合集。

Reference_design_blocks

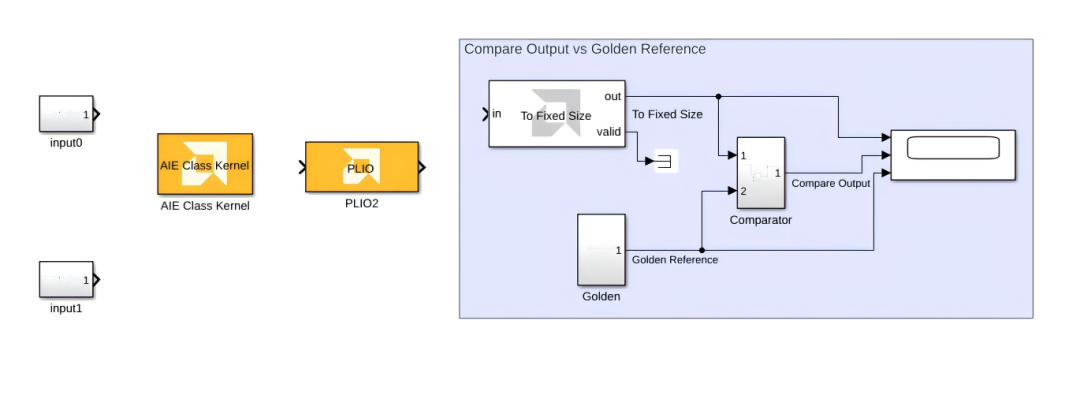

復制如下幾個blocks到duc_chain.slx當中。

這些模塊主要是包含預定義的信號輸入、用Simulink原生blocks搭建的對比模塊、用于自定義AIE block的AIE Class Kernel以及相減對比結果的波形查看器。

修改粘貼出來的PLIO2 block的配置PLIO width(bits):64

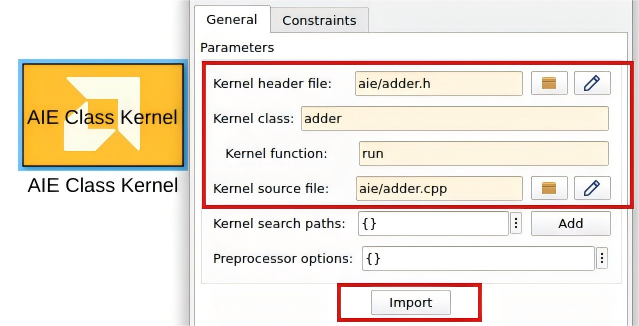

13配置自定義AIE block的AIE Class Kernel

雙擊AIE Class Kernel打開配置窗口,按下圖配置點擊Import導入C++設計的AIE加法器Kernel。

14完成所有模塊的連接

把未連接的模塊按如下示意分別連接信號輸入和輸出。

15添加Vitis Model Composer Hub block

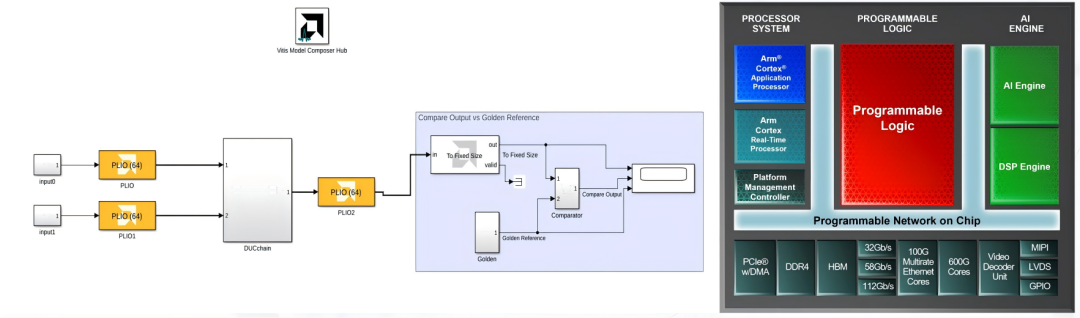

Vitis Model Composer Hub block本質是個控制面板,用于控制系統與仿真參數、選擇AMD芯片板卡型號以及調用代碼生成流程。

只要Simulink模型包含AMD Toolbox的任一Block,就必須添加Vitis Model Composer Hub block,才能進行自定義代碼生成和仿真。

15.1依次展開AMD Toolbox>Utilities>Code Generation,找到Vitis Model Composer Hub block,按住左鍵將其拖入到duc_chain.slx當中。

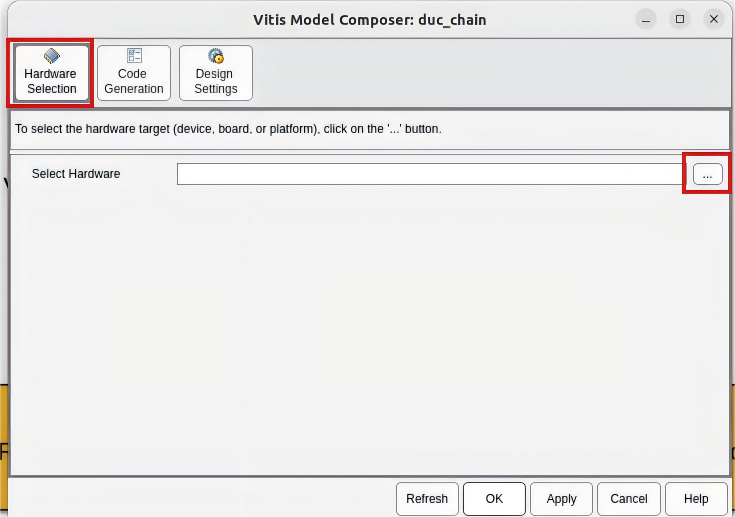

15.2雙擊Vitis Model Composer Hub block打開配置窗口,點擊右側紅框的按鈕打開硬件平臺選擇窗口。

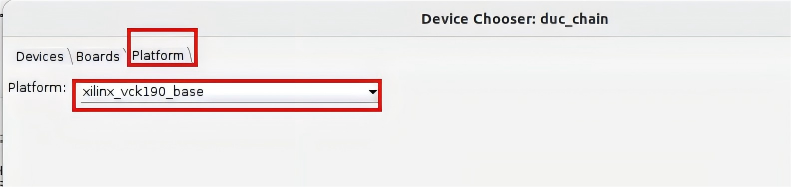

15.3選擇platform窗口,下拉選擇VCK190,點擊OK關閉窗口。

15.4點擊OK關閉Vitis Model Composer Hub block配置窗口。

16編譯工程并運行仿真

16.1按Ctrl+S保存工程,按Ctrl+D執行編譯,等待編譯完成。

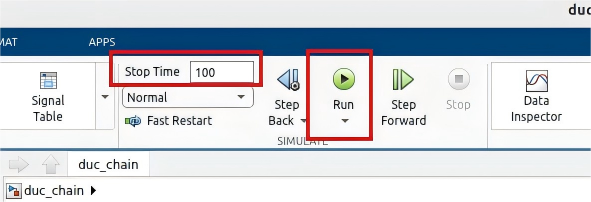

16.2把仿真的停止時間設置為100,點擊Run運行仿真。

16.3仿真結果,中間一個窗口波形是AIE仿真結果和Simulink對照組相減后的結果,可以從波形上看到基本為0,說明AIE仿真結果達到預期效果。

17創建子系統并生成graph代碼

17.1按住左鍵選中如下的Blocks。

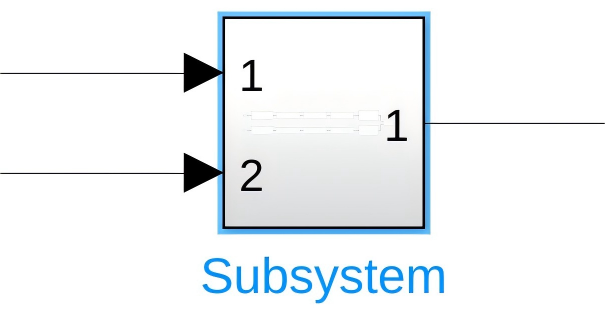

17.2按Ctrl+G將這些Blocks創建為一個子系統,如下圖所示。

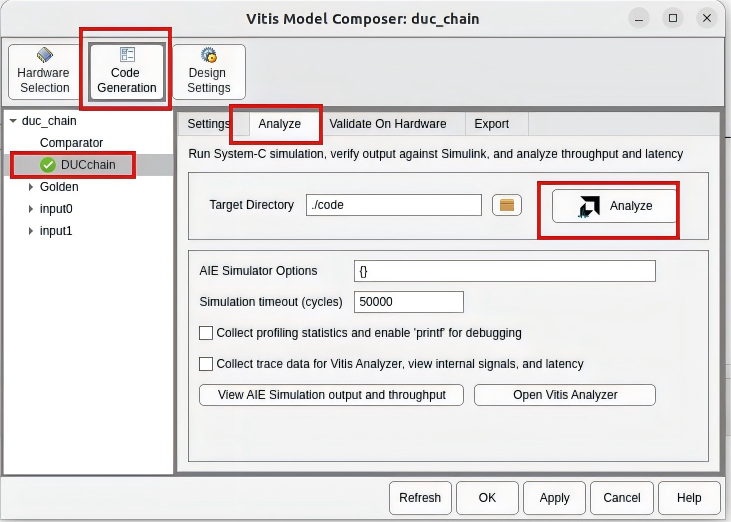

17.3雙擊上圖藍色部分,把子系統重命名為DUCchain,雙擊Vitis Model Composer Hub block打開配置窗口,點擊Code Generation窗口,選中DUCchain,右側窗口切換到Analyze,點擊Analyzer按鈕。

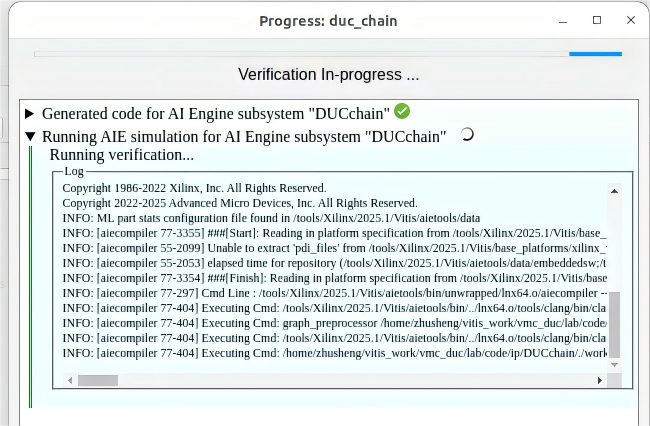

17.4隨后會自動運行仿真、編譯生成graph代碼。

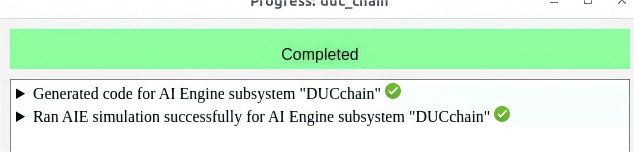

17.5完成后如下圖所示,點擊。

17.6生成的graph源代碼在如下目錄中。

/$WORK_PATH/vmc_duc/lab/code/ip/DUCchain/src

通過上述流程,可基于Vitis Model Composer完成從模型搭建、配置、仿真驗證到代碼生成的全流程AIE開發。借助其可視化設計與自動化工具鏈,能顯著降低開發復雜度,提升設計效率與可靠性,為AIE應用的快速實現提供有力支撐。

關于安富利

安富利是全球領先的技術分銷商和解決方案提供商,在過去一個多世紀里一直秉持初心,致力于滿足客戶不斷變化的需求。通過遍布全球的專業化和區域化業務覆蓋,安富利可在產品生命周期的每個階段為客戶和供應商提供支持。安富利能夠幫助各種類型的公司適應不斷變化的市場環境,在產品開發過程中加快設計和供應速度。安富利在整個技術價值鏈中處于中心位置,這種獨特的地位和視角讓其成為了值得信賴的合作伙伴,能夠幫助客戶解決復雜的設計和供應鏈難題,從而更快地實現營收。

-

仿真

+關注

關注

55文章

4505瀏覽量

138499 -

AI

+關注

關注

91文章

40353瀏覽量

301932 -

ENGINE

+關注

關注

0文章

8瀏覽量

7475 -

Vitis

+關注

關注

0文章

157瀏覽量

8385

原文標題:AMD技術干貨 | 基于Vitis Model Composer進行AIE開發

文章出處:【微信號:AvnetAsia,微信公眾號:安富利】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于Vitis Model Composer完成全流程AI Engine開發

基于Vitis Model Composer完成全流程AI Engine開發

評論