Intel的聯(lián)合創(chuàng)始人戈登·摩爾是半導體業(yè)界黃金定律“摩爾定律”的提出者,Intel公司50多年來也是這一定律最堅定的捍衛(wèi)者。但是這幾年來,Intel自己反而在制程工藝上掉隊了,甚至被小兄弟AMD用7nm超越了,今年的場面一度十分尷尬。

不過AMD對工藝趕超Intel一事也很意外,而且他們很清楚地知道Intel公司會搞定眼前的困難的,CPU架構(gòu)及工藝上絕不可能輕敵,Intel現(xiàn)在只是在進度上落后了,并不代表他們沒技術(shù)。

日前Intel也給自己的2019年做了一個總結(jié),其中多次提到了摩爾定律及自家的工藝進展。Intel指出2019年他們供應了更多的芯片以滿足市場需求,其中10nm工藝的就有Ice Lake及Agilex FPGA兩款產(chǎn)品進入了HVM大規(guī)模量產(chǎn)階段。

此外,Intel還重申他們在未來會重新回到2年一個周期的工藝升級路線上來,7nm工藝將在2021年推出,目前進展順利,而5nm工藝研發(fā)也已經(jīng)開始,這些先進的工藝將使得晶體管越來越小,集成度更高。

不過Intel依然沒有公布7nm及5nm工藝的具體細節(jié),我們現(xiàn)在知道的是7nm會是Intel首個使用EUV光刻技術(shù)的工藝,2021年首發(fā)于7nm Xe架構(gòu)的數(shù)據(jù)中心芯片Ponte Vecchio,至于5nm工藝的進度及技術(shù)就欠奉了。

對Intel來說,2021年倒是好期待,但是難題在于2020年,10nm芯片今年只是出貨了面向移動市場的低功耗版Ice Lake,高性能版的桌面版、服務器版Ice Lake要到明年下半年,在這之前14nm處理器還要再維持一兩代。

責任編輯:wv

-

cpu

+關(guān)注

關(guān)注

68文章

11279瀏覽量

224995 -

intel

+關(guān)注

關(guān)注

19文章

3508瀏覽量

191290

發(fā)布評論請先 登錄

SMT工藝革新:高精度貼裝與微型化組裝的未來趨勢

0.2nm工藝節(jié)點的背后需要“背面供電”支撐

1600TOPS!美國新勢力車企自研5nm芯片,轉(zhuǎn)用激光雷達硬剛特斯拉

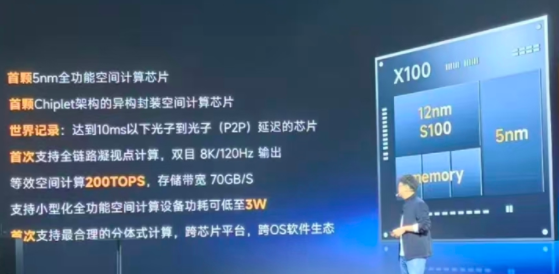

中國首顆全功能空間計算芯片發(fā)布 極智G-X100 5nm工藝

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產(chǎn)業(yè)的前沿技術(shù)

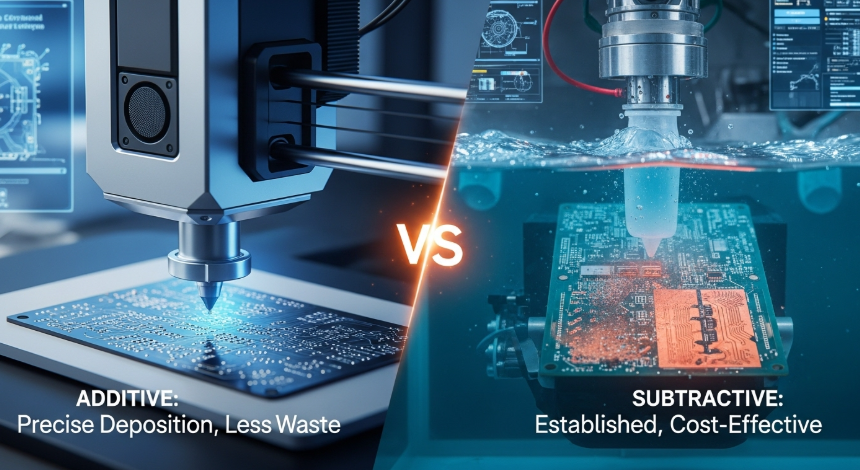

PCB工藝路線詳解:加成法 vs 減成法,一文讀懂核心差異與未來趨勢

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+工藝創(chuàng)新將繼續(xù)維持著摩爾神話

三星代工大變革:2nm全力沖刺,1.4nm量產(chǎn)延遲至2029年

SMA接頭創(chuàng)新設計:材料、工藝與功能升級

下一代高速芯片晶體管解制造問題解決了!

PCB表面處理丨沉錫工藝深度解讀

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現(xiàn)流片成功

Intel重申未來將重新回到2年一個周期的工藝升級路線 5nm工藝研發(fā)也已經(jīng)開始

Intel重申未來將重新回到2年一個周期的工藝升級路線 5nm工藝研發(fā)也已經(jīng)開始

評論