曾經為PCB設計的電路越來越多地在FPGA或CPLD中實施,原因有幾個。

首先,工業,商業消費電子市場對制造商施加持續的壓力,使電子設備小型化。手機,無線電子郵件設備,MP3播放器和PDA是當今尖端設計的展示技術。接下來,隨著電路變得更加充分或主要是數字化,PLD成為PCB的可行替代品。當PLD進一步處理更大的電路尺寸時,尤其如此(最先進的FPGA現在提供數十萬或數百萬個門)。最后,成本可以降低 - FPGA的價格可能遠遠低于成品板的價格。更小,更便宜,更有市場,更可靠。

多年來,EDA工具為PCB工程師提供了一個復雜,靈活和高效的設計環境。隨著用戶越來越多地使用PLD,成千上萬的工程師需要在他們的EDA工具中使用新的技能和功能,以學習PLD設計流程并成功地將他們現有的PCB設計遷移到PLD。

PLD需要的技術與用于PCB的技術不同。設計輸入通常使用HDL文本編輯器而不是原理圖捕獲和模擬來完成,通常使用VHDL或Verilog代替SPICE。這些差異意味著工程師直接進行了許多技術和實際的改變,因為CPLD/FPGA有太多的門作為原理圖輸入或在SPICE的晶體管級模擬。但是,目前可用的最先進軟件可以為用戶提供靈活性,可以將所有這些功能結合使用(原理圖和HDL設計輸入,SPICE和VHDL/Verilog等),從而無需學習許多不同的工具。

傳統模擬器正在發展為將SPICE,VHDL和Verilog仿真引擎集成到單個協同仿真環境中。協同仿真是多個仿真引擎實時交互的能力。這對PLD設計師來說尤為重要。它允許用戶執行,例如,在PCB上實現的電路的原理圖捕獲,同時使用完全編程或建模的FPGA/CPLD作為電路板上的一些組件。利用這項新技術,工程師可以使用HDL文本輸入和仿真設計PLD,然后對PCB的其余部分采用原理圖捕獲(利用現在建模的PLD),然后一次性透明地模擬整個電路板。在這種方法中,FPGA/CPLD使用VHDL或Verilog代碼作為其模型,而其他分立部件或不太復雜的IC使用SPICE。通過SPICE,VHDL和Verilog在后臺進行交互,用戶可以看到集成的仿真結果,并在考慮可編程器件的情況下顯示電路板的整體行為。順便說一下,共同模擬的能力對于想要模擬其他不可編程但仍然很復雜的數字IC(微處理器等)的用戶同樣有益,而這些數字IC實際上并未在SPICE中建模。

直接在PCB級電路中對可編程器件進行協同仿真,是對利用測試平臺驗證CPLD/FPGA行為的標準技術的完美補充。最后,在PLD設計流程中,傳統的電路板布局/布線被合成和布局布線的步驟所取代。在大多數情況下,通常直接從可編程設備供應商處獲取合成和布局布線工具。

采用當今最強大且易于使用的設計軟件它集成了SPICE和HDL建模組件,使用原理圖和HDL進行設計輸入以及協同仿真,傳統PCB設計人員現在可以在一個集成設計環境中設計,構建和測試PLD。 Multisim等工具允許用戶逐步調整從PCB僅遷移到PCB和PLD設計所需的技能,同時避免陡峭的恐嚇學習曲線。而且,更好的是,FPGA/CPLD功能可以作為真實PCB級電路的一部分進行驗證,它將在現實世界中運行。

-

pcb

+關注

關注

4405文章

23878瀏覽量

424345 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

44640

發布評論請先 登錄

技術解析|SAP ECC到S/4HANA遷移實戰:50TB數據19小時遷移架構

無質量損失的數據遷移:Nikon SLM Solutions信賴3Dfindit企業版

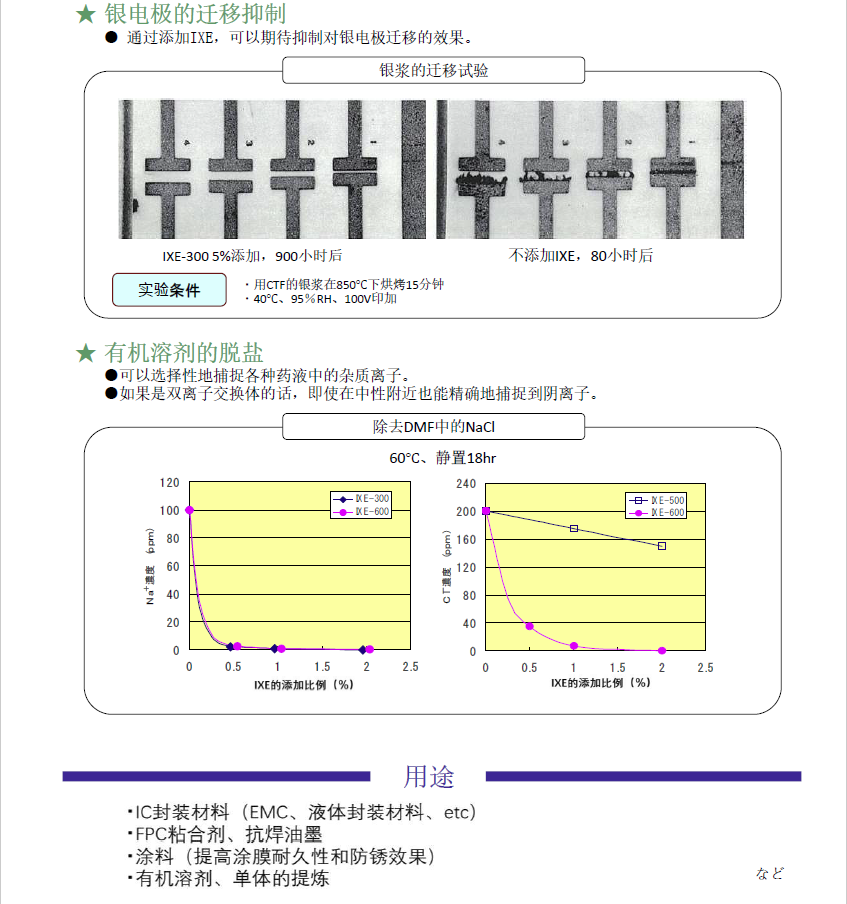

PCB 銀遷移 “終結者”:日本東亞合成 IXE 如何守護精密電路安全?

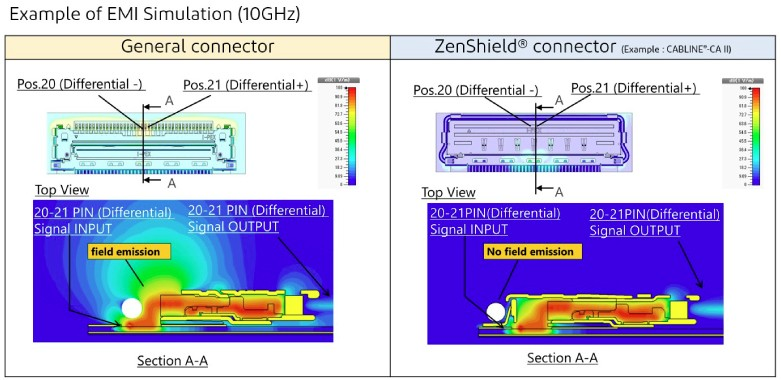

如何管理線束到 PCB 接口的 EMI

借助Cadence工具簡化PCB設計流程

新思科技攜手是德科技推出AI驅動的射頻設計遷移流程

從Altium到KiCad的遷移實踐:多源庫管理方案與Jobset應用技巧

Simcenter FLOEFD EDA Bridge模塊:使用導入的詳細PCB設計和IC熱特性來簡化熱分析

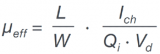

如何精準提取MOSFET溝道遷移率

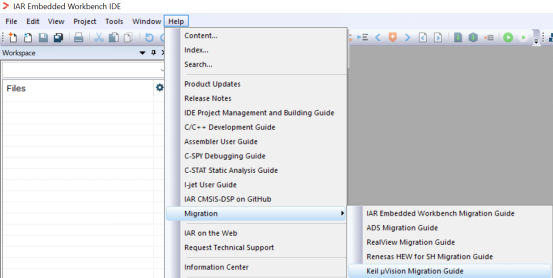

從Keil MDK到IAR EWARM:通過工程遷移實現項目資產的更好管理

Arm助力開發者加速遷移至Arm架構云平臺 Arm云遷移資源分享

KVM主機遷移方法

使用智能工具簡化向Arm平臺的遷移過程

怎樣簡化PCB到PLD的遷移

怎樣簡化PCB到PLD的遷移

評論