Mentor Graphics 公司近日宣布,推出首個完全原生的UVM SystemVerilog內(nèi)存驗證IP庫,該內(nèi)存驗證IP庫可用于所有常用內(nèi)存設(shè)備、配置和接口。目前, Mentor 驗證IP(Mentor VIP)可支持 60 多種常用外設(shè)接口和總線架構(gòu),此次庫中又新增了1600多種內(nèi)存模型。由此,Mentor成為首個向ASIC和FPGA SoC設(shè)計人員提供完整UVM SystemVerilog驗證IP庫的公司,該驗證IP庫可滿足各類外設(shè)接口、總線協(xié)議和內(nèi)存設(shè)備需求。該完整的驗證IP庫采用和行業(yè)一致的標準格式,可縮短工程師驗證運行所需時間,從而便于工程師將關(guān)注重點放在其設(shè)計中獨一無二而高價值的部分。

新推出的內(nèi)存庫支持包括尖端協(xié)議在內(nèi)的各種內(nèi)存模型,例如用于HyperRAM 和HyperFlash內(nèi)存設(shè)備的高帶寬、低管腳數(shù)目的HyperBus接口。此外,它還支持所有的動態(tài)RAM模型,包括DDR4、低功耗DDR4、混合存儲立方體以及HBM-2(高帶寬內(nèi)存),和新的JESD229-2 Wide I/O-2標準。它所涵蓋的閃存模型種類齊全,包括SDIO 4.1、SDCard 4.2、eMMC 5.1、ONFI 4.0、UFS以及串行、Toggle、NAND和NOR 閃存。

賽普拉斯半導體公司(Cypress Semiconductor)產(chǎn)品與產(chǎn)業(yè)生態(tài)系統(tǒng)營銷副總裁 Jackson Huang表示,“我們非常高興Mentor Graphics發(fā)布其全面的內(nèi)存驗證IP模型庫,特別是它支持新的HyperBus接口,我們開發(fā)HyperBus接口的目的在于達成不斷增長的產(chǎn)品性能目標,并在響應時間更快的同時,兼具功能的全面性。”

驗證IP旨在通過為常見接口、協(xié)議和架構(gòu)提供可復用構(gòu)建模塊來幫助工程師減少構(gòu)建測試平臺所花費的時間。Mentor的內(nèi)存驗證IP模型庫所包含的內(nèi)存配置軟件允許客戶根據(jù)供應商、協(xié)議和元件編號,即時生成快速、計時精確和經(jīng)過驗證的內(nèi)存模型。此外,Mentor獨有的“運行過程中可重新配置”架構(gòu)有助于工程師在無需重新編譯或重新開始軟件仿真的情況下,重新對資源進行二次評估。

“ASIC和FPGA項目團隊的大部分人員都已轉(zhuǎn)去研究標準UVM SystemVerilog驗證方法,但時至今日,仍沒能找到可支持原生UVM中總線協(xié)議、外設(shè)接口和內(nèi)存設(shè)備的通用VIP庫,” Mentor Graphics設(shè)計驗證技術(shù)部產(chǎn)品營銷經(jīng)理Mark Olen表示,“根據(jù)我們新推出的內(nèi)存VIP庫的最初使用情況來看,不難看出為什么驗證IP是功能驗證市場中增長最快速的子細分市場之一,據(jù)電子設(shè)計自動化聯(lián)盟統(tǒng)計,目前該子細分市場的年支出超過1.1億美元。”

Mentor VIP庫可向工程師提供標準UVM SystemVerilog元件,這些元件對所有支持的協(xié)議采用通用架構(gòu)。這有助于在同一個驗證團隊內(nèi)快速部署多個協(xié)議。測試計劃、符合性測試、測試序列和協(xié)議覆蓋范圍都作為SV和XML源代碼包含在內(nèi),從而使復用、擴展和調(diào)試變得簡單。Mentor VIP元件還包含一整套協(xié)議檢查、錯誤注入和調(diào)試功能。新推出的存儲器模型可應用于所有行業(yè)標準仿真器。

Mentor VIP是Mentor企業(yè)驗證平臺(EVP)的核心技術(shù)。EVP通過將高級驗證技術(shù)融合在一個綜合性平臺中,提高了ASIC和FPGA的SoC功能驗證效率。Mentor EVP集成了Questa 高級驗證解決方案、Veloce 模擬平臺和Visualizer調(diào)試環(huán)境,是全球可訪問的、高性能的數(shù)據(jù)中心資源。Mentor EVP的全球資源管理功能可為全球的項目團隊提供支持,最大限度地提高用戶生產(chǎn)率和驗證的總投資回報率。

-

半導體

+關(guān)注

關(guān)注

339文章

30737瀏覽量

264104 -

自動化

+關(guān)注

關(guān)注

31文章

5933瀏覽量

90229

發(fā)布評論請先 登錄

RDMA設(shè)計39:寄存器功能驗證與分析

RDMA設(shè)計38:寄存器功能驗證與分析

RDMA設(shè)計35:基于 SV 的驗證平臺

國產(chǎn)高性能ONFI IP解決方案全解析

【產(chǎn)品介紹】Questa One Sim軟件

NMSIS神經(jīng)網(wǎng)絡(luò)庫使用介紹

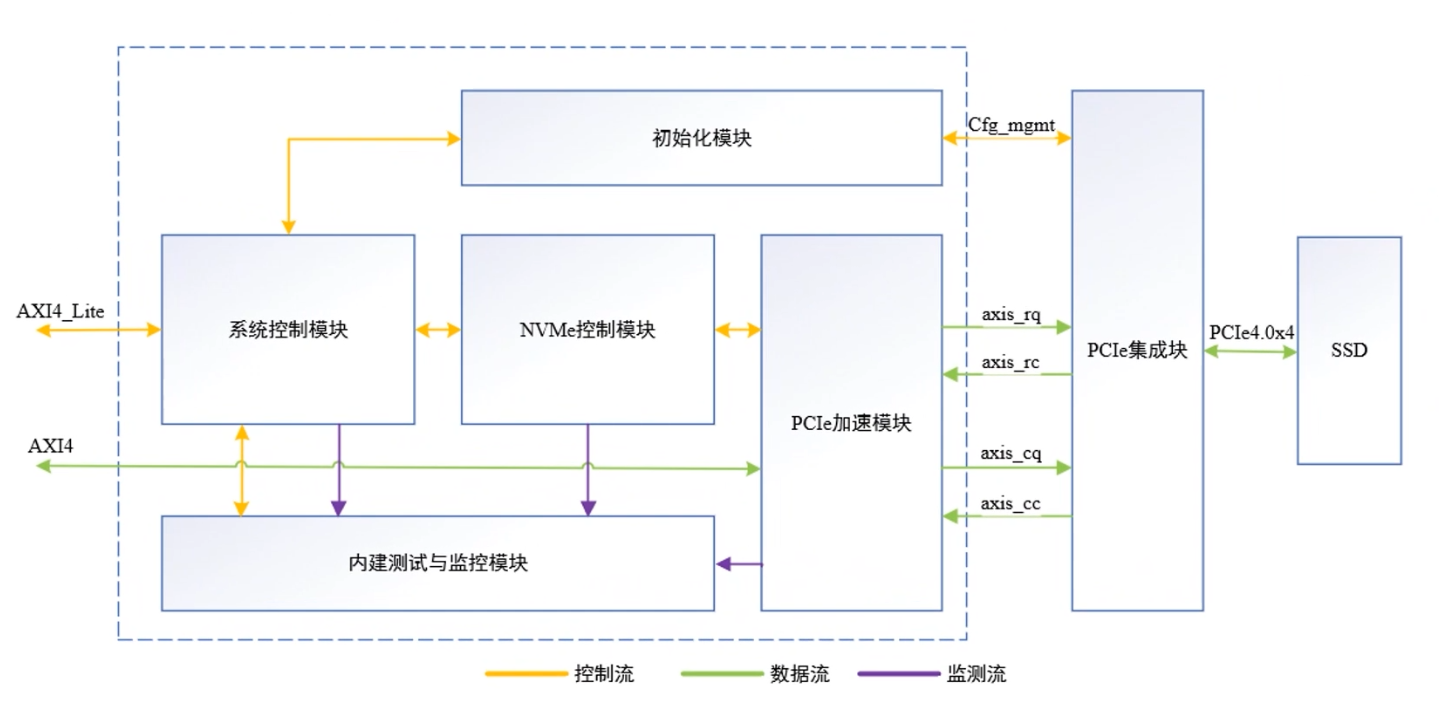

NVMe高速傳輸之擺脫XDMA設(shè)計24: UVM 驗證包設(shè)計

NVMe高速傳輸之擺脫XDMA設(shè)計24: UVM 驗證包設(shè)計

NVMe高速傳輸之擺脫XDMA設(shè)計23:UVM驗證平臺

NVMe高速傳輸之擺脫XDMA設(shè)計18:UVM驗證平臺

如何評估協(xié)議分析儀的性能指標?

NVMe IP over PCIe 4.0:擺脫XDMA,實現(xiàn)超高速!

NVMe IP開發(fā)速成: 三個月不是夢

關(guān)于UVM SystemVerilog驗證IP庫的性能分析和介紹

關(guān)于UVM SystemVerilog驗證IP庫的性能分析和介紹

評論