本設(shè)計(jì)中,計(jì)劃實(shí)現(xiàn)對(duì)文件的壓縮及解壓,同時(shí)優(yōu)化壓縮中所涉及的信號(hào)處理和計(jì)算密集型功能,實(shí)現(xiàn)對(duì)其的加速處理。本設(shè)計(jì)的最終目標(biāo)是證明在充分并行化的硬件體系結(jié)構(gòu) FPGA 上實(shí)現(xiàn)該算法時(shí),可以大大提高該算

2025-07-10 11:09:34 2198

2198

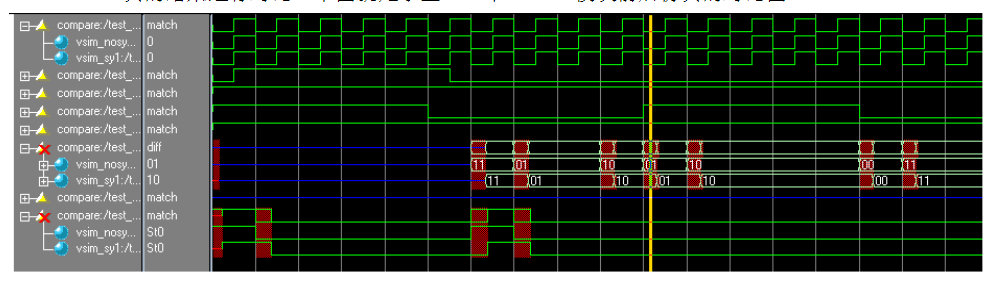

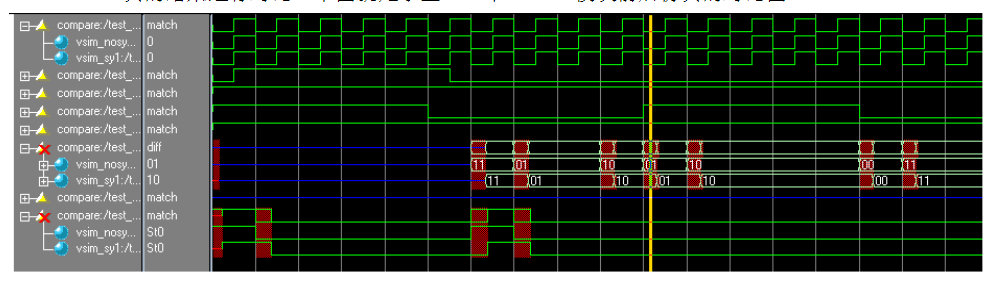

加速。安排如下: 首先基于直方圖算法進(jìn)行FPGA架構(gòu)設(shè)計(jì),這里主要考慮了如何加速以及FPGA資源的利用兩個(gè)因素;最后基于system Verilog搭建一個(gè)驗(yàn)證系統(tǒng)。 FPGA設(shè)計(jì)架構(gòu) 不論是圖像灰度直方圖還是梯度直方圖,本質(zhì)上是對(duì)數(shù)據(jù)的分布進(jìn)行計(jì)數(shù)。從F

2020-12-10 16:37:20 3562

3562 FPGA設(shè)計(jì)流程是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過程。FPGA的設(shè)計(jì)流程如上圖所示:包括設(shè)計(jì)定義、代碼實(shí)現(xiàn)、功能仿真、邏輯綜合、前仿真、布局布線、后仿真和板級(jí)調(diào)試等步驟!

2023-04-04 10:29:51 3088

3088 FPGA原型在數(shù)字芯片設(shè)計(jì)中非常重要,因?yàn)橄啾扔梅抡嫫鳎蛘?b class="flag-6" style="color: red">加速器等來(lái)跑仿真,FPGA的運(yùn)行速度,更接近真實(shí)芯片,可以配合軟件開發(fā)者來(lái)進(jìn)行底層軟件的開發(fā)。這一流片前的軟硬件的協(xié)同開發(fā),是其最不可替代的地方。

2023-05-10 10:44:00 11197

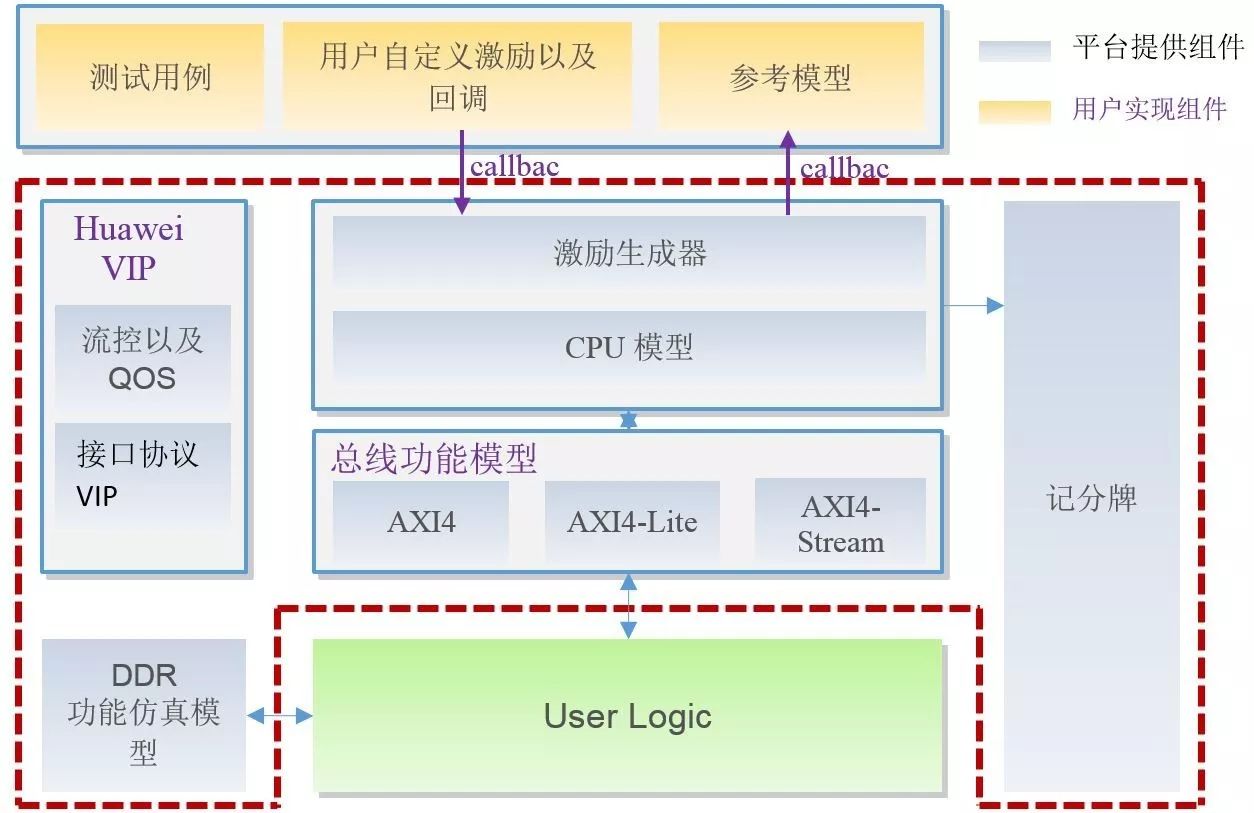

11197

可編程邏輯廠商逐步開始從可編程邏輯芯片供應(yīng)商向可編程邏輯系統(tǒng)商完成華麗轉(zhuǎn)身,正對(duì)EDA工具供應(yīng)商提出更高的要求。鑒于日益升溫的FPGA市場(chǎng),EDA業(yè)者加碼布局,加速FPGA設(shè)計(jì)進(jìn)程、提高驗(yàn)證效率,幫助廣大工程師在短時(shí)間內(nèi)進(jìn)行準(zhǔn)確無(wú)誤的設(shè)計(jì)。

2013-04-17 10:38:59 2629

2629 時(shí)序分析器可以幫助找到延時(shí)最長(zhǎng)的關(guān)鍵路徑,以便設(shè)計(jì)者改進(jìn)設(shè)計(jì)。對(duì)于結(jié)構(gòu)固定的設(shè)計(jì),關(guān)鍵路徑法是進(jìn)行速度優(yōu)化的首選方法,可與其他方法配合使用。---在fpga設(shè)計(jì)中,面積優(yōu)化實(shí)質(zhì)上就是資源利用優(yōu)化,面積

2013-09-02 15:19:20

是借助于EDA開發(fā)工具,用原理圖、狀態(tài)機(jī)、布爾表達(dá)式、硬件描述語(yǔ)言等方法進(jìn)行系統(tǒng)功能及算法描述,設(shè)計(jì)實(shí)現(xiàn)并生成編程文件,最后通過編程器或下載電纜用目標(biāo)器件來(lái)實(shí)現(xiàn)。 FPGA器件采用邏輯單元陣列(LCA

2008-06-26 16:16:11

的自動(dòng)設(shè)計(jì)。EDA是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,在現(xiàn)代集成電路設(shè)計(jì)中占據(jù)重要地位。FPGA(Field Programmable Gate Array,現(xiàn)場(chǎng)可編程門陣列)作為可編程邏輯器件的典型代表,它的出現(xiàn)

2008-06-11 10:26:29

廣泛應(yīng)用在現(xiàn)代數(shù)字系統(tǒng)設(shè)計(jì)中。EDA技術(shù)與FPGA原理1.EDA技術(shù)特征---EDA是電子設(shè)計(jì)領(lǐng)域的一場(chǎng)革命,它源于計(jì)算機(jī)輔助設(shè)計(jì)(CAD,Computer Aided Design)、計(jì)算機(jī)輔助制造

2008-06-27 10:26:34

摘 要:EDA技術(shù)是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,它在現(xiàn)代集成電路設(shè)計(jì)中占據(jù)重要地位。隨著深亞微米與超深亞微米技術(shù)的迅速發(fā)展,FPGA設(shè)計(jì)越來(lái)越多地采用基于VHDL的設(shè)計(jì)方法及先進(jìn)的EDA工具。本文詳細(xì)

2019-06-18 07:33:04

摘 要:EDA技術(shù)是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,它在現(xiàn)代集成電路設(shè)計(jì)中占據(jù)重要地位。隨著深亞微米與超深亞微米技術(shù)的迅速發(fā)展,FPGA設(shè)計(jì)越來(lái)越多地采用基于VHDL的設(shè)計(jì)方法及先進(jìn)的EDA工具。本文詳細(xì)

2019-06-27 08:01:28

FPGA可以設(shè)計(jì)成單片機(jī),但是FPGA設(shè)計(jì)成的單片機(jī)可以用C語(yǔ)言進(jìn)行編程嗎?

2014-12-07 14:07:29

請(qǐng)問:

FPGA可以用來(lái)做數(shù)字電源嗎?有參考設(shè)計(jì)案例嗎?

FPGA和DSP做數(shù)字電源的優(yōu)缺點(diǎn)是什么?

2024-01-08 22:24:13

FPGA(現(xiàn)場(chǎng)可編程門陣列)在人工智能領(lǐng)域的應(yīng)用非常廣泛,主要體現(xiàn)在以下幾個(gè)方面:

一、深度學(xué)習(xí)加速

訓(xùn)練和推理過程加速:FPGA可以用來(lái)加速深度學(xué)習(xí)的訓(xùn)練和推理過程。由于其高并行性和低延遲特性

2024-07-29 17:05:30

FPGA有哪些開發(fā)環(huán)境?可以用VSCode開發(fā)嘛?

2024-04-29 23:05:48

的是,FPGA可以采用IP內(nèi)核技術(shù),以通過繼承、共享或購(gòu)買所需的知識(shí)產(chǎn)權(quán)內(nèi)核提高其開發(fā)進(jìn)度。而利用EDA工具進(jìn)行設(shè)計(jì)、綜合和驗(yàn)證,則可加速設(shè)計(jì)過程,降低開發(fā)風(fēng)險(xiǎn),縮短了開發(fā)周期,效率高而且更能適應(yīng)市場(chǎng)。

2019-11-01 07:40:10

到了廣泛應(yīng)用。在通信領(lǐng)域,FPGA可以用于實(shí)現(xiàn)協(xié)議轉(zhuǎn)換、信號(hào)處理、高速數(shù)據(jù)傳輸?shù)裙δ埽辉谇度胧较到y(tǒng)中,FPGA可以用于構(gòu)建高性能的處理器、控制器和接口等;在科學(xué)研究中,FPGA可以用于加速計(jì)算、模擬

2023-11-13 15:43:00

我剛買了新的NEXYS4 DDR板,我已經(jīng)安裝并使用了Vivado套件。我的問題是我可以用FPGA做些什么?我是一名計(jì)算機(jī)/電氣學(xué)生,我之所以采用這種邏輯與實(shí)驗(yàn)課是因?yàn)槲乙呀?jīng)參加了我學(xué)校提供的常規(guī)

2020-05-05 07:28:08

可以用FPGA做硬件防火墻嗎?以及如何做呢?

2015-09-21 11:40:46

MODULE USB-TO-FPGA TRAINING TOOL

2023-04-06 11:27:13

MODULE USB-TO-FPGA SPARTAN3

2023-04-06 11:27:13

MODULE USB-TO-FPGA SPARTAN 3A

2023-04-06 11:27:11

使用XINTF總線進(jìn)行通訊進(jìn)行數(shù)據(jù)傳輸,DSP,FPGAIO全部引出 這樣就可以很容易的將主控板融入到嵌入式系統(tǒng)中,需要什么外設(shè)可以直接裝在主控板上,可以用來(lái)控制電機(jī),可以用來(lái)做數(shù)據(jù)采集系統(tǒng)。將外部

2016-07-18 16:59:22

可以用來(lái)控制電機(jī),可以用來(lái)做數(shù)采系統(tǒng)。最小系統(tǒng)圖,將外部接口全部印出來(lái),自己可以隨便做計(jì),電機(jī)控制,數(shù)據(jù)采集,串口,can,485,AD,應(yīng)有盡有設(shè)。DSP28335+FPGA外掛AD760616位

2016-07-16 14:32:23

USB 芯片和軟件廠商飛特蒂亞(FTDI)公司發(fā)布一款靈活而強(qiáng)大的開發(fā)平臺(tái) Morph-IC-II,可加速基于FPGA的應(yīng)用與制作,并簡(jiǎn)化先進(jìn)邏輯電路設(shè)計(jì)中整合高速480Mbit/s USB通訊作業(yè)

2019-07-03 08:29:05

請(qǐng)問NI DAQ系列可以用來(lái)控制步進(jìn)電機(jī)嗎? 要求脈沖間隔0.1ms以下。如果不能的話,想用Labview編程只能靠FPGA卡嗎?淘寶賣的維宏控制卡之類可以嗎?

2018-04-12 15:00:09

BOARD EVAL FOR ORCA OR4E6 FPGA

2023-03-30 11:49:36

FPGA是一種可編程器件,用硬件描述語(yǔ)言進(jìn)行編程使之擁有你所需要的功能,基本上就是EDA了吧。我這個(gè)打個(gè)比方,比如一個(gè)FPGA是一張白紙,通過EDA,在白紙上寫一個(gè)字,那么這個(gè)FPGA就只有顯示

2018-08-15 11:35:09

TINYFPGA AX1

2024-03-14 22:18:36

TINYFPGA AX2

2024-03-14 22:18:36

TINYFPGA BX

2024-03-14 22:18:36

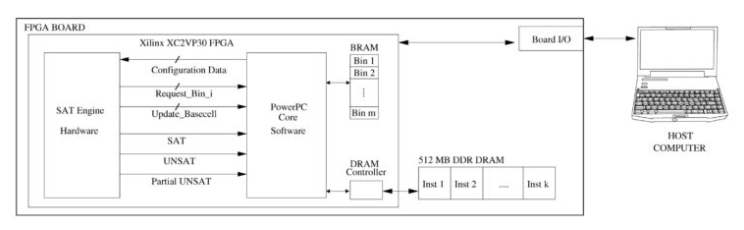

一個(gè)設(shè)計(jì)缺陷,你可以立即對(duì)其進(jìn)行重新編程設(shè)計(jì)。FPGA還允許你實(shí)現(xiàn)硬件運(yùn)算功能,而這在以前的實(shí)現(xiàn)成本是很高的。CPU流水線與FPGA邏輯之間緊密結(jié)合,這樣就可以創(chuàng)建高性能軟件加速器。圖1的模塊框圖顯示

2015-02-02 14:18:19

為什么FPGA可以用來(lái)實(shí)現(xiàn)組合邏輯電路和時(shí)序邏輯電路呢?

2023-04-23 11:53:26

代碼加速和代碼轉(zhuǎn)換到硬件協(xié)處理器的方法如何采用FPGA協(xié)處理器實(shí)現(xiàn)算法加速?

2021-04-13 06:39:25

腳本進(jìn)行FPGA的引腳分配。前面對(duì)ext_clk的引腳分配,我們可以用如下語(yǔ)句實(shí)現(xiàn)。set_location_assignment PIN_E15 -to ext_clk語(yǔ)法

2016-09-17 17:50:15

基于EDA技術(shù)的FPGA設(shè)計(jì)計(jì)算機(jī)應(yīng)用,不看肯定后悔

2021-05-06 06:24:27

對(duì)傳統(tǒng)電子系統(tǒng)設(shè)計(jì)方法與現(xiàn)代電子系統(tǒng)設(shè)計(jì)方法進(jìn)行了比較,引出了基于EDA技術(shù)的現(xiàn)場(chǎng)可編程門陣列(FPGA)電路,提出現(xiàn)場(chǎng)可編程門陣列(FPGA) 是近年來(lái)迅速發(fā)展的大規(guī)模可編程專用集成電路(ASIC

2019-11-01 07:24:42

(Electronic Design Automation)具有一定的代表性。EDA技術(shù)是一種基于芯片的現(xiàn)代電子系統(tǒng)設(shè)計(jì)方法。它的優(yōu)勢(shì)主要集中在能用HDL語(yǔ)言進(jìn)行輸入、進(jìn)行PEn(可編程器件)的設(shè)計(jì)與仿真等系統(tǒng)

2019-10-08 08:02:17

對(duì)傳統(tǒng)電子系統(tǒng)設(shè)計(jì)方法與現(xiàn)代電子系統(tǒng)設(shè)計(jì)方法進(jìn)行了比較,引出了基于EDA技術(shù)的現(xiàn)場(chǎng)可編程門陣列(FPGA)電路,提出現(xiàn)場(chǎng)可編程門陣列(FPGA)是近年來(lái)迅速發(fā)展的大規(guī)模可編程專用集成電路(ASIC

2019-09-03 06:17:15

FPGA加速卡是如何產(chǎn)生的?主要的FPGA加速卡產(chǎn)品有哪些?基于加速卡的FPGA生態(tài)系統(tǒng)布局是怎樣的?

2021-06-17 06:07:15

加速度計(jì)是一種應(yīng)用十分廣泛的慣性傳感器,它可以用來(lái)測(cè)量運(yùn)動(dòng)系統(tǒng)的加速度。目前的加速度計(jì)大多采用微機(jī)電技術(shù)(MEMS)進(jìn)行設(shè)計(jì)和制造的微型加速度計(jì),由于采用了微機(jī)電技術(shù),其設(shè)計(jì)尺寸大大縮小,一個(gè)

2020-11-25 06:17:24

多種EDA工具的FPGA設(shè)計(jì)方案

2012-08-17 10:36:17

1. 避免“劉姥姥進(jìn)大觀園”。就需要學(xué)習(xí)了解其基礎(chǔ)理論,引進(jìn)其基礎(chǔ)理論。要與世界的前沿EDA理論動(dòng)態(tài)接軌。不要過分熱衷于工具中的說明書,FPGA芯片的手冊(cè)等產(chǎn)品資料,要在西方的學(xué)術(shù)文獻(xiàn)中得到前沿信息

2018-03-02 11:32:01

你好,我目前正在設(shè)計(jì)一個(gè)LVDS接收器和DAC ASIC。DAC是12位。我需要使用來(lái)自FPGA / Eval板的LVDS信號(hào)進(jìn)行測(cè)試。任何人都可以推薦我可以用來(lái)測(cè)試我的ASIC的評(píng)估板或FPGA嗎?謝謝。問候,尼基爾

2019-09-19 12:27:09

由于接口不夠,SDIO接口可以用于CPU和FPGA之間進(jìn)行通信嗎

2024-04-23 10:56:14

盤古PGX-Mini 4K開發(fā)板,目前來(lái)說是一款性價(jià)比比較高的開發(fā)板,他用來(lái)入門FPGA怎么樣?

2024-03-16 07:17:45

FPGA可以用純C語(yǔ)言開發(fā)嗎?

2023-10-31 08:26:46

你好,我目前正在設(shè)計(jì)一個(gè)LVDS接收器和DAC ASIC。DAC是12位。我需要使用來(lái)自FPGA / Eval板的LVDS信號(hào)進(jìn)行測(cè)試。任何人都可以推薦Xilinx的評(píng)估板或FPGA,我可以使用它來(lái)測(cè)試我的ASIC嗎?謝謝。問候,尼基爾

2019-08-28 07:03:41

全球領(lǐng)先的中文互聯(lián)網(wǎng)搜索引擎提供商百度正在采用賽靈思FPGA加速其中國(guó)數(shù)據(jù)中心的機(jī)器學(xué)習(xí)應(yīng)用。兩家公司正合作進(jìn)一步擴(kuò)大FPGA加速平臺(tái)的部署規(guī)模。新興應(yīng)用的快速發(fā)展正日漸加重計(jì)算工作的負(fù)載,數(shù)據(jù)中心

2016-12-15 17:15:52

多功能食品安全快速篩檢系統(tǒng)可以用來(lái)檢測(cè)什么【山東霍爾德電子科技 HED-G1800】食品檢測(cè)儀器為集成化食品安全快速檢測(cè)分析設(shè)備,可現(xiàn)場(chǎng)快速檢測(cè)非食用化學(xué)物質(zhì)、濫用食品添加劑、農(nóng)藥殘留、獸藥殘留

2021-03-22 09:59:10

北京革新創(chuàng)展科技有限公司研制的B-ICE-EDA/SOPC FPGA平臺(tái)集多功能于一體,充分滿足EDA、SOPC、ARM、DSP、單片機(jī)相互結(jié)合的實(shí)驗(yàn)教學(xué),是電子系統(tǒng)設(shè)計(jì)創(chuàng)新實(shí)驗(yàn)室、嵌入式系統(tǒng)實(shí)驗(yàn)室

2022-03-09 11:18:52

上EasyGo FPGA Solver中的FPGA Coder解算軟件,可以將用戶靈活搭建的模型直接下載至FPGA中運(yùn)行,而不需要進(jìn)行FPGA的編譯,最

2022-05-19 09:16:05

。EasyGo FPGA Solver 的優(yōu)點(diǎn)在于,能夠?qū)imulink的圖形化模型利用解算器軟件轉(zhuǎn)化成FPGA執(zhí)行的代碼,而不需要進(jìn)行FPGA的編譯

2022-05-19 09:21:43

EDA Tools in FPGA用于開發(fā)FPGA的EDA工具:隨著集成電路和計(jì)算機(jī)技術(shù)的發(fā)展,越來(lái)越多的公司不斷的開發(fā)出更加好用的EDA工具給廣大的技瑯人員。現(xiàn)在無(wú)論是軟件的開發(fā)

2009-12-05 16:10:24 0

0 FPGA設(shè)計(jì)的指導(dǎo)原則:這里“面積”指一個(gè)設(shè)計(jì)消耗FPGA/CPLD 的邏輯資源的數(shù)量,對(duì)于FPGA 可以用所消耗的觸發(fā)器(FF)和查找表(LUT)來(lái)衡量,更一般的衡量方式可以用設(shè)計(jì)所占用的等

2010-01-11 09:01:35 107

107 EDA(CPLD/FPGA)技術(shù)概述

主要術(shù)語(yǔ)摘要:* EDA(電子設(shè)計(jì)自動(dòng)化):Electronic Design Automation* ISP(在系統(tǒng)可編程):In System Programmabl

2008-09-24 10:10:34 3256

3256 基于多種EDA工具的FPGA設(shè)計(jì)

介紹了利用多種EDA工具進(jìn)行FPGA設(shè)計(jì)的實(shí)現(xiàn)原理及方法,其中包括設(shè)計(jì)輸入、綜合、功能仿真、實(shí)現(xiàn)、時(shí)序仿真、配置下載等具體內(nèi)容。并以實(shí)

2009-05-14 18:38:38 1036

1036

摘 要:在FPGA開發(fā)的各個(gè)階段,市場(chǎng)為我們提供了很多優(yōu)秀的EDA工具。面對(duì)眼花繚亂的EDA工具,如何充分利用各種工具的特點(diǎn),并規(guī)劃好各種工具的協(xié)同使用,對(duì)FPGA

2009-06-20 10:51:14 906

906 摘要:介紹了利用多種EDA工具進(jìn)行FPGA設(shè)計(jì)的實(shí)現(xiàn)原理及方法,其中包括設(shè)計(jì)輸入、綜合、功能仿真、實(shí)現(xiàn)、時(shí)序仿真、配置下載等具體內(nèi)容。并以實(shí)際操作介紹了

2009-06-20 11:42:45 674

674

基于EDA仿真技術(shù)解決FPGA設(shè)計(jì)開發(fā)中故障的方法 FPGA近年來(lái)在越來(lái)越多的領(lǐng)域中應(yīng)用,很多大通信系統(tǒng)(如通信基站等)都用其做核心數(shù)據(jù)的處理。

2010-03-24 18:07:49 2036

2036

多種EDA工具的FPGA設(shè)計(jì)方案

概述:介紹了利用多種EDA工具進(jìn)行FPGA設(shè)計(jì)的實(shí)現(xiàn)原理及方法,其中包括設(shè)計(jì)輸入、綜合、功能仿真、實(shí)現(xiàn)、時(shí)序仿真、配

2010-05-25 17:56:59 895

895

摘 要:EDA技術(shù)是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,它在現(xiàn)代集成電路設(shè)計(jì)中占據(jù)重要地位。隨著深亞微米與超深亞微米技術(shù)的迅速發(fā)展,FPGA設(shè)計(jì)越來(lái)越多地采用基于VHDL的設(shè)計(jì)方法及先進(jìn)的E

2011-05-27 10:50:58 3314

3314 對(duì)傳統(tǒng)電子系統(tǒng)設(shè)計(jì)方法與現(xiàn)代電子系統(tǒng)設(shè)計(jì)方法進(jìn)行了比較,引出了基于EDA技術(shù)的現(xiàn)場(chǎng)可編程門陣列(FPGA)電路,提出現(xiàn)場(chǎng)可編程門陣列(FPGA) 是近年來(lái)迅速發(fā)展的大規(guī)模可編程專用集成電

2011-09-19 17:18:19 1012

1012 基于FPGA的EDA綜合實(shí)驗(yàn)系統(tǒng)設(shè)計(jì)_趙剛

2017-03-19 11:38:26 2

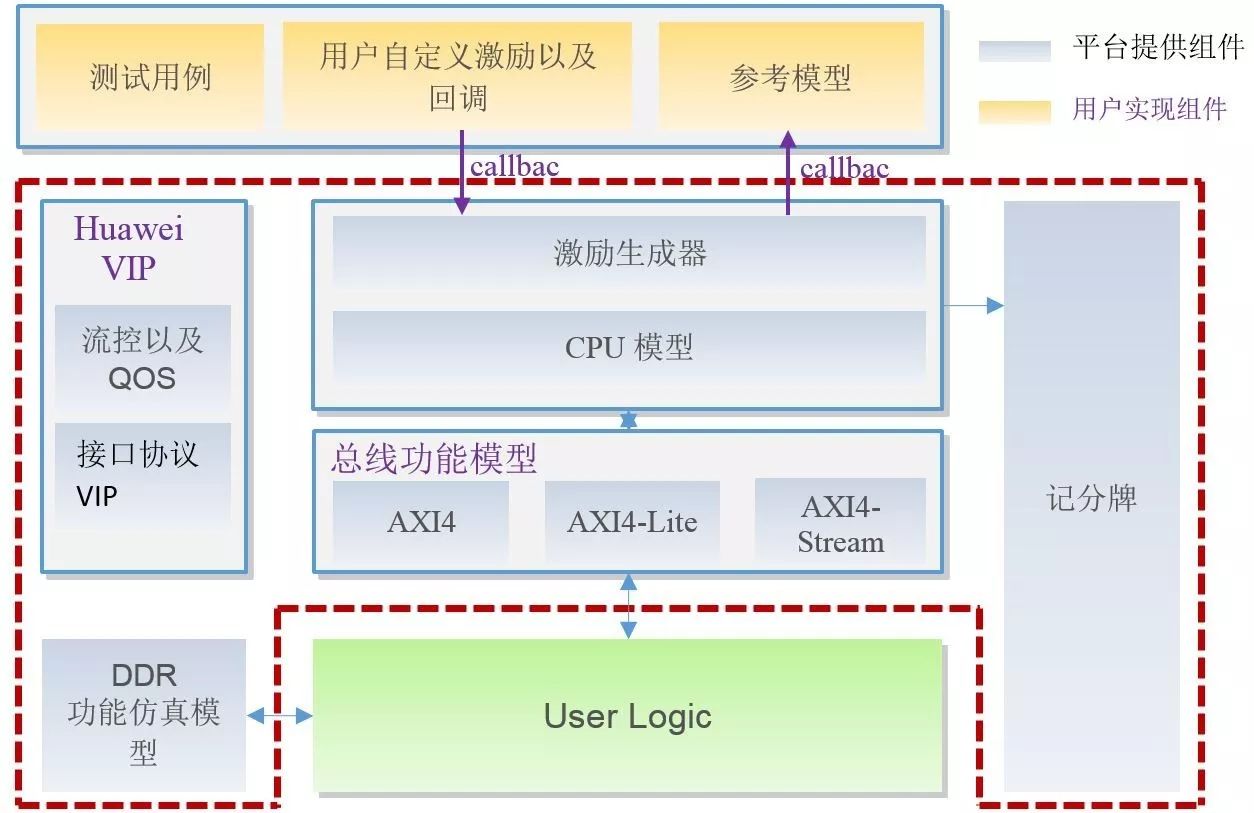

2 在數(shù)據(jù)中心引入 FPGA 并實(shí)現(xiàn)云化加速業(yè)務(wù)成為必然趨勢(shì)。隨著華為云 FPGA 加速服務(wù)的推出,打破原有 FPGA 開發(fā)、測(cè)試和應(yīng)用存在的較高門檻,開啟了一個(gè)顛覆 FPGA 開發(fā)的新時(shí)代!

2017-10-10 10:49:17 5432

5432

基于FPGA的通用CNN加速器整體框架如下,通過Caffe/Tensorflow/Mxnet等框架訓(xùn)練出來(lái)的CNN模型,通過編譯器的一系列優(yōu)化生成模型對(duì)應(yīng)的指令;同時(shí),圖片數(shù)據(jù)和模型權(quán)重?cái)?shù)據(jù)按照優(yōu)化規(guī)則進(jìn)行預(yù)處理以及壓縮后通過PCIe下發(fā)到FPGA加速器中

2017-10-27 14:09:58 10619

10619

可以用來(lái)為測(cè)試測(cè)量系統(tǒng)創(chuàng)建PWM接口。與專用的PWM I/O設(shè)備不同的是,LabVIEW FPGA允許自定義應(yīng)用程序的PWM通道特性和行為,并且可以與其它的測(cè)量設(shè)備集成和同步。 1. 應(yīng)用程序概述 LabVIEW FPGA模塊和可重配置的I/O板卡可以用來(lái)實(shí)現(xiàn)各種自定義接口。

2017-11-18 07:18:21 12809

12809

---最后針對(duì)fpga的設(shè)計(jì)實(shí)現(xiàn)提出一些改進(jìn)方案,fpga實(shí)現(xiàn)分為編譯規(guī)劃、布局布線(par,place and route)、程序比特流文件生成三個(gè)階段,當(dāng)設(shè)計(jì)不滿足性能指標(biāo)或不能完全布線時(shí),可進(jìn)行以下改進(jìn)工作:

2018-07-19 13:18:00 2778

2778 對(duì)于初學(xué)者而言,FPGA的設(shè)計(jì)流程是否顯的“又臭又長(zhǎng)”呢??嗬嗬,如果真的有這樣的感覺,沒有關(guān)系,下面我就通過對(duì)軟體的使用來(lái)了解FPGA的設(shè)計(jì)流程。

2018-06-02 07:17:00 1553

1553

FPGA技術(shù)概念

CPLD (Complex Programmable Logic Device)FPGA (Field Programmable Gate Array)

EDA技術(shù) 密度邏輯

2019-03-29 16:53:55 7

7 近日,百度云與聯(lián)捷計(jì)算科技(CTAccel)共同推出基于FPGA的圖像加速解決方案(CIP,CTAccel Image Processor),實(shí)現(xiàn)對(duì)JPEG轉(zhuǎn)碼JPEG、JPEG轉(zhuǎn)碼WebP(M6)等進(jìn)行FPGA加速的功能,聚焦社交平臺(tái)、新聞網(wǎng)站、電商、云相冊(cè)等場(chǎng)景。

2019-06-18 14:35:55 1912

1912 FPGA可以用來(lái)做高速信號(hào)處理,一般如果AD采樣率高,數(shù)據(jù)速率高,這時(shí)就需要FPGA對(duì)數(shù)據(jù)進(jìn)行處理,比如對(duì)數(shù)據(jù)進(jìn)行抽取濾波,降低數(shù)據(jù)速率,使信號(hào)容易處理,傳輸,存儲(chǔ)。

2019-07-10 17:48:58 7882

7882 近日,基于現(xiàn)場(chǎng)可編程門陣列(FPGA)的數(shù)據(jù)加速器件和高性能嵌入式FPGA(eFPGA)半導(dǎo)體知識(shí)產(chǎn)權(quán)(IP)領(lǐng)導(dǎo)性企業(yè)Achronix半導(dǎo)體公司,與Molex旗下的一家領(lǐng)先企業(yè)級(jí)FPGA加速器產(chǎn)品供應(yīng)商BittWare今日聯(lián)合宣布:推出一類全新的、面向高性能計(jì)算和數(shù)據(jù)加速應(yīng)用的FPGA加速卡。

2019-10-31 15:11:33 1229

1229 FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過程。FPGA的開發(fā)流程一般包括功能定義/器件選型、設(shè)計(jì)輸入、功能仿真、邏輯綜合、布局布線與實(shí)現(xiàn)、編程調(diào)試等主要步驟。

2019-11-06 15:17:28 2841

2841 FPGA的優(yōu)勢(shì)有三個(gè)方面:1)通信高速接口設(shè)計(jì)。FPGA可以用來(lái)做高速信號(hào)處理,一般如果AD采樣率高,數(shù)據(jù)速率高,這時(shí)就需要FPGA對(duì)數(shù)據(jù)進(jìn)行處理。

2020-01-10 15:46:21 1460

1460 最新才流行的嵌入式C程序。 FPGA的開發(fā)流程即是利用EDA開發(fā)軟件以及編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過程。EDA ( Electronic Design Automation,電子設(shè)計(jì)自動(dòng)化

2020-11-12 18:22:28 7390

7390 我們知道,FPGA的頻率一般只有幾百M(fèi)Hz,而CPU的頻率卻高達(dá)數(shù)GHz。那么,有不少網(wǎng)友心中就有一個(gè)疑問:為什么FPGA主頻比CPU慢,但卻可以用來(lái)幫CPU做加速?。 今天,EDN就和大家

2020-11-20 09:56:16 4651

4651 FPGA_ASIC-DSP和FPGA共用FLASH進(jìn)行配置的方法(哪些專業(yè)適合嵌入式開發(fā))-該文檔為FPGA_ASIC-DSP和FPGA共用FLASH進(jìn)行配置的方法講解文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-07-30 11:16:55 22

22 可以通過編程來(lái)改變內(nèi)部結(jié)構(gòu)的芯片。FPGA 功能實(shí)現(xiàn):需要通過編程即設(shè)計(jì)硬件描述語(yǔ)言,經(jīng)過 EDA 工具

2021-11-30 17:21:05 45

45 對(duì)FPGA進(jìn)行上板調(diào)試時(shí),使用最多的是SignalTap,但SignalTap主要用來(lái)抓取信號(hào)時(shí)序,當(dāng)需要發(fā)送信號(hào)到FPGA時(shí),Jtag Master可以發(fā)揮很好的作用,可以通過Jtag Master對(duì)FPGA進(jìn)行讀寫測(cè)試

2022-02-16 16:21:36 3152

3152

我們知道,FPGA的頻率一般只有幾百M(fèi)Hz,而CPU的頻率卻高達(dá)數(shù)GHz。那么,有不少網(wǎng)友心中就有一個(gè)疑問:“為什么FPGA主頻比CPU慢,但卻可以用來(lái)幫CPU做加速?”。

2022-03-25 09:45:15 1783

1783 電子發(fā)燒友網(wǎng)站提供《基于FPGA的加速基礎(chǔ)知識(shí).pdf》資料免費(fèi)下載

2023-09-18 10:12:20 0

0 加速FPGA選擇和系統(tǒng)設(shè)計(jì)的架構(gòu)探索

2022-12-30 09:21:10 4

4 FPGA(現(xiàn)場(chǎng)可編程門陣列)是一種高度靈活的硬件設(shè)備,可以根據(jù)特定的需求進(jìn)行重新配置。FPGA通常用于處理大量數(shù)據(jù)和實(shí)時(shí)計(jì)算。然而,FPGA通常并沒有內(nèi)置大容量的數(shù)據(jù)存儲(chǔ)器,例如硬盤或固態(tài)硬盤。這就

2023-12-15 15:42:51 4664

4664 任務(wù)是將邏輯元件與連接線路進(jìn)行合理的布局和布線,以實(shí)現(xiàn)性能優(yōu)化和電路連接的可靠性。然而,FPGA布局布線的過程通常是一項(xiàng)繁瑣且耗時(shí)的任務(wù),因此加速布局布線算法的研究具有重要意義。本文將詳盡探討FPGA布局布線算法加速的方法與技術(shù),分析其理論基礎(chǔ)和實(shí)踐應(yīng)用。 FPGA布局布

2023-12-20 09:55:13 1768

1768 :DE5Net_Conv_Accelerator 應(yīng)用場(chǎng)景 :面向深度學(xué)習(xí)的開源項(xiàng)目,實(shí)現(xiàn)了AlexNet的第一層卷積運(yùn)算加速。 技術(shù)特點(diǎn) : 采用了Verilog語(yǔ)言進(jìn)行編程,與PCIe接口相集成,可以直接插入到

2024-10-25 09:22:03 1856

1856 智多晶EDA工具HqFpga軟件實(shí)用小功能增加啦,支持生成可調(diào)用網(wǎng)表的功能和ballmap功能。下面來(lái)給大家講解一下如何通過HqFpga軟件生成可調(diào)用的網(wǎng)表文件以及ballmap功能的使用。

2024-12-05 10:23:33 1980

1980

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論