摘 要:本文介紹了一種同步測周期計數(shù)器的設(shè)計,并基于該計數(shù)器設(shè)計了一個高精度的數(shù)字頻率計。文中給出了計數(shù)器的VHDL編碼,并對頻率計的FPGA實現(xiàn)進行了仿真驗證,給出了測試結(jié)果。

在現(xiàn)代數(shù)字電路設(shè)計中,采用FPGA結(jié)合硬件描述語言VHDL可以設(shè)計出各種復(fù)雜的時序和邏輯電路,具有設(shè)計靈活、可編程、高性能等優(yōu)點。本文將介紹一種基于FPGA,采用同步測周期的方法來實現(xiàn)寬頻段高精度數(shù)字頻率計的設(shè)計。

圖1 同步測周期計數(shù)器

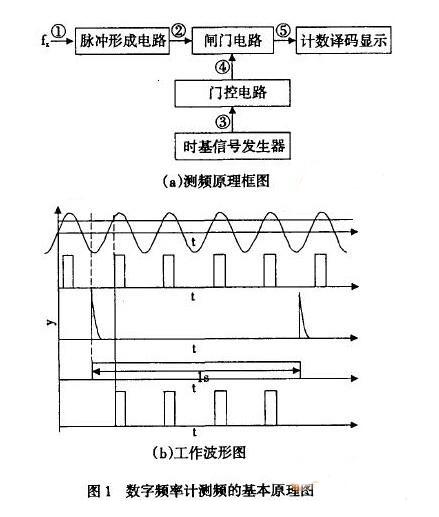

同步測周期頻率計的原理

在數(shù)字頻率計中,測周期計數(shù)器是主要的電路,其功能是:使用標準時鐘以被測頻率信號的一個周期為時限進行脈沖計數(shù)。傳統(tǒng)的測周期計數(shù)器采用門控計數(shù)器來實現(xiàn),即采用一個同被測頻率信號周期寬度相同的門控脈沖來控制計數(shù)器的計停。其缺點在于無法實現(xiàn)對被測信號的連續(xù)測周期計數(shù)。

本文設(shè)計的同步測周期計數(shù)器如圖1所示。圖中計數(shù)器的計數(shù)時鐘為clk0, 頻率為f0;被測信號為clkx,頻率為fx。采用一個D觸發(fā)器對輸入的被測信號clkx進行同步,同步輸出為s0。在clk0的上升沿到來之前,如果clkx出現(xiàn)了上升跳變,則le信號變?yōu)楦唠娖剑嫈?shù)器ct的重載信號和鎖存器cout的使能信號有效。當clk0的上升沿到來時,計數(shù)器的計數(shù)值鎖存,同時計數(shù)器重載為1,重新開始計數(shù),le變?yōu)榈碗娖健S嫈?shù)器在其他時間里進行加1計數(shù),鎖存器的值則保持不變。該測周期計數(shù)器能在clkx的每個上升沿之后輸出計數(shù)值,實現(xiàn)了對被測信號進行測周期計數(shù),并始終輸出其最新一個周期的計數(shù)值,圖中cint端輸出一個clk0周期寬度的高脈沖,用于指示新的計數(shù)值鎖存。

圖2 同步測周期數(shù)字頻率計

圖3 頻率計cint的改進電路

設(shè)該計數(shù)器的測周期計數(shù)值為M0,由于同步測周期法的分辨率為一個標準時鐘周期,因此有:

該同步測周期計數(shù)器的測周期計數(shù)值最小為2,要求被測信號高低電平的寬度大于一個標準時鐘周期。

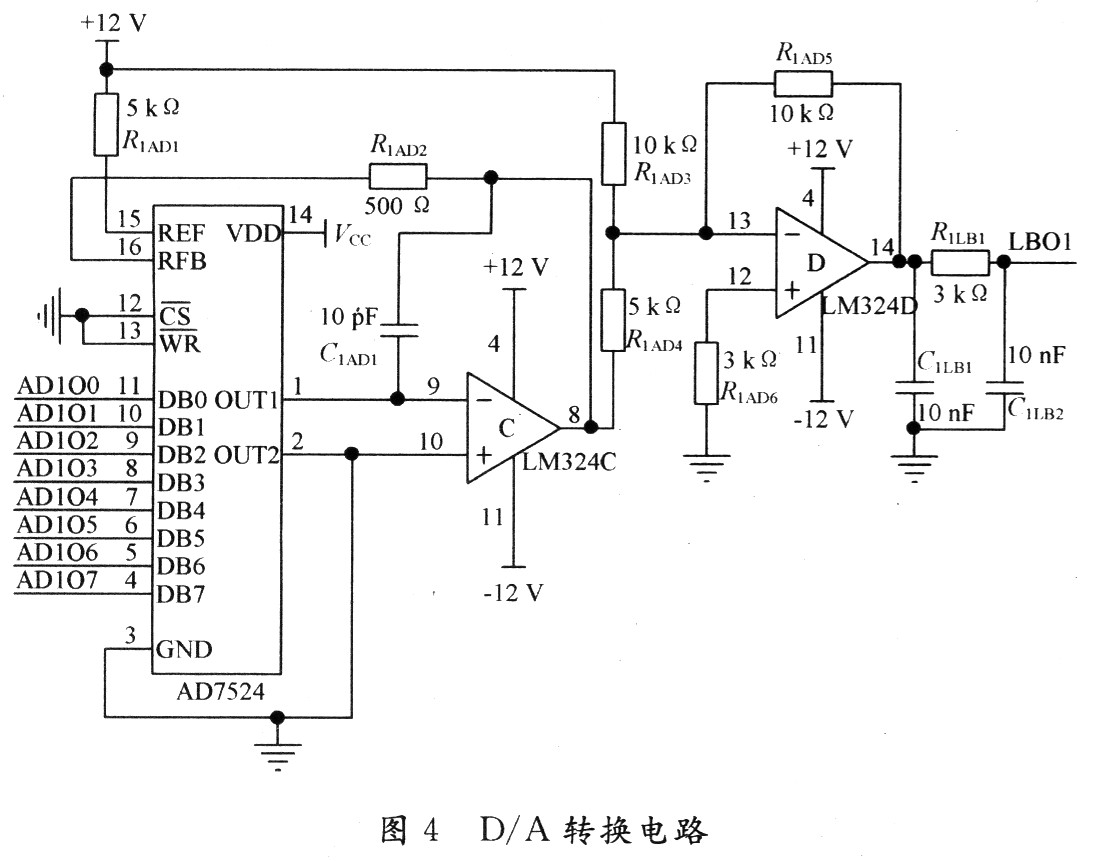

基于上述同步測周期計數(shù)器,本文設(shè)計了如圖2所示的高精度數(shù)字頻率計。freq_div模塊是一個分頻器,對標準時鐘clk0進行系數(shù)為C0的分頻。頻率計采用了兩個同步測周期計數(shù)器同時工作,計數(shù)值輸出端口分別為cout和mout。為了避免由于同步測周期計數(shù)器中被測信號和標準時鐘不同步,le信號高電平的寬度不固定而造成的計數(shù)出錯,在實際應(yīng)用中,采取將被測信號先經(jīng)過一個D觸發(fā)器同步后再送入計數(shù)器的方法,以保證計數(shù)的可靠性,其計數(shù)值和頻率的關(guān)系仍滿足(1)式。設(shè)cout輸出的值為C,mout輸出的值為M,根據(jù)頻率計的結(jié)構(gòu),對于其中以clkx為計數(shù)時鐘的計數(shù)器,由(1)式得:

同理,對于以clk0為計數(shù)時鐘的計數(shù)器,有:

根據(jù)兩個測周期計數(shù)器的計數(shù)值M、C,被測信號的頻率按下式計算得到

根據(jù)(3)式,計算結(jié)果的最大誤差為:

相對誤差為:

因此,只要使計數(shù)值C足夠大就可以保證頻率測量的精度。將(3)和(4)兩式相除并忽略小項得C和C0的關(guān)系如下:

給定C0,測周期計數(shù)值C的最大可變范圍為:。因此,根據(jù)實際測量精度的要求,設(shè)定適當?shù)姆诸l器分頻系數(shù)C0,即可保證實際的測周期計數(shù)值C的大小在精度要求的范圍內(nèi)。對于上述的數(shù)字頻率計,如果增大分頻器分頻系數(shù)C0,提高測周期計數(shù)器的計數(shù)范圍,可實現(xiàn)對輸入信號寬頻段高精度的頻率測量。

圖4 輸入被測信號周期為156ms時的仿真波形

數(shù)字頻率計的VHDL實現(xiàn)

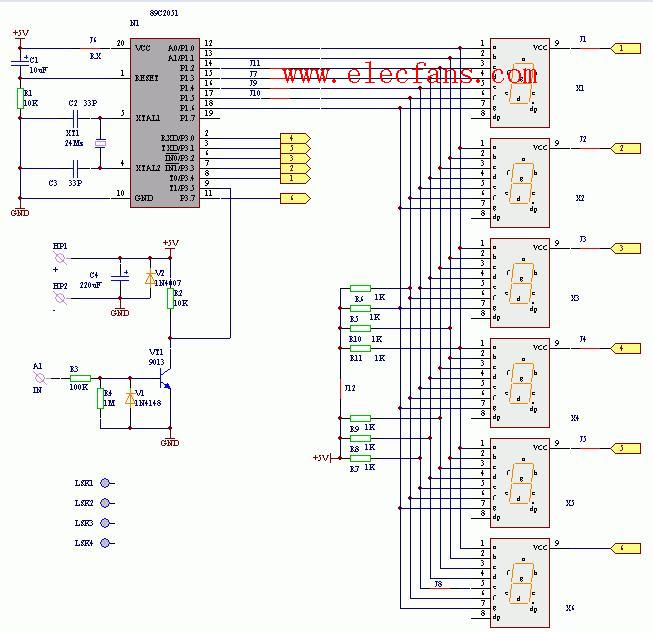

上述的同步測周期數(shù)字頻率計在Altera 公司的FPGA開發(fā)平臺Quartus II中實現(xiàn),模塊采用VHDL語言描述,具有通用性和可重用性。圖1中的同步測周期計數(shù)器的VHDL描述如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity freq_count is --實體定義

port( reset: in std_logic;

clk0 : in std_logic;

clkx : in std_logic;

cint : out std_logic;

cout : out std_logic_vector(23 downto 0));

end entity freq_count;

architecture ar of freq_count is

signal s0 : std_logic;

signal ct : std_logic_vector(23 downto 0);

begin

p0: process(reset,clk0)

--計數(shù)器進程

begin

if reset='0' then

s0<='0';

cint<='1';

cout<=conv_std_logic_vector(0,24);

else

if clk0'event and clk0='1' then

s0<=clkx;

if s0='0' and clkx='1' then

cout<=ct;

cint<='0';

ct<=conv_std_logic_vector(1,24);

else

cint<='1';

ct<=ct+1;

end if;

end if;

end if;

end process p0;

end ar;

測周期計數(shù)值M、C分別由mout和cout端口輸出,通過一定的接口由微處理器或其他的數(shù)據(jù)處理模塊獲取,進行頻率的計算和顯示,根據(jù)實際的應(yīng)用情況設(shè)計輸出接口,這里不再詳述。當頻率計新一輪的測周期計數(shù)完成后,計數(shù)器通過cint和mint信號指示處理單元來獲取數(shù)據(jù),其高電平脈沖的寬度為一個計數(shù)時鐘周期。當計數(shù)時鐘頻率很高時,一些慢速的單片機可能無法捕獲,因此(以cint信號為例)增加如圖3所示的電路。cint上升沿使D觸發(fā)器輸出引腳cdone置0,通知單片機取數(shù),單片機讀結(jié)果時,相應(yīng)的地址信號和讀信號有效使圖中的cint_set有效,cdone被復(fù)位為1,等待下一次cint脈沖的出現(xiàn)。通過該電路,慢速單片機就可以捕獲頻率計計數(shù)完成的指示信號。

為了使頻率計的設(shè)計更加靈活,頻率計中分頻器的分頻系數(shù)也可改為由外部輸入。在頻率計運行期間,由外部控制器設(shè)置不同的分頻系數(shù)C0,這樣可實現(xiàn)更寬范圍的頻率測量。

頻率計的仿真驗證 結(jié)語

上述數(shù)字頻率計的VHDL設(shè)計在Altera公司的Quartus II開發(fā)平臺下進行了編譯和仿真,圖4是在clk0輸入10 MHz方波,clkx輸入周期為156ms(頻率為6.41KHz)方波,分頻系數(shù)C0取15000時的仿真波形。

本文采用Altera公司的FPGA FLEX10K10LC84-4來實現(xiàn)上述的頻率計,計數(shù)器計數(shù)值的處理和顯示由 51單片機來完成,同步測周期數(shù)字頻率計的參數(shù)和測試結(jié)果是:計數(shù)器寬度為24 bit;分頻系數(shù)C0取106;計數(shù)時鐘頻率f0為1MHz;FPGA邏輯單元的使用比例為41%;測量的頻率范圍是1Hz

本文設(shè)計的同步測周期計數(shù)器能夠直接對被測信號進行連續(xù)的測周期計數(shù),可以在許多頻率測量的設(shè)計中取代門控計數(shù)器,使設(shè)計更加靈活。文中采用兩個同步測周期計數(shù)器設(shè)計的數(shù)字頻率計,無需選擇量程便可實現(xiàn)寬頻段高精度的頻率測量,并在FPGA中實現(xiàn)了系統(tǒng)集成。

4位數(shù)字頻率計原理圖 仿真圖 ms.10文件或protel文件

4位數(shù)字頻率計原理圖,.ms10文件或protel文件

4位數(shù)字頻率計的設(shè)計

數(shù)字頻率計的設(shè)計

數(shù)字頻率計設(shè)計與仿真

[求助]數(shù)字頻率計的設(shè)計

[求助]數(shù)字頻率計設(shè)計

【AC620 FPGA試用體驗】數(shù)字頻率計

【AC620 FPGA試用申請】基于fpga的數(shù)字頻率計

基于8086的數(shù)字頻率計怎么實現(xiàn)?

基于FPGA的數(shù)字頻率計

怎樣去設(shè)計一個基于單片機C語言的數(shù)字頻率計

怎樣去設(shè)計基于單片機的數(shù)字頻率計

我用Protel繪制的數(shù)字頻率計

經(jīng)典數(shù)字頻率計課程設(shè)計畢業(yè)論文資料

請問怎樣去設(shè)計一種基于VHDL語言的數(shù)字頻率計

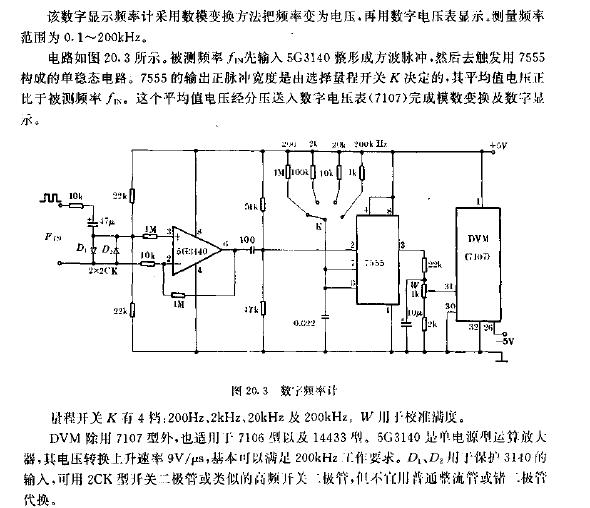

數(shù)字頻率計測頻率的基本原理

525

525基于FPGA的數(shù)字頻率計的設(shè)計與實現(xiàn)

193

193基于FPGA/CPLD芯片的數(shù)字頻率計設(shè)計

132

132基于TMS320F2812的數(shù)字頻率計

41

41超高頻數(shù)字頻率計的設(shè)計

101

101基于FPGA與DSP的等精度數(shù)字頻率計設(shè)計

68

6812位十進制等精度數(shù)字頻率計

98

98基于單片機和CPLD的數(shù)字頻率計的設(shè)計

1402

1402量程自動控制的數(shù)字頻率計

3236

3236

基于高速串行BCD碼除法的數(shù)字頻率計的設(shè)計

1611

1611

一種高性價比等精度數(shù)字頻率計方案設(shè)計

2618

2618

基于單片機的數(shù)字頻率計的方案

6749

6749

八位150MHz數(shù)字頻率計的制作

7895

7895

數(shù)字頻率計

940

940設(shè)計簡易數(shù)字頻率計

1214

1214基于NiosII的等精度數(shù)字頻率計的設(shè)計

66

66基于DSP2812設(shè)計的簡易數(shù)字頻率計

5462

5462

數(shù)字頻率計的制作

172

172基于verilog語言的數(shù)字頻率計設(shè)計

0

0大學數(shù)字頻率計課程設(shè)計報告

69

69數(shù)字頻率計

58

58畢業(yè)論文:一種基于單片機數(shù)字頻率計的設(shè)計與實現(xiàn)

62

62簡易數(shù)字頻率計

234

234如何使用FPGA和DSP進行精度數(shù)字頻率計的設(shè)計

13

13基于FPGA自適應(yīng)數(shù)字頻率計的設(shè)計

7198

7198

如何進行簡易數(shù)字頻率計的設(shè)計分析

7

7使用Multisim制作的簡易數(shù)字頻率計電路圖免費下載

70

70使用FPGA設(shè)計的數(shù)字頻率計的程序和工程文件免費下載

15

15使用FPGA設(shè)計的數(shù)字頻率計Verilog程序免費下載

26

26數(shù)字頻率計VHDL程序與仿真的設(shè)計資料免費下載

28

28基于TMS320F2812的簡易數(shù)字頻率計

10

10基于51單片機的數(shù)字頻率計的設(shè)計講解

87

87數(shù)字頻率計 風力擺 雙向DC-DC變換器

12

12基于單片機的數(shù)字頻率計設(shè)計

32

32微波數(shù)字頻率計的基本工作原理是什么?

1641

1641

電子發(fā)燒友App

電子發(fā)燒友App

評論