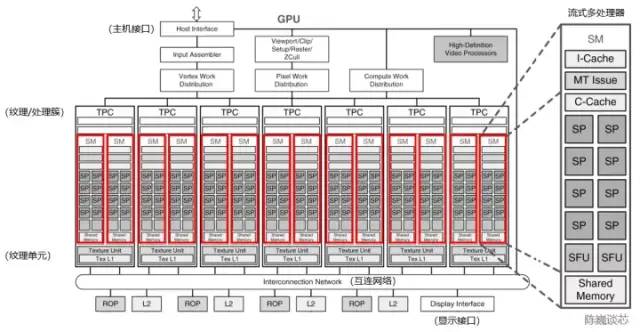

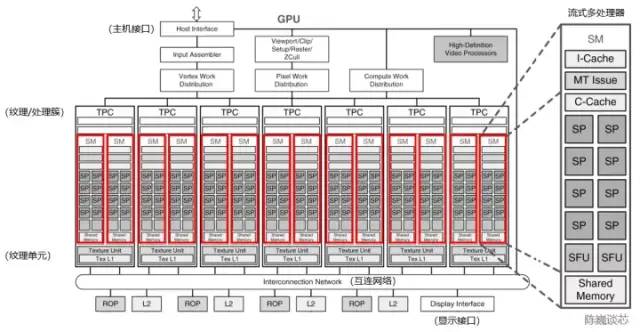

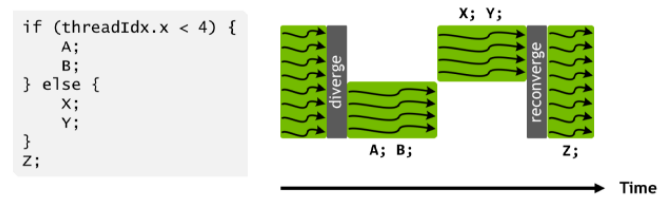

流式多處理器(Stream Multi-processor,SM)是構(gòu)建整個(gè) GPU的核心模塊(執(zhí)行整個(gè) Kernel Grid),一個(gè)流式多處理器上一般同時(shí)運(yùn)行多個(gè)線(xiàn)程塊。每個(gè)流式多處理器可以視為具有較小結(jié)構(gòu)的CPU,支持指令并行(多發(fā)射)。

2023-03-30 10:14:24 1685

1685 專(zhuān)注于引入新品并提供海量庫(kù)存的電子元器件分銷(xiāo)商貿(mào)澤電子 (Mouser Electronics)即日起備貨Xilinx的Zynq? UltraScale+ 多處理器片上系統(tǒng) (MPSoC)。

2019-11-25 15:28:48 1518

1518 芯片。 目前有很多應(yīng)用要求多處理器的配置(多個(gè) ARM 內(nèi)核,或 ARM+DSP 的組合),ARM11 處理器從設(shè)計(jì)伊始就注重更容易地與其他處理器共享數(shù)據(jù),以及從非 ARM 的處理器上移植 軟件。此外,ARM還開(kāi)發(fā)了基于ARM11系列的多處理器系統(tǒng)—MPCORE(由2~4個(gè)ARM11 內(nèi)核組成)

2019-09-27 09:31:20

具有強(qiáng)大的處理能力,有許多算法實(shí)現(xiàn)時(shí)必須采用并行處理。因此,傳統(tǒng)的基于單內(nèi)核微控制器的解決方案面臨很大挑戰(zhàn),融合MCU及DSP的異構(gòu)雙處理器或多處理器解決方案,以及具有強(qiáng)大運(yùn)算能力的多內(nèi)核處理器是智能

2010-03-16 10:52:08

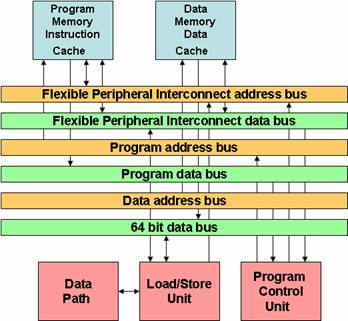

。 ADSP21160具有很大的片內(nèi)存儲(chǔ)區(qū)、多重內(nèi)部總線(xiàn)結(jié)構(gòu)、獨(dú)立的I/O子系統(tǒng);具有構(gòu)造多處理器系統(tǒng)的所有特點(diǎn),能夠真正支持處理器數(shù)目的可調(diào)節(jié)功能,十分適合組成高性能浮點(diǎn)的多DSP系統(tǒng)。 VxWorks

2019-07-10 08:03:26

Cortex-A15 MPCore處理器是一款高性能、低功耗的多處理器,采用ARMv7-A架構(gòu)。

Cortex-A15 MPCore處理器在具有L1和L2緩存子系統(tǒng)的單個(gè)多處理器設(shè)備或MPCore設(shè)備中具有一到四個(gè)Cortex-A15處理器。

2023-08-17 07:37:22

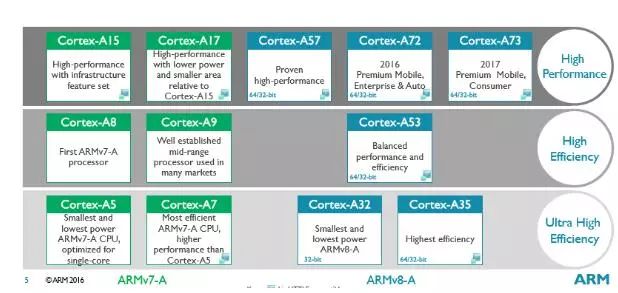

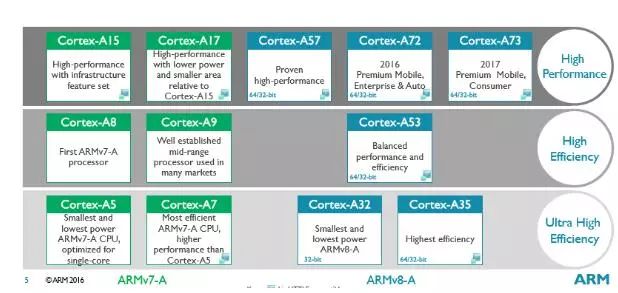

ARM Cortex系列那么多處理器,該怎么區(qū)分?

2020-05-29 13:43:08

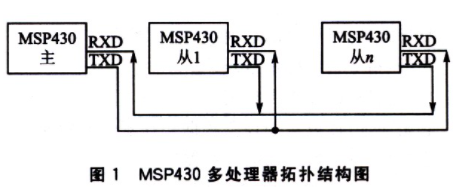

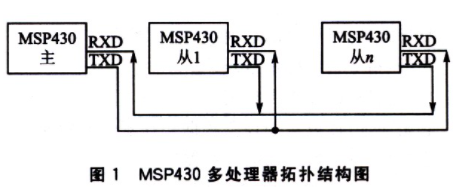

很多處理器通信,即將幾個(gè)USART連接在一個(gè)網(wǎng)絡(luò)里。比如某個(gè)USART設(shè)備可以是主機(jī),它的TX輸出和其他USART從設(shè)備的RX輸入相連接;USART從設(shè)備各自的TX輸入輸出與本地,并與主設(shè)備的RX輸入

2023-04-28 16:24:14

CM3之STM32如何實(shí)現(xiàn)多處理器通信

2015-09-17 10:11:58

普遍認(rèn)為開(kāi)發(fā)多處理器系統(tǒng)軟件的難度要大于單處理器系統(tǒng)。但實(shí)際情況并非總是如此。我們這個(gè)在 TRW 汽車(chē)公司下屬的咨詢(xún)部 TRW Conekt 工作的設(shè)計(jì)團(tuán)隊(duì)最近接管了一個(gè)項(xiàng)目,展示了如何根據(jù)手中的問(wèn)題發(fā)揮硬件的功能,并通過(guò)使用許多個(gè)處理器開(kāi)發(fā)出高效系統(tǒng)。

2019-10-23 08:00:03

我想運(yùn)用生成即保證正確(correct-by-construction)規(guī)則設(shè)計(jì)多處理器混合關(guān)鍵性系統(tǒng),請(qǐng)問(wèn)生成即保證正確(correct-by-construction)規(guī)則可用嗎?在什么情況下可用?

2016-02-17 16:18:34

。 ADSP21160具有很大的片內(nèi)存儲(chǔ)區(qū)、多重內(nèi)部總線(xiàn)結(jié)構(gòu)、獨(dú)立的I/O子系統(tǒng);具有構(gòu)造多處理器系統(tǒng)的所有特點(diǎn),能夠真正支持處理器數(shù)目的可調(diào)節(jié)功能,十分適合組成高性能浮點(diǎn)的多DSP系統(tǒng)

2019-06-27 06:48:18

。 ADSP21160具有很大的片內(nèi)存儲(chǔ)區(qū)、多重內(nèi)部總線(xiàn)結(jié)構(gòu)、獨(dú)立的I/O子系統(tǒng);具有構(gòu)造多處理器系統(tǒng)的所有特點(diǎn),能夠真正支持處理器數(shù)目的可調(diào)節(jié)功能,十分適合組成高性能浮點(diǎn)的多DSP系統(tǒng)

2019-04-03 09:40:03

dlpc3439只有紅綠藍(lán)三色的顯示接口,很多處理器沒(méi)這個(gè)接口了。怎么辦?

只能選有這個(gè)接口的處理器嗎?

2018-06-23 07:38:45

的飲料。電機(jī)控制必須保證電機(jī)僅有足夠長(zhǎng)的時(shí)間傳送一件商品。所有這些任務(wù)需要處理器等待一些事情完成以保證它不會(huì)中途停止。這個(gè)等待可能會(huì)影響到其它任務(wù)。這個(gè)系統(tǒng)是多處理器設(shè)計(jì)的一個(gè)很好的例證。 多處理器自動(dòng)

2018-12-06 10:20:18

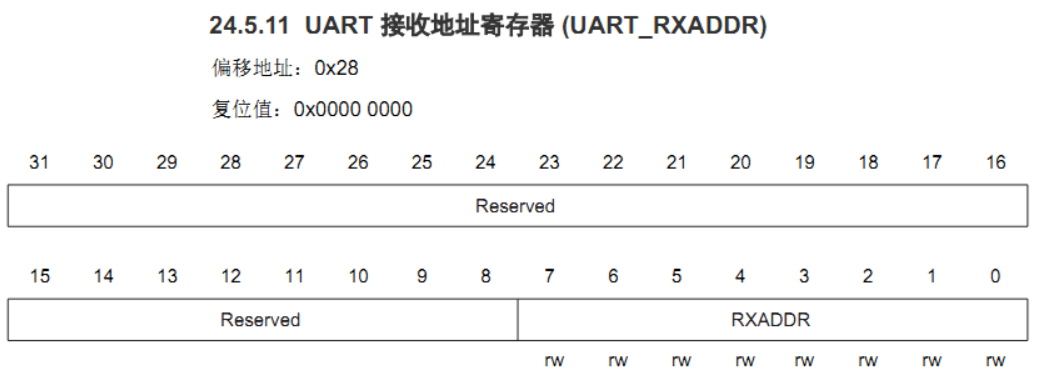

什么是MSP430多處理器?MSP430多處理器有哪些技術(shù)要點(diǎn)?

2021-05-27 06:52:20

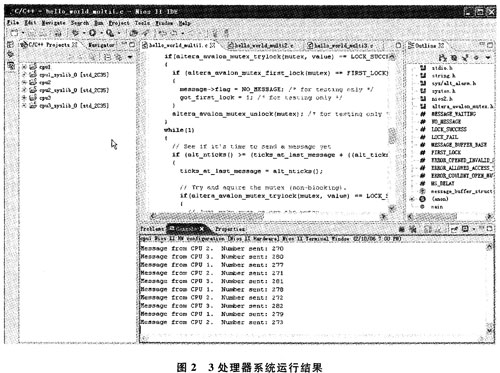

本文將對(duì)基于NiosII的SOPC多處理器系統(tǒng)的實(shí)現(xiàn)原理、設(shè)計(jì)流程和方法進(jìn)行詳細(xì)的討論。

2021-04-19 08:51:23

;(7)多處理器處理能力,具有支持多處理器無(wú)縫連接的片內(nèi)仲裁邏輯,多處理器采用統(tǒng)一尋址的方式訪(fǎng)問(wèn),可以通過(guò)簇總線(xiàn)(ClusterBus)或鏈路口(Link Ports)方便地構(gòu)成多處理器系統(tǒng)。(8)片

2019-05-21 05:00:19

,主機(jī)可以更快的速度工作,且與DSP的時(shí)鐘頻率無(wú)關(guān)。2 應(yīng)用系統(tǒng)及結(jié)果滑窗算法是數(shù)字信號(hào)處理中一種常用的基本算法,在通信、雷達(dá)、電子對(duì)抗、參數(shù)估計(jì)、信號(hào)識(shí)別中有著廣泛的應(yīng)用。滑窗算法的性質(zhì)限制了它的用途

2019-06-06 05:00:39

如何在 MA35 系列微處理器 (MPU) 上開(kāi)發(fā) AMP(非對(duì)稱(chēng)多處理)應(yīng)用程序,并通過(guò)建立多個(gè)端點(diǎn)的過(guò)程促進(jìn)與其他內(nèi)核的多通道數(shù)據(jù)傳輸。

2025-08-19 06:11:45

我想在多處理器系統(tǒng)中使用 EMIF。 為此,應(yīng)不時(shí)將地址和數(shù)據(jù)總線(xiàn)設(shè)置為高阻抗?fàn)顟B(tài)。 可能嗎? 我找不到圖紙中連接 EMIF 總線(xiàn)的位置? 直接連接到 PIN 或

2024-03-05 06:51:37

。使用多信號(hào)處理板雖可滿(mǎn)足復(fù)雜處理的要求,但系統(tǒng)成本和設(shè)計(jì)復(fù)雜度會(huì)大大增加,對(duì)于對(duì)空間質(zhì)量有嚴(yán)格要求的系統(tǒng)也是不可行的,多處理器系統(tǒng)應(yīng)用的需求越來(lái)越迫切。

2019-11-08 06:31:26

怎么實(shí)現(xiàn)多內(nèi)核處理器開(kāi)發(fā)趨勢(shì)下的高性能視頻系統(tǒng)設(shè)計(jì)?

2021-06-03 06:19:40

。使用多信號(hào)處理板雖可滿(mǎn)足復(fù)雜處理的要求,但系統(tǒng)成本和設(shè)計(jì)復(fù)雜度會(huì)大大增加,對(duì)于對(duì)空間質(zhì)量有嚴(yán)格要求的系統(tǒng)也是不可行的,多處理器系統(tǒng)應(yīng)用的需求越來(lái)越迫切。

2019-08-23 08:29:27

隨著時(shí)代的發(fā)展,單核片上可編程系統(tǒng)SOPC(Systern On a Programmable Chip)解決復(fù)雜問(wèn)題的能力與處理速度已很難滿(mǎn)足用戶(hù)的需求,面向多處理器SOPC系統(tǒng)的設(shè)計(jì)成為片上系統(tǒng)

2021-03-16 07:44:35

求一種多處理器并行計(jì)算機(jī)系統(tǒng)的設(shè)計(jì)方案

2021-04-27 06:58:57

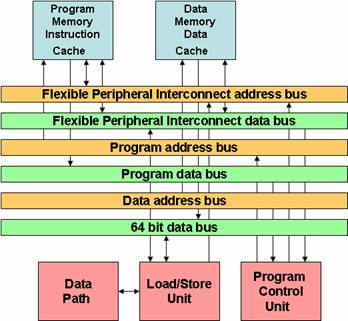

本文設(shè)計(jì)了一種在多處理器系統(tǒng)中的Nios II軟核處理器的啟動(dòng)方案,這個(gè)方案在外部處理器向Nios II的程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器加載數(shù)據(jù)時(shí),可以控制Nios II處理器的啟動(dòng)。

2021-04-27 06:52:42

片上Nios Ⅱ嵌入式軟核多處理器系統(tǒng)具有哪些優(yōu)勢(shì)?如何實(shí)現(xiàn)片上嵌入式Nios Ⅱ軟核六處理器系統(tǒng)的設(shè)計(jì)?

2021-04-19 08:17:09

原子哥,論壇上的大神們,有做過(guò)串口的多處理器通信么?如果有,大家是用空總線(xiàn)檢測(cè)還是用地址標(biāo)記的方式啊?

2019-09-05 04:35:13

機(jī)群系統(tǒng)已成為高性能計(jì)算的主流體系結(jié)構(gòu),機(jī)群模擬環(huán)境是學(xué)習(xí)機(jī)群操作的重要工具。該文提出一種基于龍芯2E多處理器硬件平臺(tái)的機(jī)群模擬方案——虛擬機(jī)群系統(tǒng)(VCS)。該系統(tǒng)在

2009-04-23 09:39:26 11

11 本文提出了一種全新的總線(xiàn)可重配置的多處理器架構(gòu)。該架構(gòu)結(jié)合了多核與可重配置處理器的優(yōu)勢(shì),具有并行性高、計(jì)算能力強(qiáng)、結(jié)構(gòu)復(fù)雜度低并且應(yīng)用領(lǐng)域廣泛靈活的特點(diǎn)。對(duì)

2009-06-13 14:11:04 11

11 定義了一種完全基于局部處理器的多處理器系統(tǒng),討論了系統(tǒng)的實(shí)現(xiàn)條件,提出了一種共享總線(xiàn)結(jié)構(gòu),建立了處理器域之間基于固定地址窗的信息交換機(jī)制,實(shí)現(xiàn)了無(wú)主多處理器

2009-06-15 08:57:52 11

11 分析了Intel-21554 非透明橋的結(jié)構(gòu)特點(diǎn),建立了利用LookupTable 基地址模式實(shí)現(xiàn)多處理器地址窗的映射機(jī)制,描述了實(shí)現(xiàn)所述地址映射的詳細(xì)過(guò)程,提供了利用標(biāo)準(zhǔn)非透明橋?qū)崿F(xiàn)無(wú)主多

2009-08-24 10:09:46 16

16 本文介紹了一種基于多PowerPC 處理器高速信號(hào)處理系統(tǒng)的Host 監(jiān)控程序的設(shè)計(jì)和實(shí)現(xiàn),該監(jiān)控程序基于Solaris,實(shí)現(xiàn)了對(duì)雷達(dá)信號(hào)處理中間結(jié)果的實(shí)時(shí)監(jiān)控和顯示。該程序利用Host 與

2009-09-01 09:44:55 10

10 SoC技術(shù)的發(fā)展使多個(gè)異構(gòu)的處理器集成到一個(gè)芯片成為可能,這種結(jié)構(gòu)已成為提高微處理器性能的重要途徑。與傳統(tǒng)的多處理器系統(tǒng)一樣,Cache一致性問(wèn)題也是片內(nèi)異構(gòu)多處理器系統(tǒng)

2009-09-26 15:02:01 11

11 多處理器實(shí)時(shí)調(diào)度理論是目前實(shí)時(shí)系統(tǒng)的關(guān)鍵技術(shù)。論文研究了PFair 調(diào)度算法在多處理器中的調(diào)度理論,在此基礎(chǔ)上,提出了一種基于PFair 調(diào)度算法的處理器分組調(diào)度算法。該算

2009-12-18 15:38:02 11

11 采用集成DSP與微處理器內(nèi)核的嵌入式應(yīng)用

采用集成 DSP 與微處理器內(nèi)核的嵌入式應(yīng)用 向

2009-04-22 11:51:37 773

773

基于NiosII的SOPC多處理器系統(tǒng)設(shè)計(jì)方法

兩個(gè)或多個(gè)微處理器一起工作來(lái)完成某個(gè)任務(wù)的系統(tǒng)稱(chēng)為“多處理器系統(tǒng)”。傳統(tǒng)基于單片機(jī)的多處理器系統(tǒng)

2009-10-17 09:28:42 1447

1447

滿(mǎn)足多媒體需求,便攜電子風(fēng)行多處理器架構(gòu)

隨著多媒體應(yīng)用要求越來(lái)越高,在小小的行動(dòng)裝置內(nèi),除了要有即時(shí)動(dòng)態(tài)影音呈現(xiàn),又必須處理大量圖型化

2009-12-15 10:30:02 992

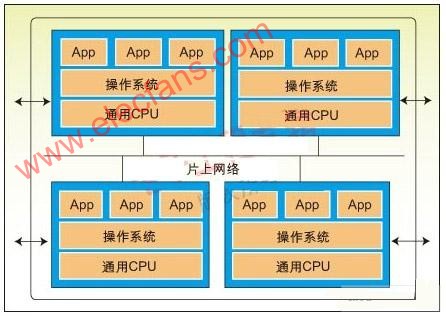

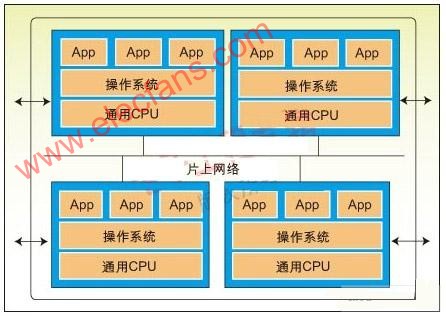

992 下面是對(duì)采用當(dāng)前開(kāi)發(fā)工具和硬件直接實(shí)現(xiàn)多內(nèi)核系統(tǒng)的三個(gè)簡(jiǎn)單模型的概述。這些多內(nèi)核設(shè)計(jì)模式不是一個(gè)為了嚴(yán)格定義一個(gè)系統(tǒng)的剛性模型,而是針對(duì)思

2010-07-10 10:08:29 759

759

多媒體手機(jī)在滿(mǎn)足傳統(tǒng)語(yǔ)音通信的同時(shí)還必須提供穩(wěn)定、高質(zhì)量的多媒體表現(xiàn),傳統(tǒng)的單處理器方案不能滿(mǎn)足這些并行任務(wù)的處理能力要求,采用具有視頻、Java和安全專(zhuān)用硬件加速器的多處理器引擎系統(tǒng)級(jí)芯片能有效解決這些多媒體任務(wù)要求,并能有效降低系統(tǒng)功耗。

2011-02-25 11:01:21 82

82 嵌入式處理器分類(lèi) 處理器造型需考慮的因素 多處理器在復(fù)雜系統(tǒng)中的應(yīng)用

2011-02-28 11:57:26 64

64 摘要:提出一種嵌入式異構(gòu)

多處理器系統(tǒng)的結(jié)構(gòu)模型,論述這種

系統(tǒng)的通信機(jī)制,并闡述在基于這種嵌入式異構(gòu)

多處理器系統(tǒng)模型的實(shí)時(shí)圖像

處理系統(tǒng)中,運(yùn)算節(jié)點(diǎn)

采用由TI公司的TMS320C6416

DSP芯片構(gòu)造的信號(hào)

處理板時(shí),在運(yùn)算節(jié)點(diǎn)與主控節(jié)點(diǎn)之間實(shí)現(xiàn)高速數(shù)據(jù)傳輸?shù)?/div>

2011-03-01 01:34:01 47

47 本篇論文采用微核心架構(gòu)在異質(zhì)性多處理器上建構(gòu)核心,經(jīng)由在不同處理器上執(zhí)行相同設(shè)計(jì)之核心以提供上層應(yīng)用程式統(tǒng)一的介面。上層應(yīng)用程式可依據(jù)其所在處理器的特性執(zhí)行相對(duì)應(yīng)的報(bào)務(wù)等待其它應(yīng)用程式的請(qǐng)求。藉由在不同處理器上執(zhí)行相同核心以及不同特性的應(yīng)

2011-03-01 13:40:11 23

23 本文提出了當(dāng)多處理機(jī)系統(tǒng)工作時(shí),為了實(shí)現(xiàn)快速有效的通信,采用使多處理器共享存儲(chǔ)器方案。IDT7134雙口RAM是本方案選擇的共享存儲(chǔ)器。針對(duì)該方案,本文給出了接口電路的硬件設(shè)計(jì)

2011-04-27 11:20:38 28

28 人們一般希望用一個(gè)處理器來(lái)處理整個(gè)系統(tǒng),但有的時(shí)候加入一個(gè)新的處理器將是一個(gè)很好選擇。盡管使用多處理器會(huì)帶來(lái)一些成本增加,但多處理器把任務(wù)劃分開(kāi)可簡(jiǎn)化設(shè)計(jì),并加快

2011-05-25 17:29:11 28

28 怎樣使用Nios II處理器來(lái)構(gòu)建多處理器系統(tǒng) Chapter 1. Creating Multiprocessor Nios II Systems Introduction to Nios II

2012-10-17 14:51:06 19

19 基于FPGA和多DSP的多總線(xiàn)并行處理器設(shè)計(jì)

2017-10-19 13:40:31 4

4 使用多處理器內(nèi)核要求軟、硬件團(tuán)隊(duì)之間進(jìn)行更多的系統(tǒng)級(jí)設(shè)計(jì)合作。基于這種理念,下面是對(duì)采用當(dāng)前開(kāi)發(fā)工具和硬件直接實(shí)現(xiàn)多內(nèi)核系統(tǒng)的三個(gè)簡(jiǎn)單模型的概述。這些多內(nèi)核設(shè)計(jì)模式不是一個(gè)為了嚴(yán)格定義一個(gè)系統(tǒng)的剛性

2017-10-26 11:48:03 0

0 ,包括3G蜂窩和寬帶無(wú)線(xiàn)基站以及國(guó)防軍事設(shè)備,如戰(zhàn)地雷達(dá)、航空器和聲納等。目前,TigerSHARC高性能數(shù)字信號(hào)處理器已成為多個(gè)DSP并行處理應(yīng)用的實(shí)用標(biāo)準(zhǔn),對(duì)加快數(shù)字信號(hào)處理技術(shù)的發(fā)展和擴(kuò)大DSP

2017-11-03 15:12:51 1

1 使用多處理器內(nèi)核要求軟、硬件團(tuán)隊(duì)之間進(jìn)行更多的系統(tǒng)級(jí)設(shè)計(jì)合作。基于這種理念,下面是對(duì)采用當(dāng)前開(kāi)發(fā)工具和硬件直接實(shí)現(xiàn)多內(nèi)核系統(tǒng)的三個(gè)簡(jiǎn)單模型的概述。這些多內(nèi)核設(shè)計(jì)模式不是一個(gè)為了嚴(yán)格定義一個(gè)系統(tǒng)的剛性

2018-07-15 11:21:00 3886

3886

與低功耗的系統(tǒng)需求,但異構(gòu)多處理器結(jié)構(gòu)下軟件編程難度大的問(wèn)題以及如何優(yōu)化頂層應(yīng)用在多處理器設(shè)備上的運(yùn)行性能都是目前亟待解決的技術(shù)難題.針對(duì)以上問(wèn)題,i-計(jì)并實(shí)現(xiàn)了一個(gè)面向異構(gòu)多處理器設(shè)備的自適應(yīng)命令解釋系統(tǒng)

2017-12-19 15:06:56 0

0 針對(duì)多處理器系統(tǒng)中隨機(jī)到達(dá)的任務(wù),設(shè)計(jì)了可靠性約束下的節(jié)能調(diào)度算法( ESACR)。該算法在滿(mǎn)足任務(wù)截止期限的前提下選擇一個(gè)預(yù)計(jì)產(chǎn)生能耗最小的處理器以節(jié)能,在單個(gè)處理器上運(yùn)用最早截止期限優(yōu)先策略進(jìn)行

2018-01-08 14:20:44 0

0 隨著多處理器實(shí)時(shí)系統(tǒng)在安全性攸關(guān)系統(tǒng)中的廣泛應(yīng)用,保證這類(lèi)系統(tǒng)的正確性成為一項(xiàng)重要的工作.可調(diào)度性是實(shí)時(shí)系統(tǒng)正確性的一項(xiàng)關(guān)鍵性質(zhì).它表示系統(tǒng)必須滿(mǎn)足的一些時(shí)間要求.傳統(tǒng)的可調(diào)度性分析方法結(jié)論保守或者

2018-02-06 16:46:37 0

0 許多現(xiàn)代嵌入式處理系統(tǒng)是多處理器系統(tǒng),包含CPU和ASIC,并應(yīng)用實(shí)時(shí)操作系統(tǒng),具有復(fù)雜的硬件和軟件結(jié)構(gòu)。

2018-04-09 17:41:21 8

8 對(duì)于一個(gè)具有多個(gè)CPU的多處理器系統(tǒng),在單板或系統(tǒng)中的一個(gè)或多個(gè)設(shè)備中,CPU和內(nèi)核有時(shí)可以相互作用或依賴(lài)于其他CPU或內(nèi)核的動(dòng)作。單個(gè)設(shè)備上的多個(gè)內(nèi)核甚至共享一個(gè)普通的內(nèi)存塊,其中包含可執(zhí)行代碼或SysDeDATA。因此,經(jīng)常需要調(diào)試多個(gè)CPU或多個(gè)內(nèi)核,同時(shí)嘗試調(diào)試提供處理器間通信的代碼。

2018-04-25 15:36:51 8

8 DSP共享外部總線(xiàn)、鏈路口點(diǎn)對(duì)點(diǎn)通信、在多通道模式下使用DSP的幾個(gè)串口等幾種不同的工作模式.以用于雷達(dá)信號(hào)處理、語(yǔ)音和圖像信號(hào)處理等各個(gè)領(lǐng)域的系統(tǒng)開(kāi)發(fā)過(guò)程中。文中以VisualDSP++4.0為開(kāi)發(fā)平臺(tái).詳細(xì)介紹了利用Visual DSP++4.0開(kāi)發(fā)多處理器系統(tǒng)(MP)的基本思想和方法,給出了基

2019-02-25 11:08:27 7

7 按照今天的標(biāo)準(zhǔn),早期的基于微處理器的系統(tǒng)很簡(jiǎn)單,尤其是因?yàn)樗鼈兺ǔV皇褂靡粋€(gè)處理器(可能只有一些協(xié)處理器,如浮點(diǎn)協(xié)處理器),而且指令集相對(duì)較簡(jiǎn)單,運(yùn)行速度很低時(shí)鐘頻率。該處理器通過(guò)一個(gè)簡(jiǎn)單的讀/寫(xiě)和信令協(xié)議,通過(guò)一個(gè)8位或16位數(shù)據(jù)總線(xiàn)與少量相對(duì)簡(jiǎn)單的存儲(chǔ)器和外圍設(shè)備進(jìn)行通信。

2019-10-06 09:38:00 2364

2364

同步多處理器,英文為Synchronous Multi-Processors,縮寫(xiě)為SMP。同步多處理器系統(tǒng)在工作的時(shí)候,每當(dāng)一個(gè)任務(wù)完成后,空閑的處理器會(huì)立刻尋找下一個(gè)新的任務(wù),對(duì)于外部而言,這兩顆處理器是一個(gè)整體,共同完成同一個(gè)工作。

2020-06-02 09:16:17 1451

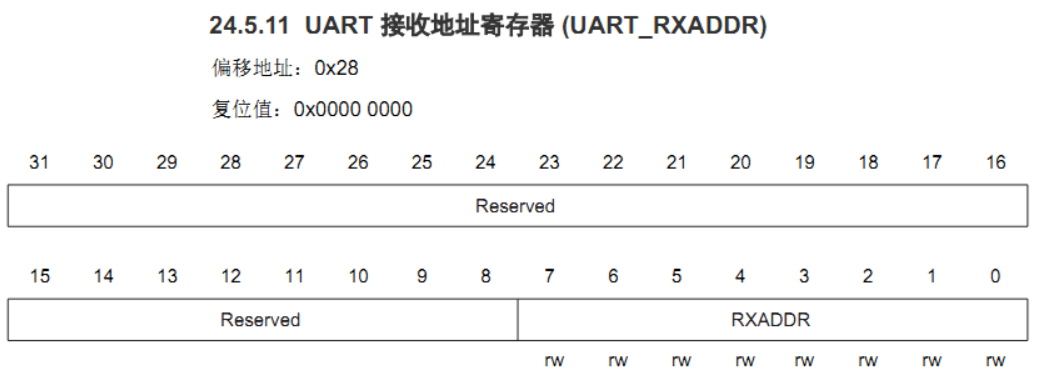

1451 MM32F013x系列MCU支持UART多處理器通信,其工作原理是主從機(jī)設(shè)備采用復(fù)用漏極開(kāi)路,主從機(jī)外部接上拉電阻,在空閑時(shí)使從機(jī)處于靜默模式,主機(jī)要控制從機(jī)執(zhí)行任務(wù)時(shí)主機(jī)發(fā)送指令喚醒從機(jī)并發(fā)送數(shù)據(jù)控制從機(jī)執(zhí)行相應(yīng)任務(wù)。

2022-02-21 10:05:22 1954

1954

MM32F013x系列MCU支持UART多處理器通信,其工作原理是主從機(jī)設(shè)備采用復(fù)用漏極開(kāi)路,主從機(jī)外部接上拉電阻,在空閑時(shí)使從機(jī)處于靜默模式,主機(jī)要控制從機(jī)執(zhí)行任務(wù)時(shí)主機(jī)發(fā)送指令喚醒從機(jī)并發(fā)送數(shù)據(jù)控制從機(jī)執(zhí)行相應(yīng)任務(wù)。

2021-01-22 06:33:51 6

6 ADSP-BF561:Blackfin嵌入式對(duì)稱(chēng)多處理器數(shù)據(jù)手冊(cè)

2021-03-21 06:39:02 9

9 AD14160:Quad-SHARC?DSP多處理器系列過(guò)時(shí)產(chǎn)品手冊(cè)

2021-04-15 19:13:10 4

4 AD14060/AD14060L:Quad-SHARC?多處理器DSP系列產(chǎn)品手冊(cè)

2021-04-25 19:23:54 1

1 EE-202:使用多處理器LDFS的專(zhuān)家鏈接器

2021-05-14 09:22:30 2

2 EE-167:使用VisualDSP++?的TigerSHARC?多處理器系統(tǒng)簡(jiǎn)介

2021-05-27 18:39:07 12

12 AD14160 Quad-SHARC?DSP多處理器系列過(guò)時(shí)數(shù)據(jù)表

2021-06-16 15:31:36 4

4 在單片機(jī)系統(tǒng)中,多處理器是指多個(gè)相同類(lèi)型或者不同類(lèi)型的單片機(jī)協(xié)作處理同一個(gè)系統(tǒng)的不同工作。它們之間必須具備一定的數(shù)據(jù)交換和協(xié)作處理能力,共同完成一個(gè)系統(tǒng)化的工作。不同處理器之間可以采用數(shù)據(jù)交換方式

2021-06-17 15:41:58 2583

2583

在上一次的靈動(dòng)微課堂中和大家分享過(guò)MM32F013x-UART 9bit通信實(shí)例,本次微課堂在此實(shí)例的基礎(chǔ)上實(shí)現(xiàn)UART多處理器通信。MM32F013x系列MCU...

2022-01-25 19:55:23 4

4 riscvOVPsim 的可用升級(jí)包括虛擬平臺(tái)開(kāi)發(fā)和仿真、多核軟件開(kāi)發(fā)、可擴(kuò)展平臺(tái)套件和多處理器主機(jī) (MPonMP) 加速軟件上的 QuantumLeap 多處理器目標(biāo)。

2022-06-21 09:40:21 1586

1586

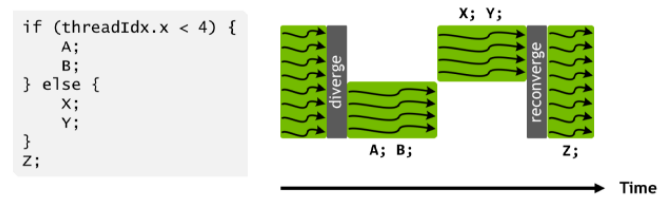

按照軟件級(jí)別,SIMT層面,流式多處理器由線(xiàn)程塊組成,每個(gè)線(xiàn)程塊由多個(gè)線(xiàn)程束組成;SIMD層面,每個(gè)線(xiàn)程束內(nèi)部在同一時(shí)間執(zhí)行相同指令,對(duì)應(yīng)不同數(shù)據(jù),由統(tǒng)一的線(xiàn)程束調(diào)度器(Warp scheduler)調(diào)度。

2023-03-30 10:05:37 3634

3634 流式多處理器(Stream Multi-processor,SM)是構(gòu)建整個(gè) GPU的核心模塊(執(zhí)行整個(gè) Kernel Grid),一個(gè)流式多處理器上一般同時(shí)運(yùn)行多個(gè)線(xiàn)程塊。每個(gè)流式多處理器可以視為

2023-04-03 14:28:09 3009

3009

流式多處理器(Stream Multi-processor,SM)是構(gòu)建整個(gè) GPU的核心模塊(執(zhí)行整個(gè) Kernel Grid),一個(gè)流式多處理器上一般同時(shí)運(yùn)行多個(gè)線(xiàn)程塊。每個(gè)流式多處理器可以視為

2023-04-03 14:28:13 2626

2626

? ARM Cortex系列那么多處理器,該怎么區(qū)分?

2023-10-26 15:45:58 3529

3529

電子發(fā)燒友網(wǎng)站提供《基于VPX6—460的多處理器通信設(shè)計(jì).pdf》資料免費(fèi)下載

2023-11-08 14:37:19 0

0 電子發(fā)燒友網(wǎng)站提供《基于VPX6-460的多處理器通信設(shè)計(jì).pdf》資料免費(fèi)下載

2023-11-13 10:13:17 0

0 電子發(fā)燒友網(wǎng)站提供《為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電.pdf》資料免費(fèi)下載

2024-09-25 10:54:09 0

0 隨著計(jì)算需求的日益增長(zhǎng),單處理器系統(tǒng)已經(jīng)無(wú)法滿(mǎn)足高性能計(jì)算的需求。多處理器系統(tǒng)應(yīng)運(yùn)而生,它們通過(guò)將多個(gè)處理器集成到一個(gè)系統(tǒng)中來(lái)提高計(jì)算能力。在多處理器系統(tǒng)中,有兩種主要的架構(gòu):對(duì)稱(chēng)多處理器

2024-10-10 15:58:03 3111

3111 在現(xiàn)代計(jì)算機(jī)系統(tǒng)中,對(duì)稱(chēng)多處理器(SMP)架構(gòu)已經(jīng)成為主流。這種架構(gòu)允許多個(gè)處理器共享相同的內(nèi)存地址空間和系統(tǒng)資源,從而提高了系統(tǒng)的處理能力和吞吐量。然而,為了充分利用SMP系統(tǒng)的性能,操作系統(tǒng)

2024-10-10 16:34:40 1005

1005 對(duì)稱(chēng)多處理器(Symmetric Multi-Processing,簡(jiǎn)稱(chēng)SMP)是一種多處理器系統(tǒng),其中多個(gè)處理器共享相同的物理內(nèi)存和其他資源,并且操作系統(tǒng)將它們視為單一的邏輯處理器。SMP系統(tǒng)

2024-10-10 16:36:10 1595

1595 電子發(fā)燒友網(wǎng)站提供《AD14060/AD14060L:四通道SHARC DSP多處理器系列數(shù)據(jù)資料.pdf》資料免費(fèi)下載

2025-01-03 15:57:08 0

0 電子發(fā)燒友網(wǎng)站提供《EE-202:將專(zhuān)家鏈接器用于多處理器LDFs.pdf》資料免費(fèi)下載

2025-01-06 14:33:14 0

0 電子發(fā)燒友網(wǎng)站提供《EE-148:使用VisualDSP的SHARC多處理器系統(tǒng)簡(jiǎn)介.pdf》資料免費(fèi)下載

2025-01-07 14:37:35 0

0 電子發(fā)燒友網(wǎng)站提供《EE-167:使用VisualDSP的TigerSHARC多處理器系統(tǒng)簡(jiǎn)介.pdf》資料免費(fèi)下載

2025-01-14 15:12:27 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論