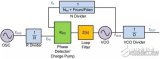

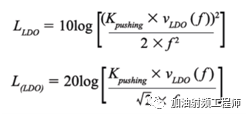

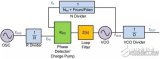

相位噪聲是時鐘、射頻頻綜最為關(guān)注的技術(shù)指標(biāo)之一。影響鎖相環(huán)相噪的因素有很多,比如電源、參考源相噪、VCO自身的相噪、環(huán)路濾波器的設(shè)置等。其中,電源引入的低頻噪聲往往對鎖相環(huán)的近端相噪有著很大的影響。##LDO噪聲與VCO輸出相噪的關(guān)系 ##TPS7A8101輸出電路優(yōu)化及對頻綜相噪的影響

2014-05-14 11:18:30 9825

9825 相位噪聲是時鐘、射頻頻綜最為關(guān)注的技術(shù)指標(biāo)之一。影響鎖相環(huán)相噪的因素有很多,比如電源、參考源相噪、VCO 自身的相噪、環(huán)路濾波器的設(shè)置等。其中,電源引入的低頻噪聲往往對鎖相環(huán)的近端相噪有著很大

2022-08-05 10:25:00 3998

3998 同一信號,經(jīng)過不同的放大器后,輸出信號有的相噪好,有的相噪差。

2023-08-25 09:11:38 2484

2484

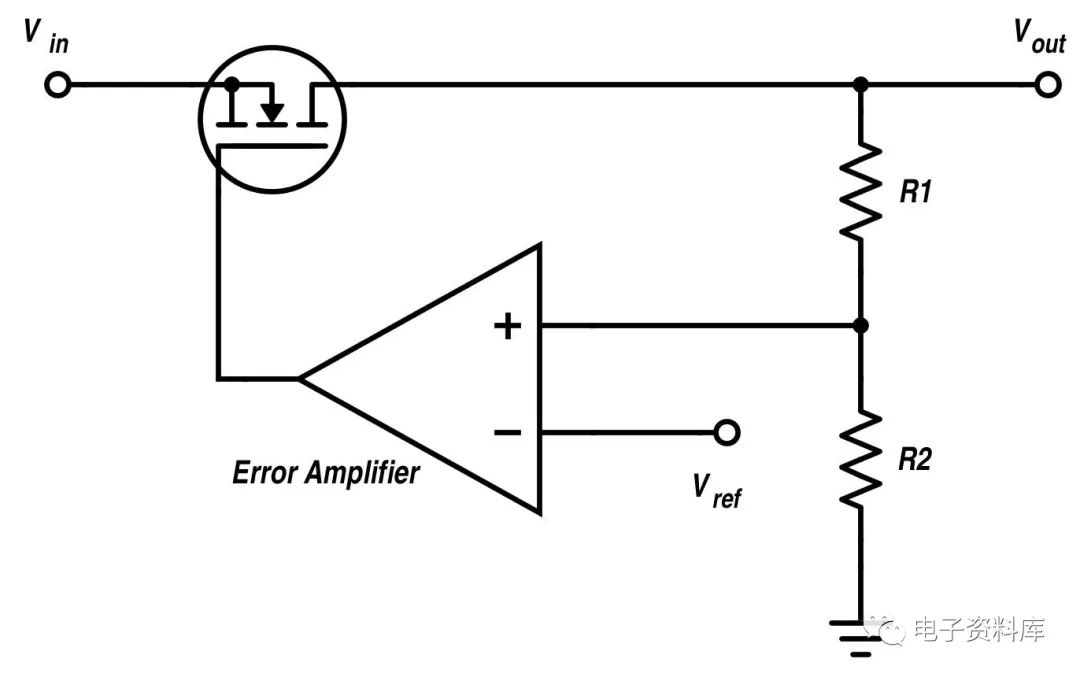

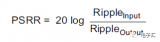

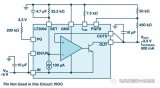

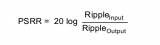

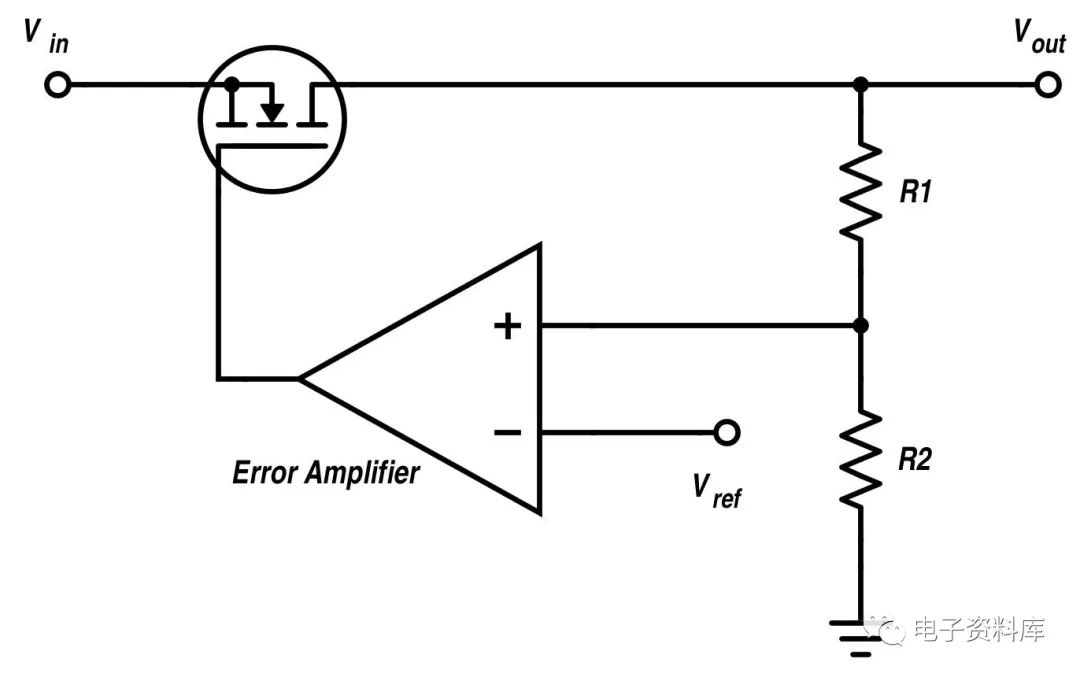

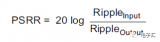

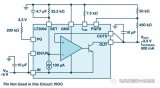

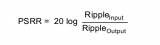

在本文中,我們將介紹噪聲和電源抑制比 (PSRR) 在低壓差 (LDO) 穩(wěn)壓器中的影響。讓我們簡要討論一下什么是 LDO。

2023-09-26 14:29:43 6745

6745

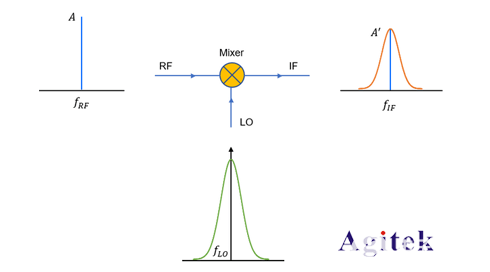

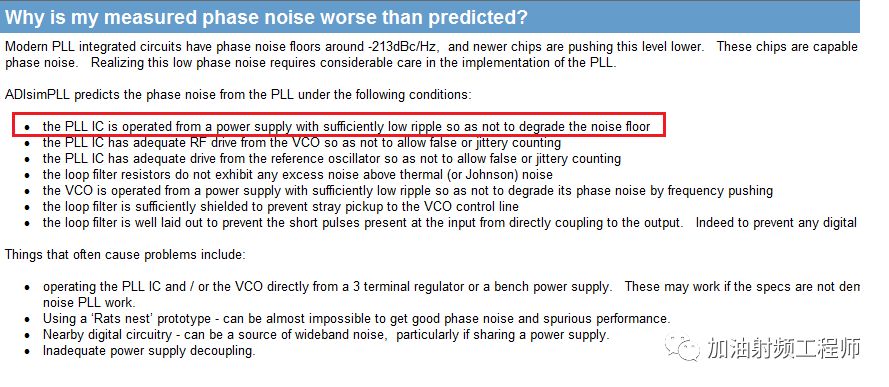

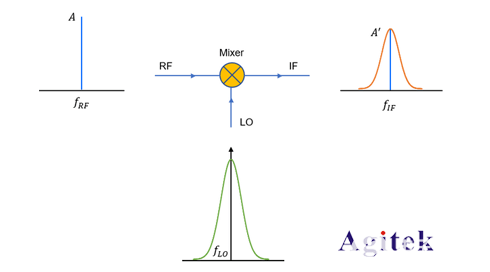

假設(shè)射頻系統(tǒng)在 2.4GHz 頻率下工作,那么 LDO 噪聲會將 2.4GHz 上下的 VCO 噪聲頻譜提高至 LDO帶寬。在 VCO 原始噪聲圖中加入圖 2-1 所示的 LDO 噪聲后,中心頻率附近的 VCO 本底噪聲等級提高。

2024-03-05 11:00:05 2198

2198

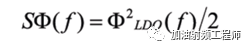

本文首先簡要地介紹了LDO的噪聲來源及環(huán)路穩(wěn)定性對輸出噪聲的影響;其次,根據(jù)調(diào)頻理論推導(dǎo)出VCO的相位噪聲與LDO的噪聲頻譜密度的理論計算關(guān)系。在此基礎(chǔ)上,為了驗證LDO噪聲對射頻頻綜輸出相噪

2019-06-20 06:57:18

在我們之前的博客中,我們談到《低壓降(LDO)穩(wěn)壓器之理想與現(xiàn)實》,介紹了什么是LDO穩(wěn)壓器及其噪聲參數(shù)的基本信息。今天,我們將進一步詳細(xì)談?wù)勈裁词?b class="flag-6" style="color: red">噪聲,它是如何分類的,并介紹安森美半導(dǎo)體提供的超低噪聲LDO。

2019-07-26 07:52:20

噪聲電源供電時,時鐘或者轉(zhuǎn)換器 IC 無法達到最高性能。僅僅只是少量的電源噪聲,便會對性能產(chǎn)生極大的負(fù)面影響。本文將對一種基本 LDO 拓?fù)溥M行仔細(xì)研究,找出其主要噪聲源,并給出最小化其輸出噪聲的一些

2018-11-29 17:02:59

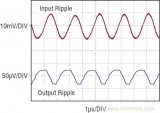

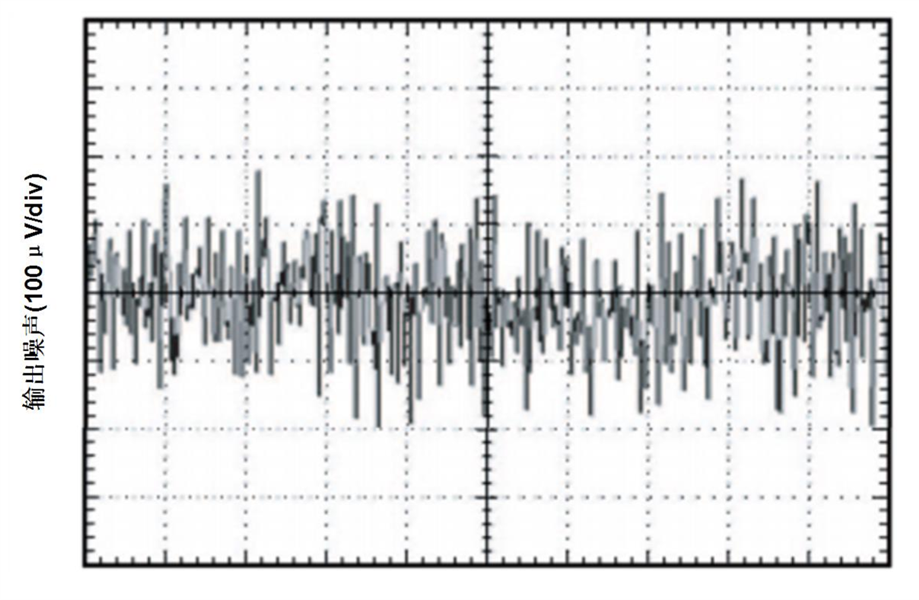

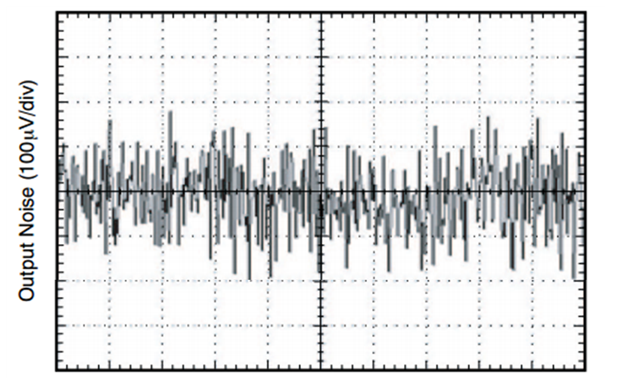

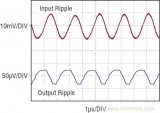

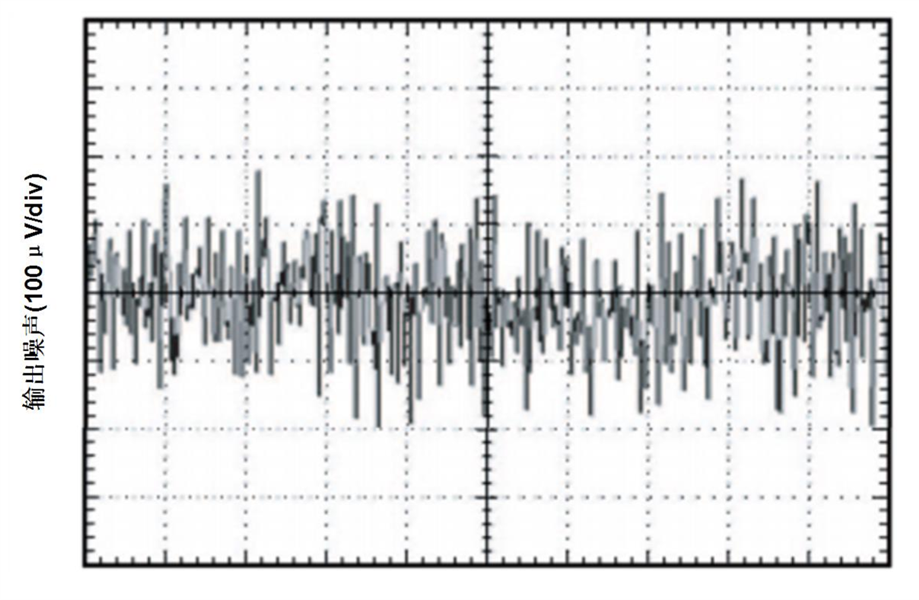

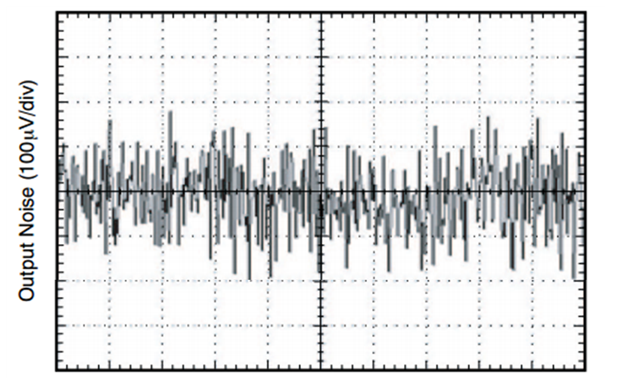

理想的LDO具備沒有交流元件的電壓軌。但缺點在于LDO會和其他電子設(shè)備一樣生成本體噪聲。圖 1 顯示了這種噪聲在時間域中的表現(xiàn)。

2019-07-31 07:30:39

相位噪聲是時鐘、射頻頻綜最為關(guān)注的技術(shù)指標(biāo)之一。影響鎖相環(huán)相噪的因素有很多,比如電源、參考源相噪、VCO 自身的相噪、環(huán)路濾波器的設(shè)置等。其中,電源引入的低頻噪聲往往對鎖相環(huán)的近端相噪有著很大

2019-08-21 08:04:28

現(xiàn)在很多集成VCO的頻率合成器的設(shè)計思想,都是利用輸出端加分頻器來擴展輸出范圍。

2019-08-22 06:18:43

VCO,鑒相頻率為10MHz,VCO=2.8GHz,環(huán)路濾波器按照軟件默認(rèn)設(shè)置(二階),AD9517輸出頻率范圍50MHz-300MHz。用頻譜儀測量各個AD9517時鐘輸出管腳的頻譜,發(fā)現(xiàn)不管時鐘頻率

2018-10-24 15:57:37

10dB。此時的實驗條件如下:采用的參考3.5GHz的相位噪聲如下圖2所示:

圖2

手冊的殘余相噪如圖3:

圖3

輸出的300MHz相噪如圖4:

圖4

問題1:此時輸出300MHz的相位噪聲為啥

2024-12-19 07:12:59

我在用HMC703+HMC733輸出0.1-21GHz時,發(fā)現(xiàn)在VCO輸出頻率在高于18GHz后,將帶寬span設(shè)置為10k時,輸出信號底噪不停抖動,且輸出相位噪聲惡化嚴(yán)重,請問是什么原因造成的,LPF采用100k有源設(shè)計??

2018-08-09 07:20:32

如題。我的hmc833配置輸出為50MHZ,32分頻。 當(dāng)輸入?yún)⒖紴?0MHz,功率為8dBm時,輸出相噪在100KHZ處為-122dBc/Hz。 當(dāng)輸入?yún)⒖紴?0MHz,輸入功率為8dBm時,輸出

2018-09-20 14:46:02

差了7dB

3.139G,無論是VCO輸出還是4分頻,8分頻輸出,其相噪都不會隨功率變化,僅二分頻會有此現(xiàn)象;

TICS pro配置如下

相噪測試數(shù)據(jù)如下:

請問該現(xiàn)象是否正常,造成該現(xiàn)象的原因是什么?

2024-11-08 16:16:51

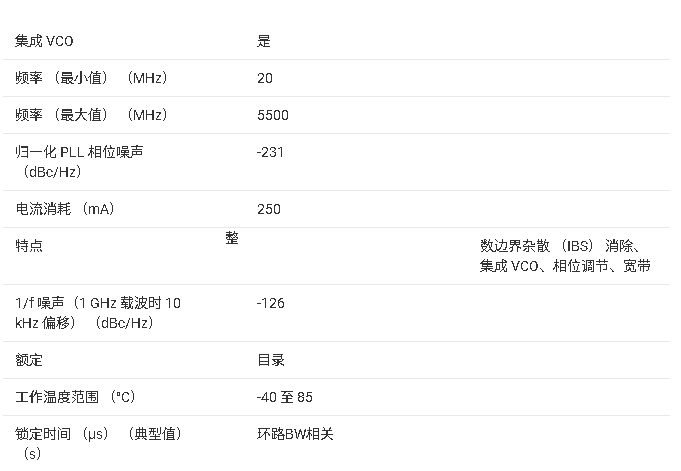

中心頻率校準(zhǔn)帶有5 V電荷泵的外部VCO選項倍頻器輸出的基本VCO抑制高于20 dB內(nèi)部寬帶匹配射頻輸出在6 GHz時提供+6 dBm,在12 GHz時提供+4 dBm單端集成低噪聲LDO最大鑒相器

2018-08-24 09:07:47

中心頻率校準(zhǔn)帶有5 V電荷泵的外部VCO選項倍頻器輸出的基本VCO抑制高于20 dB內(nèi)部寬帶匹配射頻輸出在6 GHz時提供+6 dBm,在12 GHz時提供+4 dBm單端集成低噪聲LDO最大鑒相器

2018-08-24 09:08:55

中心頻率校準(zhǔn)帶有5 V電荷泵的外部VCO選項倍頻器輸出的基本VCO抑制高于20 dB內(nèi)部寬帶匹配射頻輸出在6 GHz時提供+6 dBm,在12 GHz時提供+4 dBm單端集成低噪聲LDO鑒相器頻率

2018-11-12 10:12:30

Z-COMM VCO的相位噪聲測量AN-109Phase Noise Measurement Of Z-COMM VCOsPublished phase noise performance can

2009-06-13 07:31:08

壓電阻時候比鎖相環(huán)設(shè)計時在100Hz處相噪優(yōu)化10db!鎖相環(huán)工作狀態(tài)下,100Hz的相噪不是很穩(wěn)定有6db的波動!這個是什么原因呢!adf4002和vcxo采用的一個ldo lp5912給的電,每個饋電都采用π形電感電容濾波!

2019-01-29 10:35:53

LDO。噪聲分為兩類:內(nèi)部噪聲和外部噪聲。內(nèi)部噪聲是不可避免的,每個電子設(shè)備都會產(chǎn)生內(nèi)部噪聲。LDO由理想的源供電,這意味著它不受外界影響,因此在輸入端沒有外部噪聲(雖然LDO在輸出端確實有

2020-10-27 07:29:38

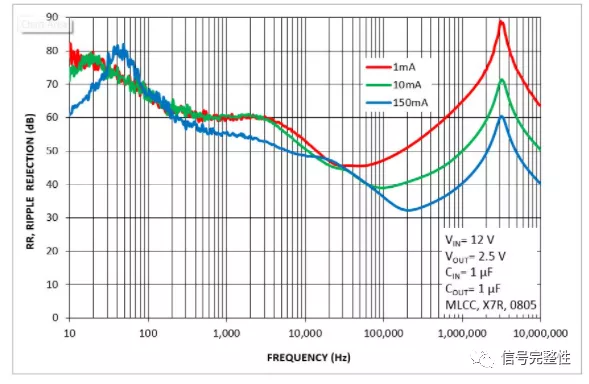

用LDO給運放或者ADC供電,運放和ADC都有PSRR,而且在低頻端PSRR都高達80dB,LDO的內(nèi)部噪聲剛好也是低頻的,按理說,運放和ADC的PSRR可以把LDO輸出的內(nèi)部噪聲抑制的干干凈凈

2025-01-08 07:49:53

用LDO給運放或者ADC供電,運放和ADC都有PSRR,而且在低頻端PSRR都高達80dB,LDO的內(nèi)部噪聲剛好也是低頻的,按理說,運放和ADC的PSRR可以把LDO輸出的內(nèi)部噪聲抑制的干干凈凈

2024-09-03 07:32:36

在我們之前的博客中,我們談到《低壓降(LDO)穩(wěn)壓器之理想與現(xiàn)實》,介紹了什么是LDO穩(wěn)壓器及其噪聲參數(shù)的基本信息。今天,我們將進一步詳細(xì)談?wù)勈裁词?b class="flag-6" style="color: red">LDO噪聲?LDO噪聲是如何分類的?

2019-08-01 07:20:41

LDO。噪聲分為兩類:內(nèi)部噪聲和外部噪聲。內(nèi)部噪聲是不可避免的,每個電子設(shè)備都會產(chǎn)生內(nèi)部噪聲。LDO由理想的源供電,這意味著它不受外界影響,因此在輸入端沒有外部噪聲(雖然LDO在輸出端確實有

2018-10-30 09:04:53

分析儀或相噪分析儀則存在許多局限且需要額外的設(shè)備投資,如何協(xié)助數(shù)字領(lǐng)域的專業(yè)人士利用現(xiàn)有的數(shù)字實時示波器進行高精度的抖動分析和相噪測試?

2020-03-09 13:52:45

在從電源(無論是交流線路還是電池)到電子負(fù)載的長電路中,低壓差(LDO)線性穩(wěn)壓器通常需要覆蓋“最后一英里”。在這里,噪聲開關(guān)調(diào)節(jié)器不得不支持安靜的LDO來為關(guān)鍵的電子負(fù)載供電。靈活的LDO(圖1

2019-01-17 19:22:05

我有一塊ADF4351的開發(fā)板,但是我現(xiàn)在想用相位噪聲測試儀測量ADF4351的VCO開環(huán)相位噪聲,但是卻不知道怎樣設(shè)置,如果僅僅只是將振蕩器移除,測量得到的相位噪聲是VCO的閉環(huán)相位噪聲,有沒有大神知道怎么設(shè)置才能測量VCO的開環(huán)相位噪聲, 希望能夠指點一二 謝謝

2018-08-02 07:46:23

NCP4688 150 mA,低噪聲,LDO線性穩(wěn)壓器的典型應(yīng)用。 NCP4688是一款CMOS 150 mA LDO線性穩(wěn)壓器,具有高輸出電壓精度,具有低噪聲輸出電壓和高紋波抑制性能。低電平輸出噪聲10 Vrms通常保持在任何輸出電壓

2020-07-25 11:12:30

決定。也即是PLL對參考晶體噪聲源呈現(xiàn)低通特性,而對VCO噪聲呈現(xiàn)高通特性。因此通過常規(guī)的分頻鎖相方式,由于鑒相器鑒相頻率較高以及噪聲基底的惡化無法取得較好的相噪指標(biāo)。本振相位噪聲水平很高的時候,射頻

2019-06-20 08:09:50

LDO是一種微功耗的低壓差線性穩(wěn)壓器,它具有極低的自有噪聲和較高的電源抑制比(PSRR)。SGM2007高性能低壓差線性穩(wěn)壓器在10Hz至100kHz頻率范圍內(nèi)的輸出噪聲為30 μV(RMS),在

2019-06-19 06:43:54

本文設(shè)計了一個適用于以太網(wǎng)物理層芯片時鐘同步PLL的高寬帶低噪聲VCO,采用了具有良好抗噪能力的交叉耦合電流饑餓型差分環(huán)形振蕩器。仿真結(jié)果表明,在同樣輸入噪聲和環(huán)境噪聲的情況下,本文的VCO中心

2021-02-25 07:39:43

寬帶VCO在堅固耐用的RoHS兼容模塊中結(jié)合了低相位噪聲和高輸出功率

2019-09-29 14:18:47

單獨仿真VCO的相位噪聲時,正常出現(xiàn)結(jié)果,在加入LDO為其供電后,再仿真相位噪聲出現(xiàn)如下錯誤:有經(jīng)驗的前輩們求解答!!!

2021-06-25 06:38:52

VCO,并配有輸出分頻器以實現(xiàn)更低的頻率。一般而言,低VCO相位噪聲取決于高VCO振蕩電路Q.高VCO電路Q意味著VCO的小頻率范圍和靈敏度(Kv),這是VCO設(shè)計中的基本權(quán)衡。許多倍頻程調(diào)諧VCO通過

2018-10-26 11:48:38

經(jīng)常看到很多論文上面都描述電源噪聲對VCO相位噪聲的影響,但一直都沒弄明白,電源噪聲是怎么影響VCO的頻率抖動的,就拿一個我最近在做的VCO電路圖來說, 電源噪聲是怎么對VCO造成影響的?是由于電容

2021-06-24 06:11:40

ADF4351使用板子上的晶振作為參考鐘時輸出相噪還可以,參考鐘使用外接信號源時輸出相噪變差很多,這是怎么回事?怎么解決???晶振和信號源輸出參考鐘的相噪差不多

2018-07-30 06:11:57

ADF4351輸出,相噪遠(yuǎn)不及器件參考值理想。而且在離中心頻率最近處的雜散出現(xiàn)在偏離中心頻率5KHz的地方。從頻譜來分析,我估計如果能減小或者消除該雜散,則相噪應(yīng)該可以明顯變好。電源我采用了兩顆

2018-09-29 15:40:47

什么是抖動?時鐘抖動有哪幾種測量方法 ?什么是相噪?測試相噪有哪幾種測量方法?抖動與相噪是如何轉(zhuǎn)換的?

2021-04-29 06:13:34

(如ADF4350,HMC830),與直接把這個clipped-sine wave 信號送入VCO鎖出來的信號相比相噪在1K地方惡化比較明顯,這個情況是正常的嗎? 這個惡化是由什么引起的?buffer的抖動30fs按說不是buffer引起的惡化吧。 謝謝。

2018-08-22 09:35:21

關(guān)于ADF4350不同頻點相噪相差很遠(yuǎn)的提問?現(xiàn)在發(fā)現(xiàn)ADF4350在2.871G和2.870G這里有個分界點,在2.871G頻點處,相位噪聲在100k的地方可以達到-105dBc/Hz,而在

2018-11-02 09:30:13

相位噪聲是表征CW信號頻譜純度的非常重要的參數(shù),衡量了信號頻率的短期穩(wěn)定度。通常所說的相噪為單邊帶(SSB) 相位噪聲,相噪的好壞對于系統(tǒng)的性能至關(guān)重要!· 對于終端通信而言,如果接收機LO的相噪

2020-07-01 11:12:45

LDO穩(wěn)壓器的PSRR和輸出噪聲在RF電路中的選擇:LDO是一種微功耗的低壓差線性穩(wěn)壓器,它具有極低的自有噪聲和較高的電源抑制比(PSRR)。SGM2007高性能低壓差線性穩(wěn)壓器在10Hz至100kHz頻率

2009-09-25 08:19:27 19

19 壓控振蕩器(VCO)是鎖相環(huán)路的重要組成部分。隨著電子技術(shù)的發(fā)展,出現(xiàn)了許多集成的VCO芯片。考慮到高頻率穩(wěn)定度、低相噪的要求,這里采用Agilent公司生產(chǎn)的低噪聲晶體管HBFP0450來設(shè)

2010-06-05 11:57:21 25

25 免調(diào)中頻VCO的實現(xiàn)分立元件VCO能夠提供足夠的自由度來滿足大多數(shù)系統(tǒng)的性能要求(調(diào)諧范圍、輸出功率、相位噪聲、電流消耗等等)。然而,對于具有較大批量、價格敏感的

2009-02-08 11:20:10 1187

1187

羅德與施瓦茨FSPN26相噪測試儀 羅德與施瓦茨R&S FSPN26 相位噪聲分析儀和 VCO 測試儀FSPN26相噪測試儀RS FSPN26主要特點 優(yōu)異

2025-02-25 15:51:17

本文將對一種基本 LDO 拓?fù)溥M行仔細(xì)研究,找出其主要噪聲源,并給出最小化其輸出噪聲的一些方法。

2012-12-27 15:23:32 56

56 R&S新型相噪分析和VCO測試儀能夠快速進行超低靈敏度相位噪聲測量。借助R&S FSWP,用戶可輕松進行脈沖源相噪和射頻部件的剩余相噪測量。另外,R&S FSWP亦可輕松升級成一臺完整的信號和頻譜分析儀。

2015-06-05 16:21:16 4608

4608 低噪聲LDO可為眾多的模擬/RF 設(shè)計供電,包括頻率合成器(PLL/VCO)、RF混頻器和調(diào)制器、高速和高分辨率數(shù)據(jù)轉(zhuǎn)換器(ADC和DAC)以及高精度傳感器。然而,這些應(yīng)用對于功能和靈敏度的要求已經(jīng)開始逐步考驗著傳統(tǒng)低噪聲LDO的性能極限。

2016-11-05 02:09:15 2014

2014

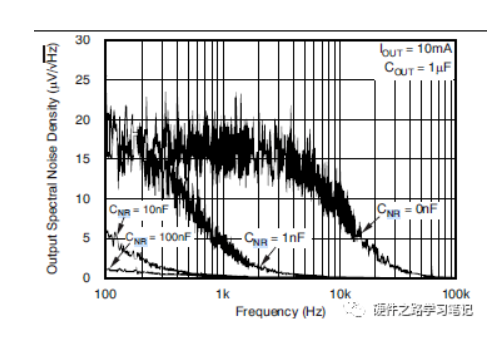

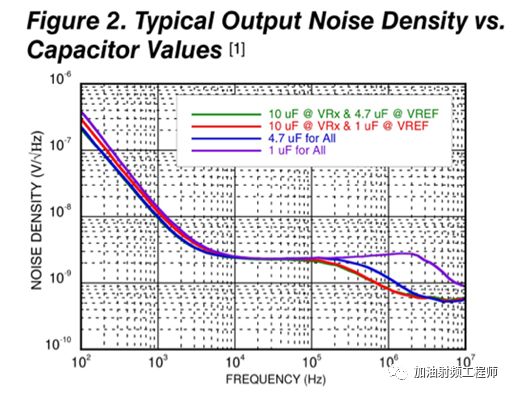

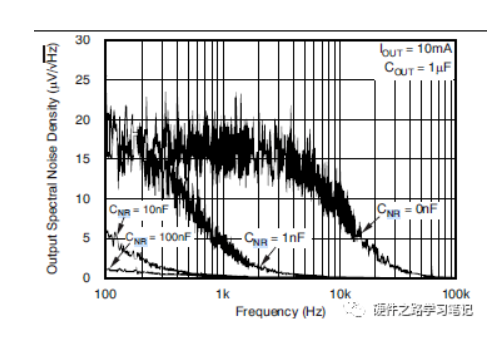

噪聲對高性能模擬電路設(shè)計人員來說是一個極其重要的參 數(shù)。對高速時鐘、模數(shù)轉(zhuǎn)換器 (ADC)、數(shù)模轉(zhuǎn)換器 (DAC)、電壓控制振蕩器(VCO)和鎖相環(huán)(PLL)來說尤其如 此。降低輸出電壓噪聲的關(guān)鍵是

2017-09-12 17:41:27 11

11 噪聲傳導(dǎo)路徑和靜噪基本概念

2017-11-27 14:18:01 4

4 這個應(yīng)用報告解釋了LDO的噪聲和PSRR之間的差異。

2018-05-23 16:36:23 13

13 現(xiàn)在很多集成VCO的頻率合成器的設(shè)計思想,都是利用輸出端加分頻器來擴展輸出范圍,如圖1所示。比如ADI的HMC832,其VCO的頻率為1500~3000MHz,利用其后的分頻器(1/2/4/6/…60/62),最終獲得25MHz~3000MHz的頻率覆蓋范圍。

2018-05-25 09:54:00 8704

8704

相位噪聲是時鐘、射頻頻綜最為關(guān)注的技術(shù)指標(biāo)之一。影響鎖相環(huán)相噪的因素有很多,比如電源、參考源相噪、VCO 自身的相噪、環(huán)路濾波器的設(shè)置等。其中,電源引入的低頻噪聲往往對鎖相環(huán)的近端相噪有著很大

2018-07-19 10:19:39 34

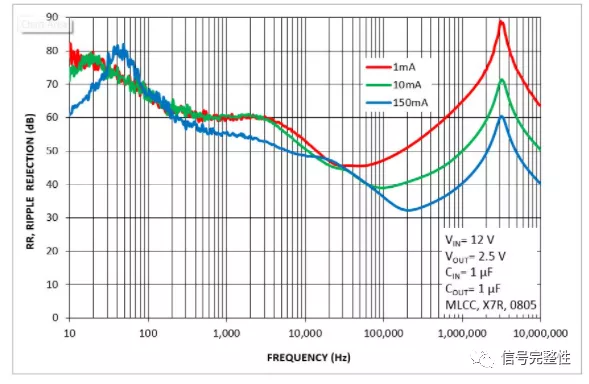

34 為了獲得最佳的整體效率,許多高性能模擬和射頻電路采用LDO穩(wěn)壓器對開關(guān)轉(zhuǎn)換器的輸出進行后級調(diào)節(jié)來供電。這需要在LDO穩(wěn)壓器在輸入至輸出電壓差很小時具有高PSRR和低輸出電壓噪聲。具有高PSRR

2018-11-19 15:08:06 7435

7435

ADI LDO具有低輸出雜訊、高PSRR、高準(zhǔn)確度、快速暫態(tài)響應(yīng)、低壓差、小型封裝尺寸等特性。本展示顯示了ADI超低雜訊LDO如何大幅降低信號鏈中的VCO相位雜訊。

2019-07-30 06:20:00 2919

2919 相位噪聲是時鐘、射頻頻綜最為關(guān)注的技術(shù)指標(biāo)之一。影響鎖相環(huán)相噪的因素有很多,比如電源、參考源相噪、VCO自身的相噪、環(huán)路濾波器的設(shè)置等。其中,電源引入的低頻噪聲往往對鎖相環(huán)的近端相噪有著很大

2020-04-02 17:36:08 11

11 現(xiàn)在很多集成VCO的頻率合成器的設(shè)計思想,都是利用輸出端加分頻器來擴展輸出范圍,如圖1所示。比如ADI的HMC832,其VCO的頻率為1500~3000MHz,利用其后的分頻器(1/2/4/6/…60/62),最終獲得25MHz~3000MHz的頻率覆蓋范圍。

2020-10-30 10:40:00 3

3 供電,這意味著它不受外界影響,因此在輸入端沒有外部噪聲(雖然LDO在輸出端確實有內(nèi)部噪聲)。外部噪聲是由外界影響(輸入處的紋波——實際源)產(chǎn)生的各種噪聲。輸入波紋與電源抑制比(PSRR)有關(guān)。此外,還有如熱和閃爍等噪聲的不同

2020-09-08 10:47:00 3

3 本文首先簡要地介紹了LDO的噪聲來源及環(huán)路穩(wěn)定性對輸出噪聲的影響;其次,根據(jù)調(diào)頻理論推導(dǎo)出VCO的相位噪聲與LDO 的噪聲頻譜密度的理論計算關(guān)系。在此基礎(chǔ)上,為了驗證LDO噪聲對射頻頻綜輸出相噪

2020-08-13 18:51:00 4

4 1.5A 負(fù) LDO 提供快速瞬態(tài)響應(yīng)、低輸出噪聲和精確電流限制

2021-03-20 15:39:16 9

9 寬帶VCO在堅固耐用的RoHS兼容模塊中結(jié)合了低相位噪聲和高輸出功率

2021-04-18 17:35:10 0

0 和 PSRR 低壓差線性穩(wěn)壓器 (LDO) 為調(diào)節(jié)由較高電壓輸入產(chǎn)生的輸出電壓提供了一種簡單方法。雖然操作簡單,但其自生噪聲在很多時候易與電源抑制比 (PSRR) 混淆。這兩者在很多情況下統(tǒng)稱為“噪聲”,這是不恰當(dāng)?shù)摹?b class="flag-6" style="color: red">噪聲是由LDO 內(nèi)部電路中的晶體管和電阻器以及外部元件產(chǎn)生

2021-05-13 15:35:18 5072

5072

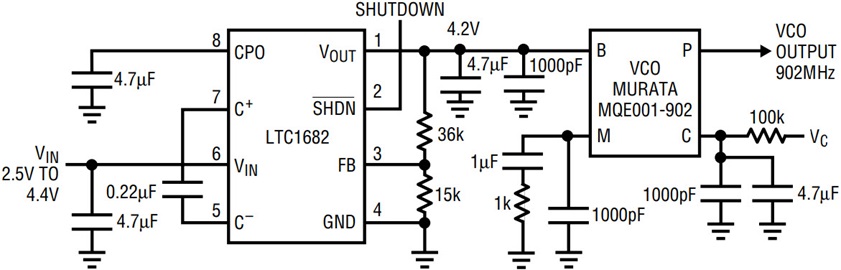

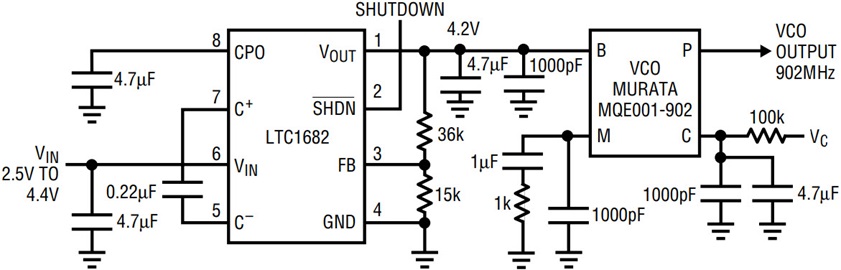

本電路利用低噪聲、低壓差(LDO)線性調(diào)節(jié)器為寬帶集成PLL和VCO供電。寬帶壓控振蕩器(VCO)可能對電源噪聲較為敏感,因此,為實現(xiàn)最佳性能,建議使用超低噪聲調(diào)節(jié)器。圖1所示電路使用完全集成的小數(shù)

2021-06-06 11:25:50 2

2 相位噪聲是時鐘、射頻頻綜最為關(guān)注的技術(shù)指標(biāo)之一。影響鎖相環(huán)相噪的因素有很多,比如電源、參考源相噪、VCO 自身的相噪、環(huán)路濾波器的設(shè)置等。

2022-08-05 10:30:27 3687

3687 曾經(jīng)有過這樣的困惑,頻譜儀怎么會有相噪的指標(biāo),相噪不是信號源的指標(biāo)嗎?后來才明白,頻譜儀的相噪其實是內(nèi)部LO信號的相噪,而且它決定了頻譜儀近端相噪的測試能力。頻譜儀自身的相噪越低,則相噪測試能力越強!

2022-12-13 15:35:18 2339

2339

許多便攜式RF產(chǎn)品使用壓控振蕩器(VCO)來產(chǎn)生RF載波頻率。這些應(yīng)用通常需要高于主電池電源的低噪聲VCO電源電壓。通常使用為低噪聲線性穩(wěn)壓器供電的 DC/DC 轉(zhuǎn)換器。不幸的是,此解決方案有幾個缺點。DC/DC轉(zhuǎn)換器往往會產(chǎn)生可能不會被穩(wěn)壓器抑制的噪聲,從而導(dǎo)致穩(wěn)壓器輸出噪聲遠(yuǎn)遠(yuǎn)大于熱噪聲水平。

2023-03-07 15:20:04 1388

1388

在一篇LDO基礎(chǔ)知識博文中,我討論了使用低壓差穩(wěn)壓器(LDO)過濾因開關(guān)模式電源導(dǎo)致的紋波電壓。然而,這不是獲得凈化直流電源唯一要考慮的事情。因為LDO是電子設(shè)備,它們自身也會生成一定數(shù)量的噪聲

2023-03-30 09:43:15 2737

2737

那么我們?nèi)绾螠y量噪聲呢?如前所述,內(nèi)部噪聲是由輸入端有理想源的 LDO 產(chǎn)生的噪聲。在實際測量中,這個理想的源可能是電池,它比 LDO 穩(wěn)壓器具有更低的內(nèi)部噪聲。

2023-06-06 09:52:38 2396

2396 相位噪聲是VCO的核心指標(biāo),衡量了輸出信號頻譜的純凈程度。研究相位噪聲的來源和形成機制,對VCO設(shè)計與優(yōu)化有著重要的意義。

2023-07-06 14:42:08 3575

3575

LDO噪聲源與降低噪聲方式

2023-07-25 08:56:49 3988

3988

相噪是與哪種類型的抖動相對應(yīng)?如何理解相位噪聲與時間抖動的關(guān)系? 相位噪聲與時間抖動是兩個在信號處理領(lǐng)域中經(jīng)常涉及的概念。在討論相位噪聲時,我們常常聽到相位噪聲和時間抖動的聯(lián)系。因此,本文將探討相位

2023-10-20 15:08:11 2180

2180 頻率的比例決定了鎖定的頻率倍數(shù),因此對于VCO的頻率穩(wěn)定性要求比較高。 2. 延遲:VCO的輸出延遲對于PLL系統(tǒng)的工作非常重要。如果VCO的輸出延遲太大,則可能會導(dǎo)致鎖定時間變長或者無法鎖定。 3. 噪聲:VCO的輸出噪聲會影響PLL系統(tǒng)的性能和穩(wěn)定性。因此,要求VCO的輸出噪聲較

2023-10-30 10:46:44 1533

1533 揭秘什么是LDO噪聲

2023-12-07 16:05:20 1401

1401

混頻器輸出相噪與以下因素相關(guān)

2023-11-25 09:15:51 1255

1255 電子發(fā)燒友網(wǎng)站提供《如何用簡單的RC網(wǎng)絡(luò)降低可調(diào)低壓差穩(wěn)壓器(LDO)的輸出噪聲.pdf》資料免費下載

2023-11-29 10:47:13 1

1 您可以使用頻譜分析工具來識別LDO輸出線路中的各種交流元件。(應(yīng)用,“如何測量LDO噪聲,”介紹了豐富的噪聲測量知識。) 圖 2 繪制了1A低噪聲LDO TPS7A91的輸出噪聲。

2024-01-18 15:50:48 1827

1827

電子發(fā)燒友網(wǎng)站提供《LDO噪聲揭秘.pdf》資料免費下載

2024-09-21 09:13:00 0

0 的頻率選擇。1.8 GHz 輸出的集成噪聲為 47 fs,使其成為理想的低噪聲源。該器件將一流的PLL和集成VCO噪聲與集成LDO相結(jié)合,無需在高性能系統(tǒng)中使用多個分立器件。

2025-09-13 10:22:25 1250

1250

。

。

電子發(fā)燒友App

電子發(fā)燒友App

評論