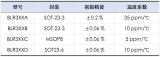

0 引 言

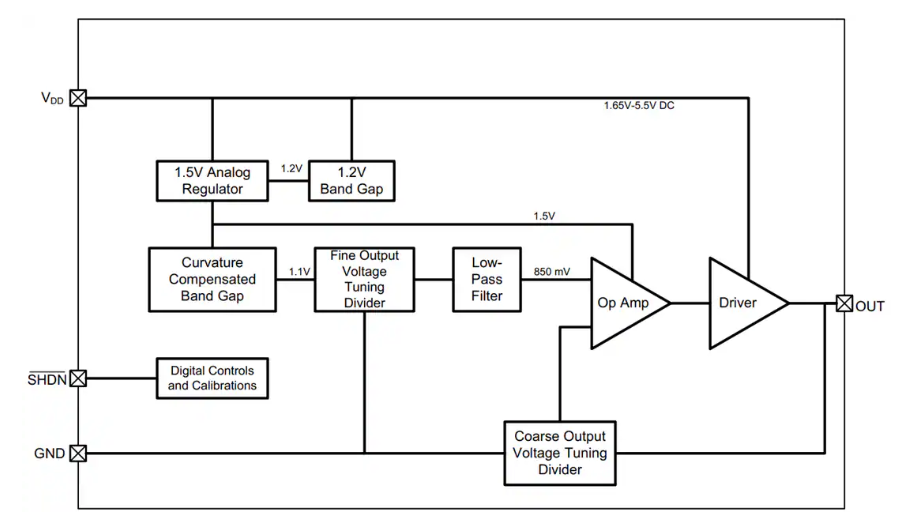

隨著集成電路的發(fā)展,一個(gè)高穩(wěn)定、高精度的基準(zhǔn)電壓源變得越來(lái)越重要。特別是在D/A,A/D轉(zhuǎn)換以及PLL電路中,溫度穩(wěn)定性和精度之間關(guān)系到整個(gè)電路的精確度和性能。

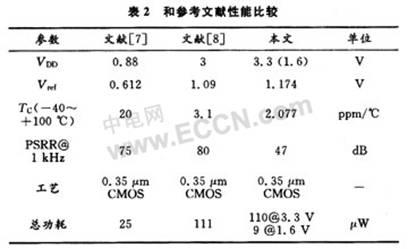

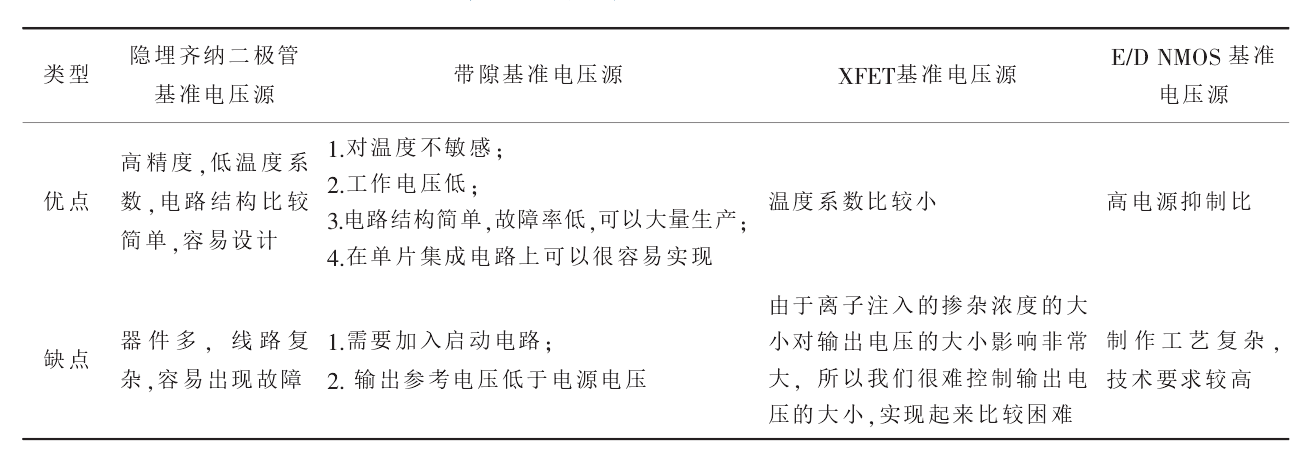

當(dāng)今設(shè)計(jì)的基準(zhǔn)電壓源大多數(shù)采用BJT帶隙基準(zhǔn)電壓源結(jié)構(gòu),以及利用MOS晶體管的亞閾特性產(chǎn)生基準(zhǔn)電壓源;然而,隨著深亞微米CMOS工藝的發(fā)展,尺寸按比例不斷縮小,對(duì)芯片面積的挑戰(zhàn)越來(lái)越嚴(yán)重,雙極型晶體管以及高精度電阻所占用的面積則成為一個(gè)非常嚴(yán)重的問(wèn)題。在此,提出一種通過(guò)兩個(gè)工作在飽和區(qū)的MOS管的柵源電壓差原理,產(chǎn)生一個(gè)與絕對(duì)溫度成正比(PTAT)的電流,利用這個(gè)電流與一個(gè)工作在飽和區(qū)的二極管連接的NMOS晶體管的閾值電壓進(jìn)行補(bǔ)償,實(shí)現(xiàn)了一個(gè)低溫漂、高精度的基準(zhǔn)電壓源的設(shè)計(jì)。

1 NMOS晶體管的構(gòu)成

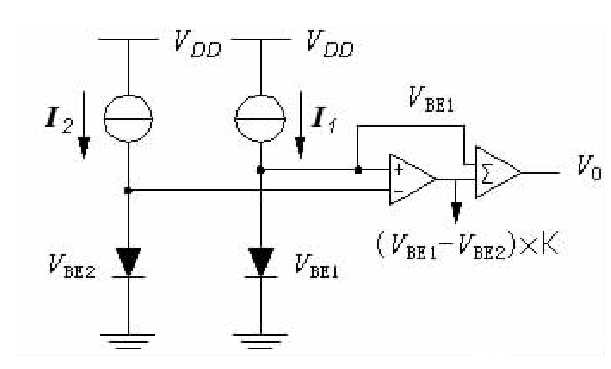

兩個(gè)工作在弱反型區(qū)的NMOS晶體管M1和M2的結(jié)構(gòu)如圖1所示。

其輸出電壓V0可以表示為:

式中:UT=kT/q;k為波爾茲曼常數(shù);△V表示實(shí)際中晶體管失配引入的誤差,是個(gè)常數(shù),這里忽略它的影響。由此得到:

式中: 是由溫度決定的倍增因子,后面將對(duì)其溫度特性進(jìn)行討論。

是由溫度決定的倍增因子,后面將對(duì)其溫度特性進(jìn)行討論。

對(duì)于NMOS晶體管M1和M2,其柵源電壓分別為Vgs1和Vgs2,那么圖3中電壓為:

如果利用前面提到的兩個(gè)工作在弱反型區(qū)的MOS管輸出電壓特性來(lái)控制兩個(gè)工作在飽和區(qū)的NMOS的柵極電壓Vgs1和Vgs2,使得:

式中:λ為比例常數(shù)。

將式(5)代入到式(3)可得:

對(duì)于參數(shù)KM1,它主要受晶體管遷移率λ的影響,通常被定義為:

式中:T為絕對(duì)溫度;α由工藝決定,典型值為1.5.將式(7)代人式(6)可得:

它為一個(gè)與溫度無(wú)關(guān)的常數(shù)。

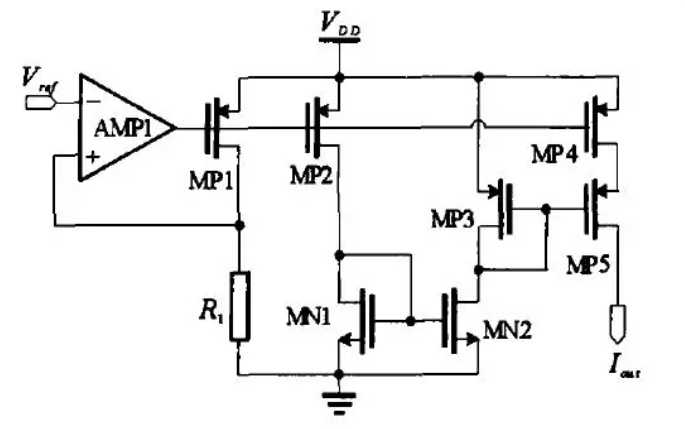

通過(guò)上面分析可知,此方法可以得到一個(gè)與絕對(duì)溫度成正比(PTAT)的電流I1.具體實(shí)現(xiàn)電路如圖3所示。

圖3電路中,M3~M6四個(gè)PMOS晶體管工作在飽和區(qū),它們的寬長(zhǎng)比相同。M1和M2兩個(gè)NMOS晶體管工作在飽和區(qū),它們的寬長(zhǎng)比為(W/L)2/(W/L)1=m.通過(guò)調(diào)節(jié)電路,使得M7~M10四個(gè)NMOS晶體管工作在深線(xiàn)性區(qū)。現(xiàn)在討論電路的工作原理。

對(duì)于X點(diǎn)和Y點(diǎn)的對(duì)地電壓,可以分別表示為:

通過(guò)式(5)和式(15)可以看出,在這個(gè)電路中,式(5)的系數(shù):

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論