Allegro中如何進行顏色設置

在ALLEGRO中,如何對網絡設置顏色?比如對POWER網絡,我想讓它顯示為紅顏色!怎么做?RichardLC網友回復:我想你

2008-03-22 16:40:44 11885

11885

通過上期的文章,是不是很多粉絲都開始憧憬:“本來差分線上下層需要兩層地,現在地都不用,只要一層差分線,原本要20層板,現在10層就搞掂!^_^”,差分信號表示:“我謝謝你啊!”

2022-07-13 09:16:26 2658

2658 兩條傳輸線,傳輸兩個相位相反的信號,就叫差分傳輸,也叫奇模傳輸,這兩條傳輸線構成的系統叫做差分線,它們的阻抗稱為差分阻抗。

2023-12-25 13:56:43 2716

2716

我在走差分線的時候出線一定要走一段平行線然后才能轉角度,在空間比較有限的地方很不方便,太占地方了。有些PCB的差分線在出線后馬上就可以轉角度,有什么地方可以設置嗎?

2016-06-29 20:45:47

自己總結下差分對規則的設置

2016-03-01 01:48:30

一般的,需要自己先提前計算好層疊,阻抗,計算好單端和差分的線寬,線距,計算之前,需要自己根據BGA間距,走線密度等,做一個預估,這樣,計算出來的更有針對性,也更容易一次成功。

2019-05-22 06:57:53

我畫的差分電路板有差分線,需要用蛇形線讓他們等長,可是我的蛇形線只能一根線一根線的畫,怎樣讓一對差分線同時畫出蛇形線?是不是哪里的設置需要更改?

2012-07-11 20:24:14

差分線能走GHz以上的頻率,差分線為什么能走高速?是否與抗干擾能力強有關?為何?

2015-11-08 14:10:40

的變化,一時讓很多硬件工程師頭疼不已。問題的分析:造成HDMI輻射超標的原因有多種可能,就不一一分析了,這里只重點談談與差分線傳輸線長度差有關的問題。理想情況下,差分信號是正負對稱的,其共模份量為零

2020-11-04 09:40:06

差分線對等長補償,請問這個走線里面ABC三個地方不等長,請問如何補償?是在abc三個地方分別補償還是在ab之間補償。B到C的距離超過了600mil。

2023-11-02 15:09:48

差分線對的PCB設計要點

2012-08-20 14:52:39

差分線抗干擾能力強,信噪比高,輻射小,帶寬容量大等眾多優點,所以在目前的高速電路設計中,都選取差分線作為通信方式。差分線使用兩根走線傳輸一路信號,兩根線上攜帶的信息是相同的,但是信號的相位差是180

2020-10-29 08:56:44

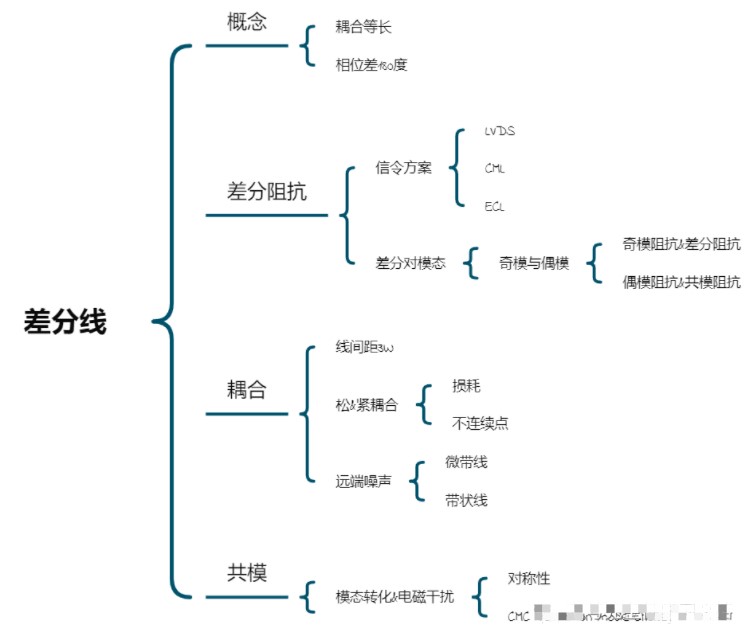

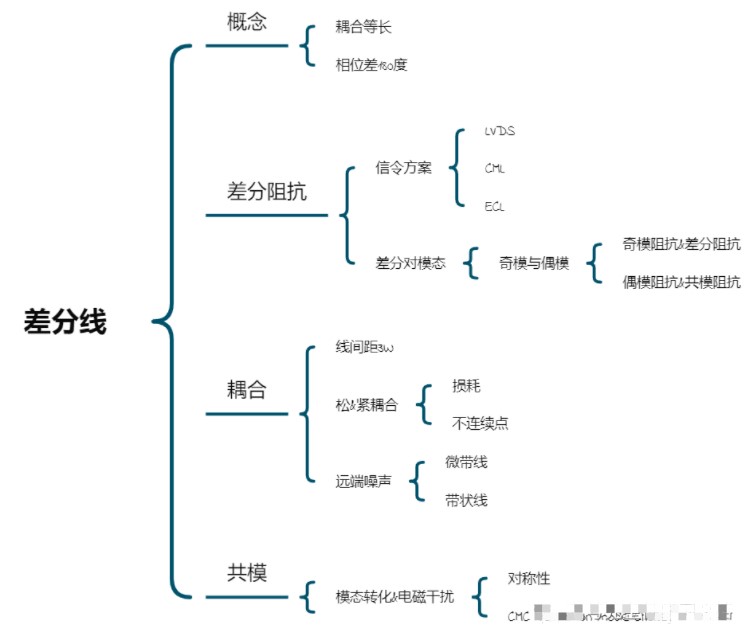

記得在剛學習差分線(對)的時候,總是對一些概念把握不準,很多概念都會混淆,比如差分(很多人還會誤解成差模)、共模、奇模與偶模,以及由此延伸出的差分阻抗、共模阻抗、奇模阻抗與偶模阻抗,光是這些概念

2019-08-07 08:44:05

,尤其是串擾以及損耗等問題。為了解決這些問題,一種全新的數據傳輸方式應運而生,如圖1所示,他就是-----差分(差分線、差分互聯)。

2019-07-23 07:52:10

差分線繞線方法比較

2017-12-05 14:25:56

差分線繞線方法比較差分線抗干擾能力強,信噪比高,輻射小,帶寬容量大等眾多優點,所以在目前的高速鏈路設計中,都選取差分線作為通信方式。 差分線使用兩根走線傳輸一路信號,兩根線上攜帶的信息是相同

2014-04-15 10:51:05

差分線要注意什么問題?

2015-06-29 00:31:58

差分線阻抗為什么要是85Ω呢?

2016-01-31 20:25:50

有一組線:里面有多對差分線對,有多根單端線,差分線對的走線規則已經設置了(線寬5MIL,線距5mil),請問如何設置差分線對與差分線對之間間距(比如我想要的線對之間間距10mil)?如何設置差分對與單端線之間的距離(比如我想要間距8mil)?

2019-11-19 14:17:31

PCB布線中,有著許多需要注意的點,比如:1.高頻時鐘線需要蛇形走線2.有些信號線需要設置差分對,差分走線

2019-05-31 06:23:05

`各位大佬,ORCAD PCB (16.3~16.6)在設計PCB時候,需要畫差分線和差分的等長要求,請教各位如何設置;謝謝!`

2018-04-14 09:54:03

Properties,如下圖所示。(3)在彈出的對話框中,可設置相應的線寬及線距,此處分別設置為8與6(8:8:6)。點擊OK,即完成差分對的定義。線寬及線距影響差分線的阻抗,其值可由Polar

2015-01-12 15:38:59

差分信號在高速電路設計中應用越來越廣泛,如USB、HDMI、PCI、DDR*等,承載差分信號的差分線主要優勢有:抗干擾能力強,能有效抑制EMI、時序定位精確等,對于PCB工程師來說,最關注的是如何確保在實際走線中能完全發揮差分線的這些優勢。

2019-05-20 09:32:55

RT,按F3 交互布線時 差分只出了一端,不知道是什么地方設置的問題,從網絡的另一端可以。正常的差分交互布線時兩個差分線應該能同時引出來,但是有個芯片就是不行,只能引出一根。別的板子上同樣的芯片是可以的,差分設計規則也設成了同樣的。求教還有其他的地方設置不合理會導致這種現象的出現么?

2013-11-19 22:43:05

按F3 交互布線時 差分只出了一端,不知道是什么地方設置的問題,從網絡的另一端可以。正常的差分交互布線時兩個差分線應該能同時引出來,但是有個芯片就是不行,只能引出一根。別的板子上同樣的芯片是可以的,差分設計規則也設成了同樣的。求教還有其他的地方設置不合理會導致這種現象的出現么?

2019-04-07 21:33:41

PCB設計中差分線怎么設置,還有就是等長分析

2019-08-19 09:47:36

請教大家,一下PCI-E和BGA之間的差分線因到BGA時長度不一致,需要走蛇形線.但蛇形線又走的太長,相當與整個長度的一半了,該怎樣走好一些呢?

2009-04-10 22:01:48

` 本帖最后由 cooldog123pp 于 2019-8-10 22:50 編輯

差分線,布線的時候經常會遇到,在AD里面,怎么進入布差分線的模式中呢。快捷鍵組合p+i,或者點擊菜單Place

2016-09-26 17:11:37

各位,為什么不同層差分線的間距不一樣啊?

2019-09-06 05:36:01

為什么我看到被人的樣板為什么高頻差分線不包地這是為什么

2015-01-07 09:45:00

介紹反向偏置差分線性傳感器的主要應用是測量軸和軸向位移等線性運動,本文以Allegro ATS344LSP 反向偏置差分線性傳感器 IC為例介紹了其傳感原理,其磁性配置的優點,并給出了典型的用戶

2020-07-30 09:41:49

什么是差分線差分線有什么用哪些地方用到差分線高速差分線設計的硬件要求

2021-02-25 06:26:18

老師,這個差分線走到一半怎樣單獨走線呢?

2019-09-19 22:58:05

差分對組距之間。差分組與差分組之間的間距。差分線與其它信號之間的間距如何設置

2019-09-10 22:57:20

請問這種交叉的差分線如何處理

2019-09-17 05:35:54

差分信號在高速電路設計中應用越來越廣泛,如USB、HDMI、PCI、DDR*等,承載差分信號的差分線主要優勢有:抗干擾能力強,能有效抑制EMI、時序定位精確等,對于PCB工程師來說,最關注的是如何確保在實際走線中能完全發揮差分線的這些優勢。

2019-05-24 06:32:02

記得以前設計過一塊多層板,電路上有一個屏,是用幾對差分線驅動的。調試硬件的時候,系統能正常跑起來,但是屏點不亮。后來經過排查,發現有一對差分線用錯了,這個方案有四路差分線模式和兩路差分線模式,本項

2022-02-18 09:48:47

圖中左邊是差分線,右邊也是差分線。求教這兩端差分線號S1和S2是什么關系?這個是電平轉換嗎?求教

2015-01-28 14:30:42

在AD中,差分線等長知道用TOOLS/Interactive Length Tuning操作,表現出來差分中一條線作蛇形線。請教下:1.如何讓兩條線都作蛇形線??2.不同組別的差分線要等長?這兩個要求有會的嗎?急!!

2015-07-10 12:32:41

①在元件布局(PCB Layout)時,應將USB2.O芯片放置在離地層最近的信號層,并盡量靠近USB插座,縮短差分線走線距離。②差分線上不應加磁珠或者電容等濾波措施,否則會嚴重影響差分線的阻抗。

2019-05-23 08:54:17

編譯差分線時出現錯誤怎么辦?錯誤:number of nets in differential parts EXT_CS_DPN is 1 instead of 2

2015-04-30 09:50:28

請教各位大神, allegro 差分對與差分對之間的間距如何設置?謝謝! 版本16.6。我在網上看到可以在class to class中設置,嘗試后發現需要為每一對差分對設置一個NetClass屬性

2017-02-24 14:21:34

請教大家一個問題。 芯片采用的差分線傳輸數字數據,芯片輸出一共有10對LVDS差分走線,兩對時鐘,8對數據線。截圖是芯片手冊中提到的內容。 問題1:它是說明每一對之間相差長度嗎?我舉例解釋一下

2019-01-04 10:00:40

差分線拐這么多次對信號影響大嗎????

2019-06-12 21:19:07

差分線組內等長 命令是哪個?

2019-07-26 05:35:14

我的圖中是一對差分線,不過走線過程中得放置過孔,使用了快捷鍵shift+ctrl+滾輪放置過孔換層,測的兩個過孔之間間距30多mil,請問放置這兩個過孔時的間距可以設置嗎,再不改變過孔大小的情況下。

2019-09-25 02:48:42

求助dxp2004中如何布50歐姆的差分線,還有一些布線規則都怎么設置

2020-03-13 04:22:20

封裝上12號和1號引腳離得比較遠 ,這樣怎么畫差分線啊?

2019-04-24 06:22:15

走差分線可以設置等長嗎

2019-07-31 05:35:12

差分線對的工作原理是使接收到的信號等于兩個互補并且彼此互為參考的信號之間的差值,因此可以極大地降低信號的電氣噪聲效應。而單端信號的工作原理是接收信號等于信號與電源或地之間的差值 ,因此信號或電源

2018-09-04 16:31:34

allegro16.2過孔設置方法.圖解教程。

2010-03-18 15:06:38 0

0 allegro規則設置里常見縮寫詞的含義,Dsn Design整個設計

2011-11-22 10:51:53 6126

6126 allegro pcb editor在規則設置之前,必須了解allegro pcb editor規則設置類別優先順序,

2011-11-22 10:53:16 6388

6388

本內容介紹了Allegro中尺寸標注文字的設置,這里我們介紹文字參數的設置。

2012-06-26 15:03:51 7033

7033

Allegro中尺寸標注有很強大的功能,包括線性標注,角度標注,引線標注等。下面介紹一下Allegro中尺寸標注參數的設置

2012-06-26 15:09:10 19423

19423

詳細介紹了ALLEGRO16.6 約束規則設置方法,適合初學者

2015-11-20 15:45:08 0

0 allegro_差分線等長設置,有需要的下來看看

2016-02-22 16:15:35 62

62 allegro16.2過孔設置方法,有需要的下來看看。

2016-02-22 16:21:27 12

12 的布線方式,重點說明了差分線對的布線準則、設置方法以及其需要注意的問題。采用Cadence公司的Allegro軟件,以子卡上的SFP+接口信號為例,闡明了差分信號在PCB中的實現。

2017-11-13 17:18:21 11

11 本文檔的主要內容詳細介紹的是AD中關于差分線的設置和走線的方法詳細資料說明。

2019-02-11 08:00:00 0

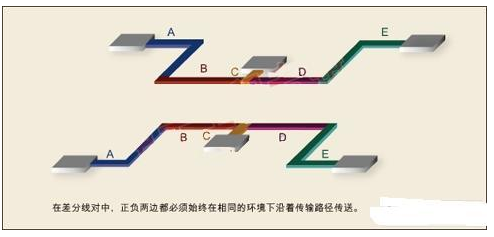

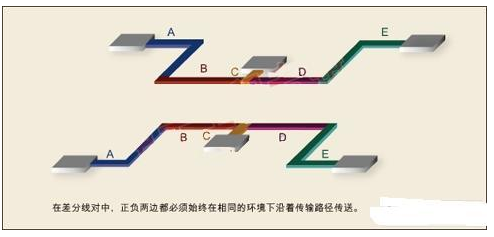

0 在差分線對中,正負兩邊都必須始終在相同的環境下沿著傳輸路徑傳送。正負兩邊必須緊靠在一起,以使正負信號經由這些信號上相應點的電磁場而彼此耦合。差分線對是對稱的,因此它們的環境也必須對稱。

2019-09-29 14:35:32 14773

14773

,不過已經改名叫 Altium Designer System(ADS)了,仔細看看說明,說已經支持差分線布線了,經過一番折騰,終于弄出來了,現和大家分享一下: 要讓 Protel(或者說 Altium Designer )在交互布線時走差分線,需要經過以下幾個步驟:

2019-12-02 08:00:00 0

0 DDR4布線之allegro約束規則設置綜述

2021-09-08 10:34:29 0

0 三招教你理清差模與共模干擾

2022-01-10 14:30:59 16

16 差分線本身沒有什么特別,決定它們特性的是這兩條傳輸線上的信號傳輸方式。差分線除了傳輸差分信號,還有共模信號,前一種是大小相等方向相反的驅動電壓,后一種是相等方向相同的驅動電壓。

2022-08-16 09:46:56 4768

4768

揭曉最差密碼排行榜 教你設置安全密碼的小技巧

2022-10-20 10:27:32 0

0 的長度。 圖 1 差分走線出現網格走線 當出現這種錯誤時,首先打開規則管理器查看規則所設置的未耦合長度為多少,如圖2所示。因為在走差分時首尾兩端或者在差分線進行打孔換層時是有一段差分線允許不滿足耦合間距的,但這個長度不能過長,推薦設置為50mil,如

2022-12-10 07:45:05 2854

2854 整個基礎知識體系中,差分線(對)是很難搞的部分,卻是最常用的部分。說到差分線基礎知識,里面的概念很多,記得剛接觸的時候,奇模&共模有時候會搞不清楚。話不多說,直接上圖。

2023-03-22 09:18:24 3914

3914 在PCB設計過程中,差分信號是比較重要的信號,一般設置差分信號到其它信號的間距是20mil,但是設置完差分信號到其它信號的間距之后,差分對內PN之間不滿足20mil的間距,會報錯,如1所示:圖1差

2022-05-31 11:09:33 11347

11347

分類的創建和差分規則設置:PCB上存在一對USB差分線,首先需要創建差分類,然后針對這對差分線來設置差分規則。

2023-08-01 10:06:21 4098

4098

ALLEGRO約束規則設置步驟(以DDR為例)

2022-12-30 09:19:29 12

12 為什么要走差分線?哪些地方需要用到差分走線?差分線與等長線的關系? 差分線是一種常見的高速布線技術,用于傳輸高頻信號。差分信號傳輸是指通過兩條物理線傳輸信號,其中一條線是信號的正向傳輸線,另一

2023-12-07 11:15:42 4385

4385 差分線pcb走線原則? 差分線是PCB設計中非常重要的一個部分,它的設計和走線原則可以直接影響到電路性能的穩定性和可靠性。在以下文章中,我將詳盡、詳實、細致地探討差分線的設計原則及其在PCB走線中

2023-12-07 18:09:37 7616

7616 隨著信息技術的飛速發展,高速信號傳輸已成為現代通信和數據處理中不可或缺的一環。在高速信號傳輸中,差分線技術因其獨特的優勢而得到廣泛應用。本文將從差分線的基本原理、抗干擾能力、帶寬容量、信號完整性以及應用實例等方面,深入探討高速信號差分線的技術優勢。

2024-05-16 16:31:14 1903

1903 電子發燒友網站提供《高速差分線路接收器數據表.pdf》資料免費下載

2024-06-26 10:52:54 0

0

?

? 電子發燒友App

電子發燒友App

評論