在《數字電路之如雷貫耳的“邏輯電路”》、《數字電路之數字集成電路IC》之后,本文是數字電路入門3,將帶來「時序電路」的講解,及其核心部件觸發器的工作原理。什么是時序電路?

2016-08-01 10:58:48 19579

19579

時序電路 首先來看兩個問題: 1.為什么CPU要用時序電路,時序電路與普通邏輯電路有什么區別。 2.觸發器、鎖存器以及時鐘脈沖對時序電路的作用是什么,它們是如何工作的。 帶著這兩個問題,我們從頭了解

2020-11-20 14:27:09 5120

5120

觸發器是由各種基礎門電路單元組成,廣泛應用于數字電路和計算機中。它具有兩個穩定狀態的信息存儲器件,是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。 觸發器具有兩個穩定狀態

2023-01-11 17:17:07 13779

13779

觸發器是一種特殊的電路元件或信號,它可以根據預先設定的條件或事件來產生相應的輸出信號或動作。觸發器是數字電路中的基本元件,用于控制信號的時序、邏輯運算和狀態轉換。

2024-01-15 16:33:15 7830

7830

用Qn(t)表示現態函數,用Qn+1(t)表示次態函數。它們統稱為狀態函數,一個時序電路的主要特征是由狀態函數給出的。三:時序電路的特征時序電路中記憶功能是靠觸發器來實現的,我們設計和分析時序電路

2018-08-23 10:36:20

時序電路測試及應用一、實驗目的1.掌握常用時序電路分析,設計及測試方法。2.訓練獨立進行實驗的技能.二、實驗儀器及材料1.雙蹤示波器 2.

2009-08-20 18:55:27

邏輯功能,若電路存在問題,并提出改進方法。在分析同步時序電路時分為以下幾個步驟:分清時序電路的組成.列出方程. 根據時序電路的組合部分,寫出該時電路的輸出函數表達式.并確定觸發器輸入信號的邏輯表達式

2018-08-23 10:28:59

CPLD與FPGA對比分析哪個好?

2021-06-21 06:10:12

CPLD與FPGA的對比分析哪個好?

2021-11-05 08:20:40

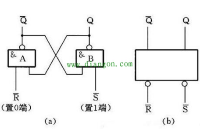

的,因此可以設計成儲存電路用來保存信息。常用的存儲電路有兩類:一類采用電平觸發,我們稱為鎖存器(Latch);另一類通過邊沿信號觸發,也就是觸發器(Flip-flop)。中文譯法經常有一種不明覺厲的感覺

2021-07-04 08:00:00

LTE與WiMAX對比分析哪個好?

2021-05-31 06:22:29

什么是時序電路?時序電路核心部件觸發器的工作原理

2021-03-04 06:32:49

什么是時序電路?SRAM是觸發器構成的嗎?

2021-03-17 06:11:32

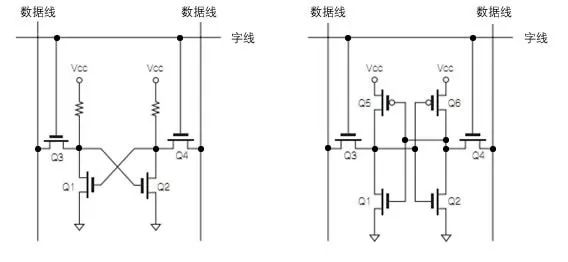

邏輯可構成時序邏輯電路,簡稱時序電路。現在討論實現存儲功能的兩種邏輯單元電路,即鎖存器和觸發器。雙穩態:電子電路中。其雙穩態電路的特點是:在沒有外來觸發信號的作用下,電路始終處于原來的穩定狀態。在外

2016-05-21 06:50:08

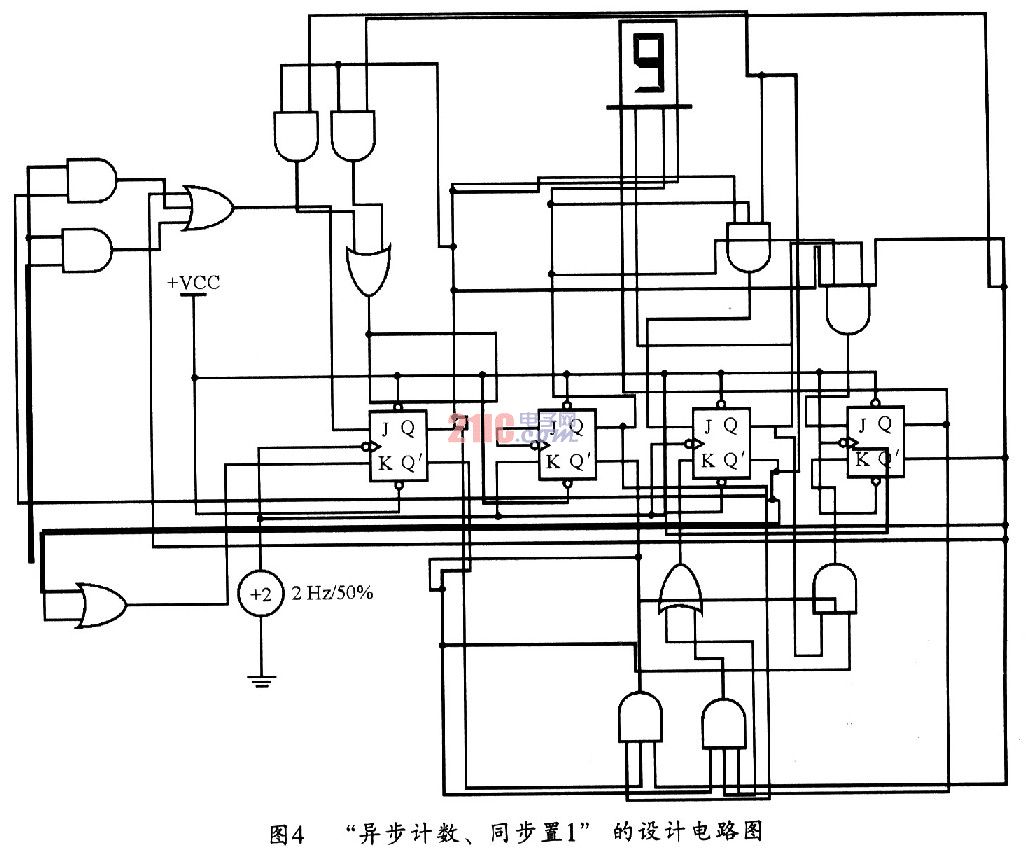

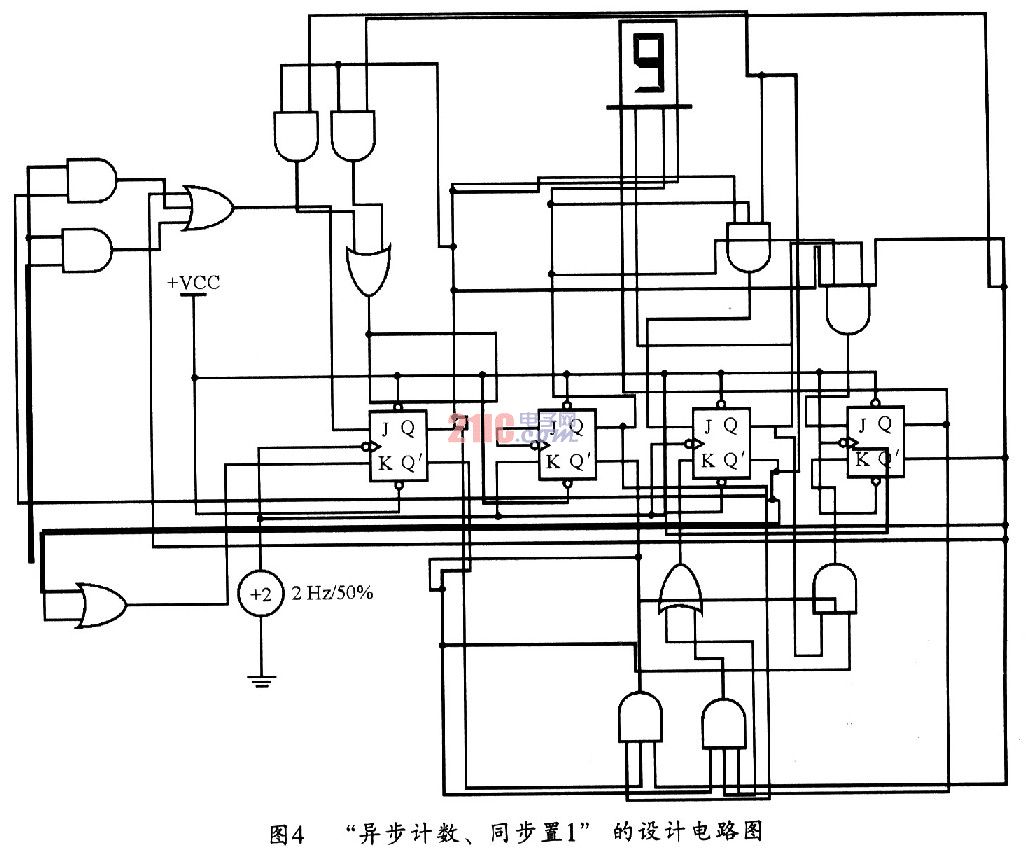

同步時序邏輯電路的設計(仿真實驗 2學時)一、 實驗目的;1. 掌握時序電路的設計和測試方法。2. 驗證二進制計數器的工作原理:學會用集成觸發器

2009-10-11 09:09:51

觸發器沒有使用相同的時鐘信號,需要分析哪些觸發器時鐘有效哪些無效分析步驟和同步時序電路一樣,不過要加上時鐘信號有關D觸發器的例題抄自慕課上的一個題目,注意第二個觸發器反相輸出端同時連接到復位端JK

2021-09-06 08:20:26

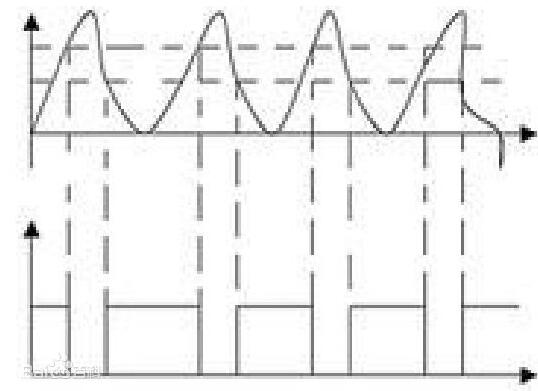

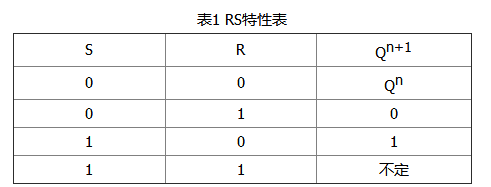

狀態,因此,與標準環形計數器相比,約翰遜計數器僅需要一半數量的觸發器便可實現同樣的MOD。 典型時序電路的缺陷 如圖1所示,這種電路最大的缺點是不可配置,因此,不能改變時鐘分頻因子。一個N觸發器

2018-09-30 16:00:50

實驗二 基本時序電路設計(1)實驗目的:熟悉QuartusⅡ的VHDL文本設計過程,學習簡單時序電路的設計、仿真和硬件測試。(2)實驗內容:Ⅰ.用VHDL設計一個帶異步復位的D觸發器,并利用

2009-10-11 09:21:16

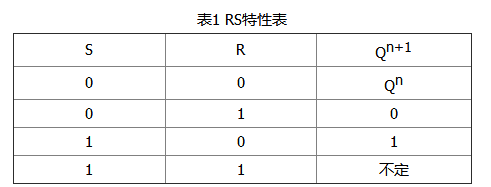

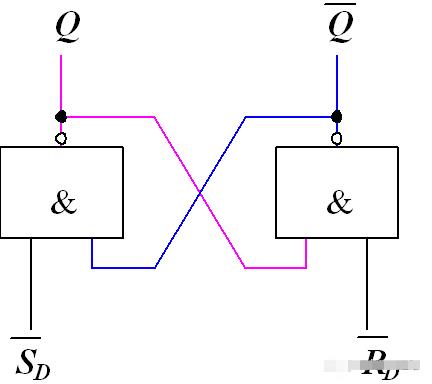

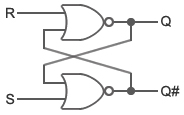

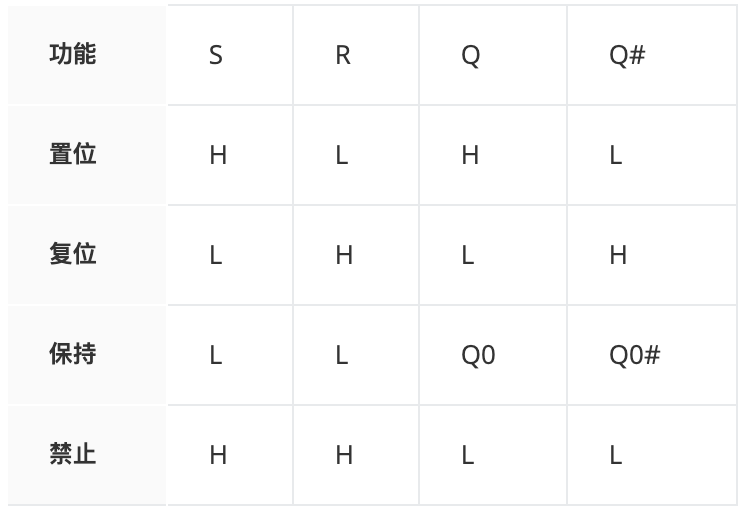

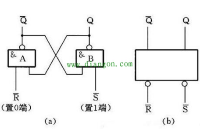

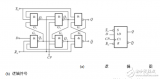

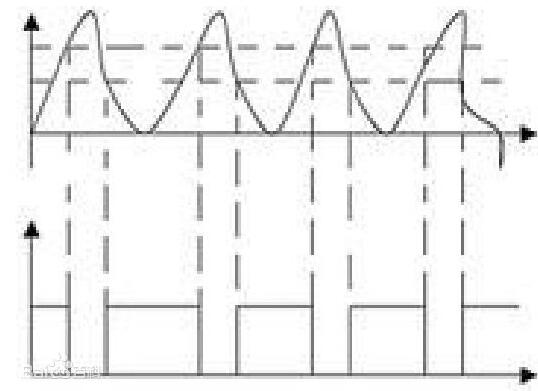

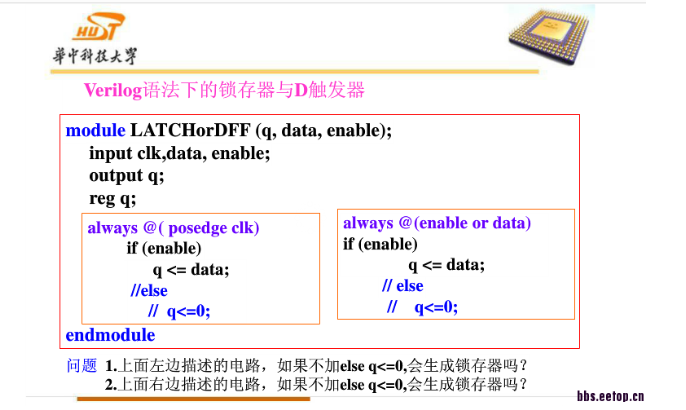

新課第五章 觸發器5.1 概述1、觸發器具有“記憶”功能,它是構成時序邏輯電路的基本單元。本章首先介紹基本RS觸發器的組成原理、特點和邏輯功能。然后引出能夠防止“空翻”現象的主從觸發器和邊沿觸發器。同時,較詳細地討論RS觸發器、JK觸發器、D觸發器、T觸發器、T'觸發器的邏輯功能及其描述方法。

2009-04-02 11:58:41

《計算機系統基礎》30’一、處理器的時序電路1、CPU中的時序電路答:CPU中的時序電路:通過RS觸發器控制CPU的時序。2、單周期處理器的設計答:CPU在處理指令時,一般需要經過以下幾個步驟:1

2021-07-22 09:46:12

觸發器是構成時序邏輯電路的基本單元電路。

觸發器具有記憶功能,能存儲一位二進制數碼。

2025-03-26 14:21:19

計數器及時序電路一、實驗目的1、了解時序電路的經典設計方法(D觸發器、JK觸發器和一般邏輯門組成的時序邏輯電路)。 2、了解同步計數器,異步計數器的使用方法。 3

2009-10-11 09:13:20

計數器及時序電路原理及實驗 一、實驗目的1、了解時序電路的經典設計方法(D觸發器、JK觸發器和一般邏輯門組成的時序邏輯電路)。 &

2009-10-10 11:47:02

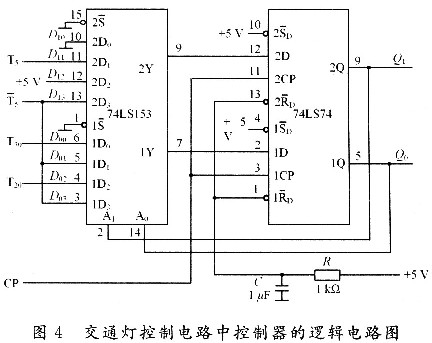

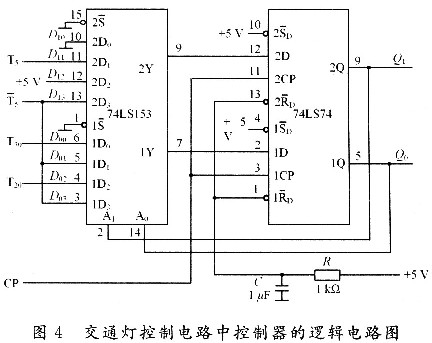

多輸入時序電路的基本原理是什么?基于數據選擇器和D觸發器的多輸入時序邏輯電路設計

2021-04-29 07:04:38

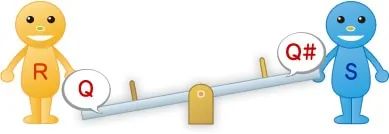

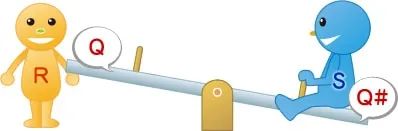

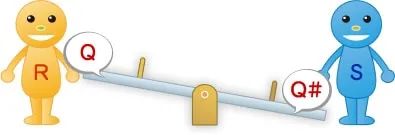

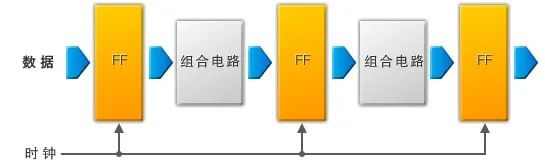

中,除了組合電路以外,還有一種時序電路,它的輸出不僅與當前時刻的輸入狀態有關,而且與電路原來狀態有關。而觸發器是組成時序電路中存儲部分的基本單元,具有保持、記憶、存儲功能。它有兩個輸出端Q和Q,當Q

2008-12-11 23:38:01

PLD練習2(時序電路)

2006-05-26 00:14:19 20

20 摘要:針對同步時序電路的初始化問題,提出了一種新的實現方法。當時序電路中有未確定狀態的觸發器時,就不能順利完成該電路的測試生成,因此初始化是時序電路測試生成中

2010-05-13 09:36:52 6

6 本文介紹將量子進化算法應用在時序電路測試生成的研究結果。結合時序電路的特點,本文將量子計算中的量子位和疊加態的概念引入傳統的測試生成算法中,建立了時序電路的量

2010-08-03 15:29:01 0

0 5.1 基本RS觸發器5.2 時鐘控制的觸發器5.3 集成觸發器5.4 觸發器的邏輯符號及時序圖

2010-08-10 11:53:23 0

0 觸發器是時序邏輯電路中完成記憶功能的電路,是最基本的時序邏輯電路。

2010-08-12 16:20:24 0

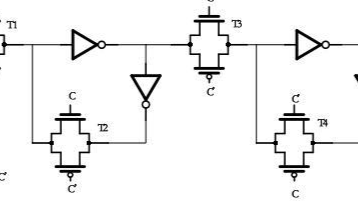

0 摘要: 研究采用三相交流電源的絕熱時序電路。首先介紹了采用三相交流電源的雙傳輸門絕熱電路并分析其工作原理, 在此基礎上提出了性能良好的低功耗絕熱D、T 與JK 觸發器。使用

2010-08-16 14:37:56 20

20 一、基本要求1、理解R-S觸發器、J-K觸發器和D觸發器的邏輯功能;2、掌握觸發器構成的時序電路的分析,并了解其設計方法;3、理解計數器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

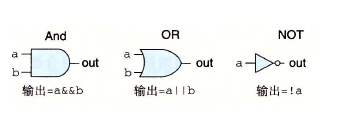

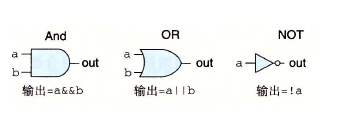

57 組合電路和時序電路是數字電路的兩大類。門電路是組合電路的基本單元;觸發器是時序電路的基本單元。

2010-08-29 11:29:04 67

67 觸發器是時序邏輯電路的基本構成單元,按功能不同可分為 RS 觸發器、 JK 觸發器、 D 觸發器及 T 觸發器四種,其功能的描述可以使用功能真值表、激勵表、狀態圖及特性方程。

2010-09-30 16:03:26 90

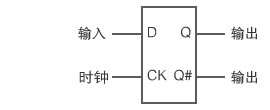

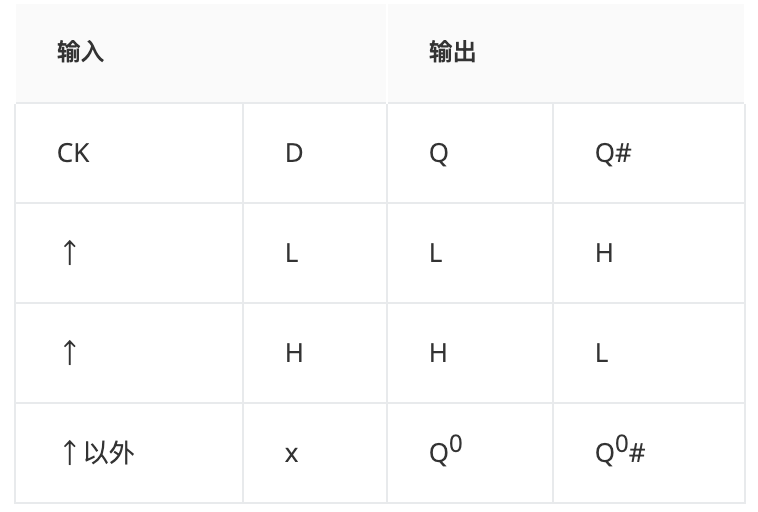

90 D觸發器真值表分析:

1. D 觸發器真值表

Dn

2007-09-11 23:15:20 20330

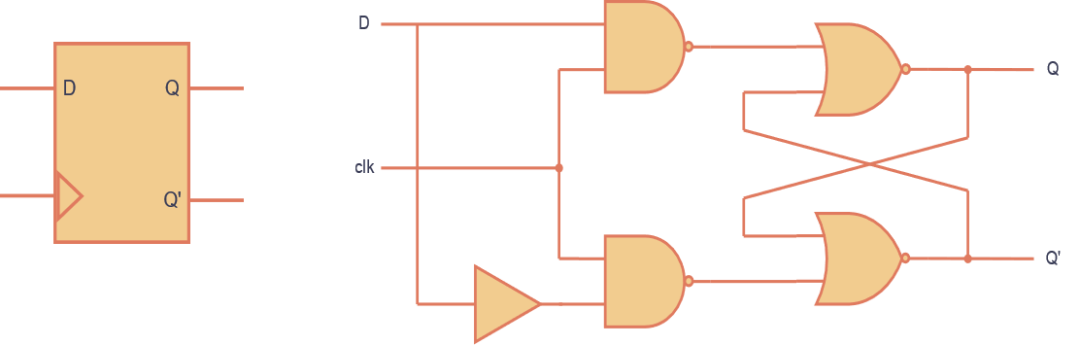

20330 D觸發器

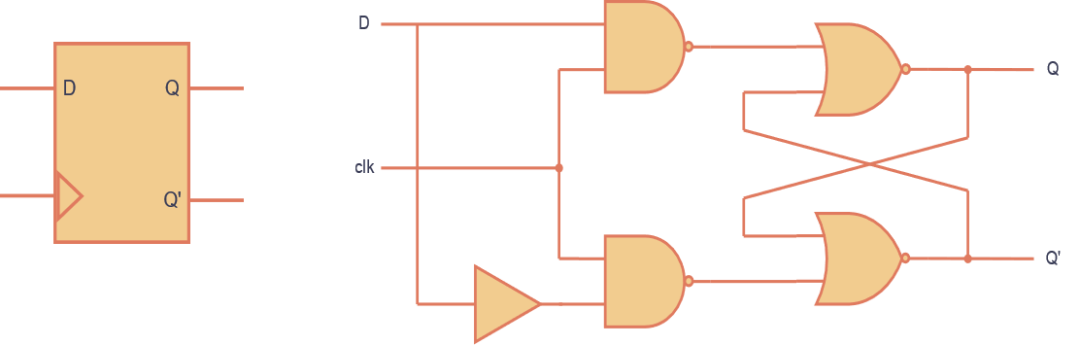

同步式D觸發器邏輯電路圖

D觸發器功能

2008-10-20 09:57:54 2818

2818

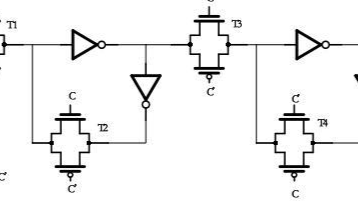

CMOS觸發器的結構與工作原理

CMOS D觸發器足主-從結構形式的一種邊沿觸發器,CMOS T型觸發器、JK觸發器、計數單元、移位單元和各種時序電路都由其組成,因此儀

2009-10-17 08:52:27 7947

7947

同步時序電路

4.2.1 同步時序電路的結構和代數法描述

2010-01-12 13:31:55 5769

5769

觸發器的分類, 觸發器的電路

雙穩態器件有兩類:一類是觸發器,一類是鎖存器。鎖存器是觸發器的原始形式。基本

2010-03-09 09:59:59 1866

1866 什么是時序電路

任意時刻的穩定輸出,不僅與該時刻的輸入有關,而且還

2010-01-12 13:23:14 8908

8908

觸發器是數字電路的基本邏輯單元之一,也是構成各種時序電路的最基本邏輯單元。

文中給出了基于JK觸發器來設計十二歸一計數器的設計和實現方法,并通過EWB軟件進行了

2010-06-30 15:58:29 18642

18642

在SSI時序邏輯電路設計中,遵循的設計準則是:在保證所設計的時序邏輯電路具有正確功能的前提下,觸發器的激勵函數應最小化,從而簡化電路結構。用卡諾圖法或公式法

2010-08-13 09:22:23 3848

3848

圖中所示是用CMOS電路D觸發器組成T型觸發器和J-K觸發器線路。圖示線路將D觸發器的Q端與D端相連,就可組成T

2010-09-20 03:31:35 21923

21923

圖中所示是用J-K觸發器組成的D觸發器電路。

從J-K觸發器的邏輯圖已知在D觸發器端增

2010-09-24 00:21:27 8886

8886

0 引言 觸發器是具有存儲功能的器件,在數字電子技術中用于構成各種時序邏輯電路。觸發器有多

2010-10-11 10:20:17 15534

15534 數字電路--觸發器雙穩態觸發器

2016-12-20 17:32:40 0

0 1、了解時序電路的經典設計方法(D觸發器、JK觸發器和一般邏輯門組成的時序邏輯電路)。

2、了解同步計數器,異步計數器的使用方法。

3、了解同步計數器通過清零阻塞法和預顯數法得到循環任意進制

2022-07-10 14:37:37 17

17 觸發器是一個具有記憶功能的,具有兩個穩定狀態的信息存儲器件,是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。在數字系統和計算機中有著廣泛的應用。觸發器具有兩個穩定狀態,即“0”和“1”,在一定的外界信號作用下,可以從一個穩定狀態翻轉到另一個穩定狀態。

2017-08-19 09:21:00 17041

17041

觸發器是一個具有記憶功能的,具有兩個穩定狀態的信息存儲器件,是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。在數字系統和計算機中有著廣泛的應用。觸發器具有兩個穩定狀態.

2017-11-02 08:53:42 61659

61659 觸發器是一個具有記憶功能的二進制信息存儲器件,是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。在數字系統和計算機中有著廣泛的應用。觸發器具有兩個穩定狀態,即“0”和“1”,,在一定的外界信號作用下,可以從一個穩定狀態翻轉到另一個穩定狀態。

2017-11-02 10:20:40 115082

115082

觸發器是一個具有記憶功能的,具有兩個穩定狀態的信息存儲器件,是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。在數字系統和計算機中有著廣泛的應用。觸發器具有兩個穩定狀態,即“0”和“1”。

2017-12-12 16:47:56 8214

8214

觸發器是一個具有記憶功能的,具有兩個穩定狀態的信息存儲器件,是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。在數字系統和計算機中有著廣泛的應用。觸發器具有兩個穩定狀態

2017-12-12 17:20:40 86395

86395

觸發器具有兩個穩定狀態,用以表示邏輯狀態“1”和“0”,在一定的外界信號作用下,可以從一個穩定狀態翻轉到另一個穩定狀態,它是一個具有記憶功能的二進制信息存貯器件,是構成各種時序電路的最基本邏輯單元。

2018-01-31 11:31:16 15403

15403

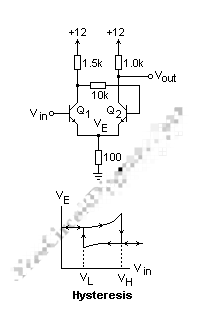

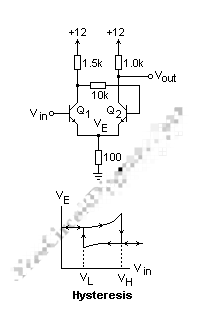

本文開始介紹了施密特觸發器的定義與作用,其次分析了施密特觸發器原理與它的典型應用,最后介紹了施密特觸發器的芯片及典型電路。

2018-02-08 13:41:25 50907

50907

本文開始介紹了什么是單穩態觸發器以及單穩態觸發器的電路組成,其次闡述了單穩態觸發器特點、門電路構成的單穩態觸發器、D觸發器構成的單穩態觸發器,最后詳細的闡述了時基電路構成的單穩態觸發器。

2018-03-27 09:24:23 78858

78858

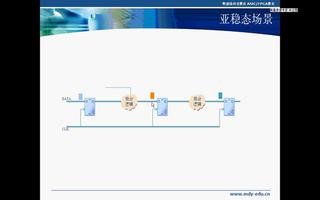

“時鐘是時序電路的控制者” 這句話太經典了,可以說是FPGA設計的圣言。FPGA的設計主要是以時序電路為主,因為組合邏輯電路再怎么復雜也變不出太多花樣,理解起來也不沒太多困難。但是時序電路就不同了

2018-07-21 10:55:37 5151

5151 組合電路和時序電路是計算機原理的基礎課,組合電路描述的是單一的函數功能,函數輸出只與當前的函數輸入相關;時序電路則引入了時間維度,時序電路在通電的情況下,能夠保持狀態,電路的輸出不僅與當前的輸入有關,而且與前一時刻的電路狀態相關,如我們個人PC中的內存和CPU中的寄存器,均為時序電路。

2018-09-25 09:50:00 25946

25946 ,得到原始狀態圖. 2.化簡原始狀態. 在制作原始狀態圖時,難免會出現多余狀態(觸發器的個數增多激勵電路過于復雜等),因此要進行狀態化簡,化簡時應根據具體情況來考慮. 3.分配化簡后的狀態. 把化簡后的狀態用二進制代碼來表示稱為狀態編碼.時序電路中,電路

2018-10-31 18:14:01 1681

1681 將驅動方程代入相應觸發器的特性方程中,便得到該觸發器的次態方程。時序邏輯電路的狀態方程由各觸發器次態的邏輯表達式組成。

2019-02-28 14:06:14 25600

25600 D觸發器是一個具有記憶功能的,具有兩個穩定狀態的信息存儲器件,是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。

2019-12-02 07:06:00 8199

8199

異步時序電路是指電路中除以使用帶時鐘的觸發器外,還可以使用不帶時鐘的觸發器和延遲元件作為存儲元件;電路中沒有統一的時鐘;電路狀態的改變由外部輸入的變化直接引起。

2019-11-29 07:07:00 1637

1637 異步時序電路是指電路中除以使用帶時鐘的觸發器外,還可以使用不帶時鐘的觸發器和延遲元件作為存儲元件;電路中沒有統一的時鐘;電路狀態的改變由外部輸入的變化直接引起.

2019-11-27 07:04:00 2273

2273 數字時序電路中通常用到的觸發器有三種:電平觸發器、脈沖觸發器和邊沿觸發器。

2019-07-05 14:38:54 17269

17269

本文檔的主要內容詳細介紹的是數碼管與分析儀的時序電路原理圖免費下載。

2019-12-13 15:17:11 9

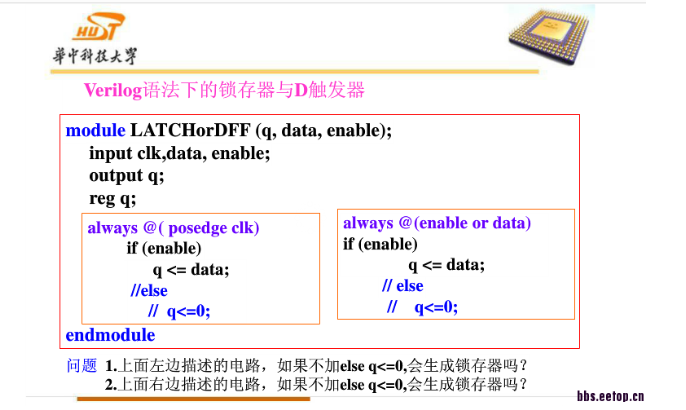

9 時序電路,生成觸發器,觸發器是有使能端的,使能端無效時數據不變,這是觸發器的特性。

2020-06-26 09:19:00 5422

5422

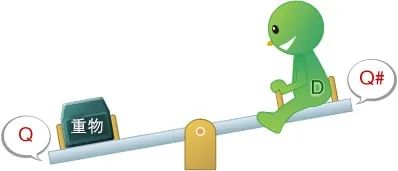

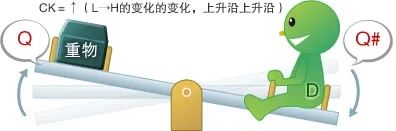

時間的重要性不言而喻,加上時間這個維度就如同X-Y的平面加上了一個Z軸,如同打開了一個新的世界。所以今天我們就要來聊聊時序電路。 在時序電路中,電路任何時刻的穩定狀態輸出不僅取決于當前的輸入,還與前

2021-01-06 17:07:22 5770

5770 電子發燒友網為你提供什么是時序電路?觸發器又是怎么回事資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-02 08:41:19 5

5 電子發燒友網為你提供“時序電路”及其核心部件觸發器的工作原理資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-04 08:51:02 13

13 明德揚有完整的時序約束課程與理論,接下來我們會一章一章以圖文結合的形式與大家分享時序約束的知識。要掌握FPGA時序約束,了解D觸發器以及FPGA運行原理是必備的前提。今天第一章,我們就從D觸發器開始講起。

2022-07-11 11:33:10 6143

6143

組合邏輯和時序邏輯電路是數字系統設計的奠基石,其中組合電路包括多路復用器、解復用器、編碼器、解碼器等,而時序電路包括鎖存器、觸發器、計數器、寄存器等。 在本文中,小編簡單介紹關于時序電路的類型和特點等相關內容。

2022-09-12 16:44:00 10673

10673

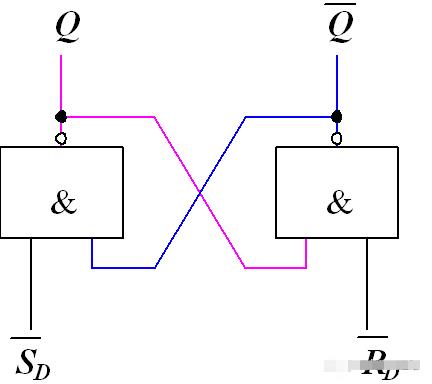

rs觸發器電路圖與rs觸發器內部電路圖 rs觸發器電路圖 主從RS觸發器電路圖: 主從觸發器由兩級觸發器構成,其中一級接收輸入信號,其狀態直接由輸入信號決定,稱為主觸發器,還有一級的輸入與主觸發器

2022-10-19 19:16:03 34612

34612

D 觸發器或數據觸發器是一種觸發器,它只有一個數據輸入“D”和一個時鐘脈沖輸入, 這種觸發器也稱為延遲觸發器,經常用于許多時序電路,如寄存器、計數器等。下面一起來了解一下D觸發器不同應用下的電路圖。

2023-01-06 14:19:46 9744

9744 觸發器是構成時序邏輯電路的基本單元。它是一種具有記憶功能,能儲存1位二進制信息的邏輯電路。在之前的文章中已經介紹過觸發器了,這里再介紹一下其他類型的觸發器。

2023-03-23 15:13:26 19700

19700

那么,如何才能將過去的輸入狀態反映到現在的輸出上呢?「時序電路」到底需要些什么呢?人類總是根據過去的經驗,決定現在的行動,這時我們需要的就是—記憶。同樣,「時序電路」也需要這樣的功能。這種能夠實現人類記憶功能的元器件就是觸發器。

2023-03-24 10:48:58 1943

1943

同步和異步時序電路都是使用反饋來產生下一代輸出的時序電路。根據這種反饋的類型,可以區分這兩種電路。時序電路的輸出取決于當前和過去的輸入。時序電路分為同步時序電路和異步時序電路是根據它們的觸發器來完成的。

2023-03-25 17:29:52 29287

29287

本文旨在總結近期復習的數字電路D觸發器(邊沿觸發)的內容。

2023-05-22 16:54:29 22344

22344

時序電路的考察主要涉及分析與設計兩個部分,上文介紹了時序邏輯電路的一些分析方法,重點介紹了同步時序電路分析的步驟與注意事項。 本文就時序邏輯電路設計的相關問題進行討論,重點介紹時序邏輯電路的核心部分——計數器。

2023-05-22 17:01:29 5307

5307

時序邏輯電路分析和設計的基礎是組合邏輯電路與觸發器,所以想要分析和設計,前提就是必須熟練掌握各種常見的組合邏輯電路與觸發器功能,尤其是各種觸發器的特征方程與觸發模式,因此前幾文的基礎顯得尤為重要。 本文主要介紹時序邏輯電路的分析方法。

2023-05-22 18:24:31 5504

5504

時間的重要性不言而喻,加上時間這個維度就如同X-Y的平面加上了一個Z軸,如同打開了一個新的世界。所以今天我們就要來聊聊時序電路。

2023-06-20 16:59:50 1063

1063

,在很多應用場景中都可以用來構建序列發生器。本文將介紹使用D觸發器設計序列發生器的方法和步驟。 首先,我們需要了解D觸發器的基本原理和性質。D觸發器是一種時序電路,它可以存儲和延遲一個輸入信號,并在時鐘信號到來時輸出

2023-08-24 15:50:17 6096

6096 D觸發器,是時序邏輯電路中必備的一個基本單元,學好 D 觸發器,是學好時序邏輯電路的前提條件,其重要性不亞于加法器,二者共同構成數字電路組合、時序邏輯的基礎。

2023-10-09 17:26:57 6026

6026

RS觸發器是一種經典的數字邏輯電路元件,用于存儲和控制信息流。它是由兩個反饋作用的邏輯門組成,常用于時序電路和數據存儲。 RS觸發器由兩個互補的輸出Q和~Q組成,其中Q表示觸發器的狀態為"1",~Q

2023-11-17 16:14:28 4298

4298 施密特觸發器是一種常見的數字電路元件,主要用于時序電路和數字邏輯電路中。它是由兩個雙穩態門電路(或稱為非門電路)構成的。在施密特觸發器中,輸出是由輸入信號的變化而變化的,而不是根據門電路的輸入和輸出

2024-01-12 16:50:30 4556

4556 jk觸發器是一種常見的時序電路元件,常用于計數器、寄存器以及存儲器等電子電路中。本文將介紹jk觸發器的特征方程以及推導過程。 jk觸發器的基本結構及原理 jk觸發器由兩個交叉耦合的反饋環組成,它具有

2024-01-17 10:00:22 6091

6091 RS觸發器與SR觸發器都是基本的數字邏輯電路元件,常用于存儲、控制和時序電路中。

2024-01-29 14:15:08 8678

8678 時序電路是由觸發器等時序元件組成的數字電路,用于處理時序信號,實現時序邏輯功能。根據時序元件的類型和組合方式的不同,時序電路可以分為同步時序電路和異步時序電路。本文將從這兩個方面詳細介紹時序電路,并

2024-02-06 11:22:30 2830

2830 ,時序電路可以分為同步時序電路和異步時序電路。接下來,我們將詳細討論時序電路的分類以及其基本單元電路。 一、同步時序電路 同步時序電路是指所有的時鐘信號在整個電路中具有相同的時鐘頻率和相位。它包括鎖存器、觸發器

2024-02-06 11:25:21 4240

4240 時序電路基本原理是指電路中的輸出信號與輸入信號的時間相關性。簡單來說,就是電路的輸出信號要依賴于其輸入信號的順序和時間間隔。 時序電路由時鐘信號、觸發器和組合邏輯電路組成。時鐘信號是時序電路的重要

2024-02-06 11:30:00 3204

3204 觸發器是數字電路中常用的組合邏輯電路,在現代電子系統中有著廣泛的應用。其中,最常用的兩種觸發器是T觸發器和JK觸發器。本文將詳細介紹T觸發器和JK觸發器的區別和聯系。 一、T觸發器 T觸發器是一種單

2024-02-06 14:04:55 7823

7823 時序電路是數字電子學中的一個核心概念,它利用了觸發器或其他記憶元件來存儲信息,并根據輸入信號和當前狀態產生輸出。

2024-05-23 15:14:50 4700

4700 在數字電路設計中,觸發器和時序邏輯電路是構建復雜數字系統不可或缺的基礎元素。觸發器(Flip-Flop)作為基本的存儲單元,能夠存儲一位二進制信息,并在特定的時鐘信號控制下更新其狀態。而時序邏輯電路

2024-07-18 17:43:41 4403

4403 。在數字電路中,觸發器通常用于實現寄存器、計數器、時序電路等功能。 二、觸發器的類型 觸發器有多種類型,根據其特性和應用場景的不同,可以分為以下幾類: SR觸發器(Set-Reset Flip-flop) :最基本的觸發器類型,具有Set和Reset兩個輸

2024-07-23 10:59:54 10317

10317 和保持四種功能,是集成觸發器中功能最為齊全的觸發器之一。由于其強大的通用性和靈活性,JK觸發器被廣泛應用于時序電路、頻率分析電路、數碼集成電路等多種數字電路中,特別是在計算機的寄存器中用于存儲二進制信息。

2024-07-27 14:53:31 11274

11274 在數字電路設計中,觸發器是一種非常重要的存儲元件,用于存儲一位二進制信息。觸發器的種類很多,其中最為常見的是T觸發器(Toggle Flip-Flop)和D觸發器(Data Flip-Flop

2024-08-11 09:37:25 6781

6781 雙穩態觸發器(Bistable Trigger or Flip-Flop)是一種具有兩個穩定狀態的數字電路元件,廣泛應用于數字邏輯電路、存儲器和時序電路中。 一、雙穩態觸發器的基本概念 1.1 定義

2024-08-11 10:00:52 5546

5546 在數字電路設計中,觸發器是一種非常重要的存儲元件,用于存儲一位二進制信息。觸發器的種類很多,其中最為常見的有JK觸發器、D觸發器和T觸發器等。 一、觸發器的基本概念 1.1 觸發器的定義 觸發器

2024-08-22 10:33:51 3767

3767 引言 數字電路是現代電子技術的基礎,廣泛應用于計算機、通信、控制等領域。觸發器是數字電路中的一種基本邏輯元件,具有存儲和傳遞信息的功能。 觸發器的基本概念 觸發器是一種具有記憶功能的數字電路元件

2024-08-22 10:37:33 5060

5060

電子發燒友App

電子發燒友App

評論