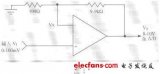

以往我們的設計總是集中在運放本身的規范上,但常常是無源元件會成為系統性能的主要限制。本文將集中討論在集成運放電路設計中,應如何正確地選擇無源元件 ,以使運放電路獲得

2012-03-07 11:00:51 4205

4205

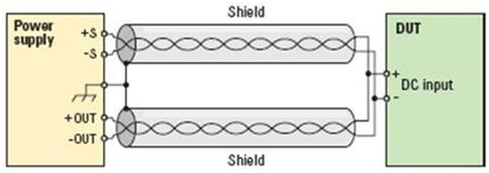

有些測試對于噪聲很敏感,那么如何降低噪聲?本文就選擇電源以及引線連接的方式兩個方面闡述如何降低測試中的噪聲。

2015-08-05 14:29:18 2213

2213

外部的噪聲通常指電源噪聲、空間耦合干擾等,通常通過合理的設計可以避免或減小影響。降低外部噪聲的影響對發揮低噪聲運放的性能至關重要。

2016-03-14 16:21:37 4492

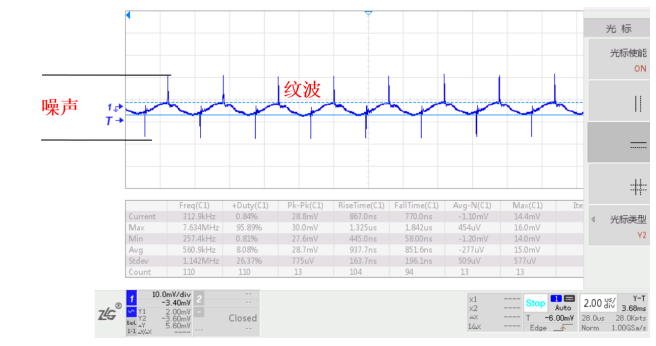

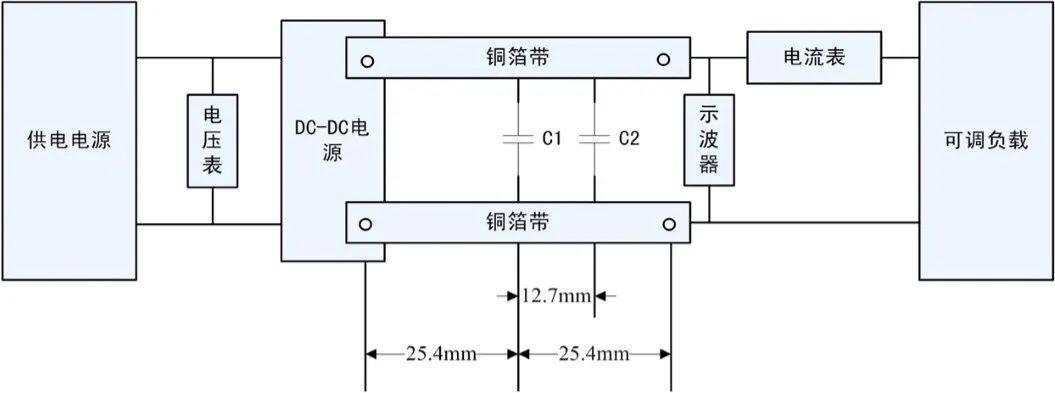

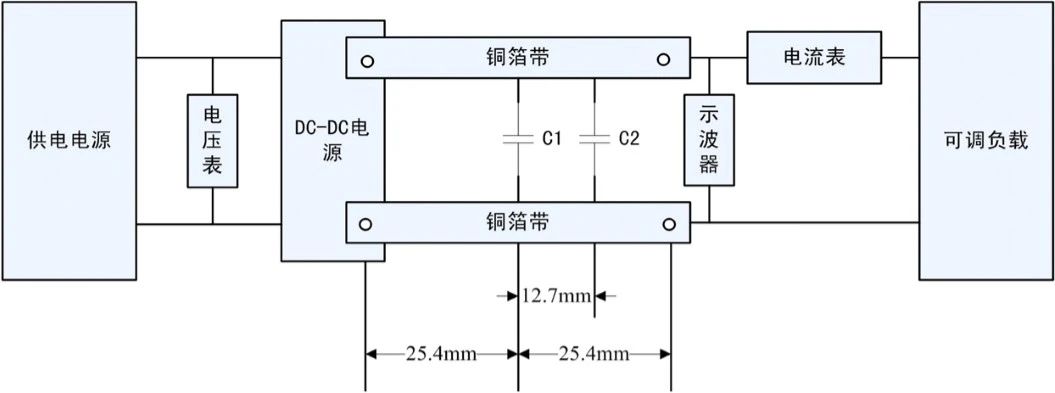

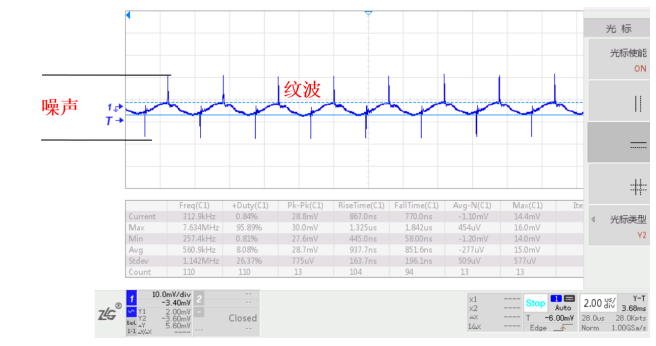

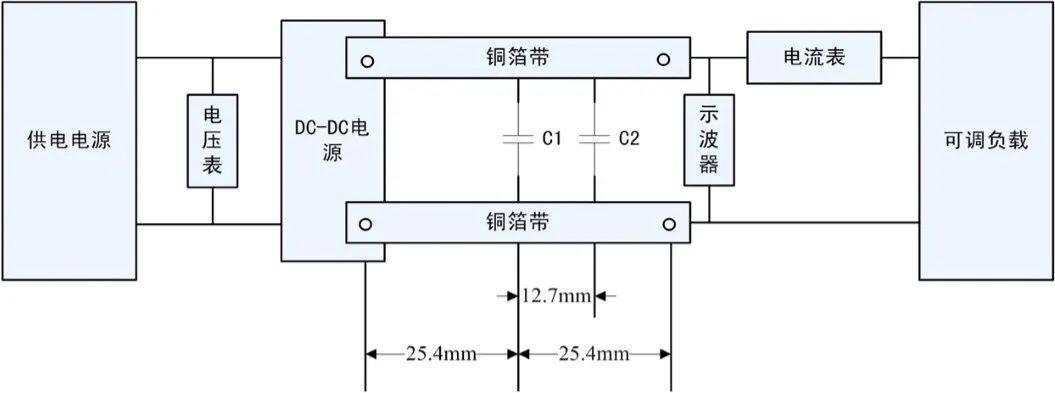

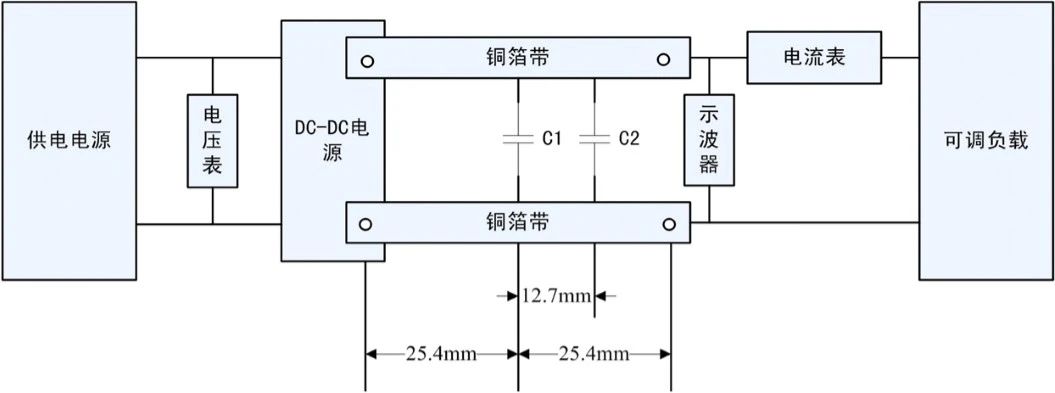

4492 在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。那么模塊的紋波噪聲該如何降低?下文為大家從紋波噪聲的波形、測試方式、模塊設計及應用的角度出發,闡述幾種有效降低輸出紋波噪聲的方法。

2018-08-08 14:53:36 9300

9300

在運放電路中,大家可能會經常看到這么幾個電容。

2023-02-01 10:27:19 6351

6351 輸出功率大,放大倍數相應調大才能滿足靈敏度的要求,放大倍數增大直接影響音頻功放的輸出底噪聲。如何降低這兩類音頻功放的輸出底噪聲,針對客戶在應用中的問題,總結以下方法可供參考:1. 分地 電路板上所有

2020-04-30 09:38:53

電源電路設計原理及應用 眾所皆知,電源電路設計,乃是在整體電路設計中最基礎的必備功夫,因此,在接下來的文章中,將會針對實體電源電路設計的案例做基本的探討。 電源device電路

2009-10-22 11:07:48

,各種方式開關穩壓器的設計方法及實例,電路設計中降低噪聲的技術技巧等。另外,本書附錄介紹了電源設計過程中散熱及散熱器安裝技巧和電源電路的新技術。

2020-11-03 11:02:28

在電路設計中,一般我們很關心信號的質量問題,但有時我們往往局限在信號線上進行研究,而把電源和地當成理想的情況來處理,雖然這樣做能使問題簡化,但在高速設計中,這種簡化已經是行不通的了。盡管電路設計比較直接的結果是從信號完整性上表現出來的,但我們絕不能因此忽略了電源完整性設計。因為電源完整性直...

2021-12-30 07:05:05

本項就電路上的噪聲對策進行說明。開關電源的設計時,必須進行噪聲的評估和對策。首先略為重溫與噪聲相關的術語。?EMI(Electro Magnetic Interference):電磁干擾 電波和高頻

2021-10-30 07:00:00

摘要:紋波噪聲是衡量電源的一個重要指標,一個好的電源必須要把輸出紋波噪聲控制在一個合理的范圍內。但一般有哪些行之有效的降低紋波噪聲的對策呢?下面我們拋磚引玉,簡單討論常用的八個方法。 1

2018-11-30 16:49:13

開關電源設計的噪聲降低法

2019-02-28 11:14:15

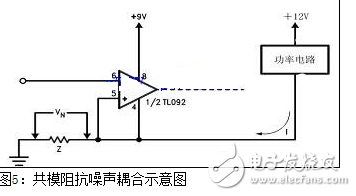

以上兩個參數,可以合理的設計電源工作頻率。 3.電源布局設計---噪聲的來源和降低 1)運放的輸入與輸出 在設計電源時,良好的布局可以降低電源噪聲,電源噪聲主要有三種:運算放大器的輸入與輸出

2023-03-16 15:55:02

電路設計中如何防止靜電放電? 對某些人來說 ESD 是一種挑戰,因為需要在處理和組裝未受保護的電子元件時不能造成任何損壞。 這是一種電路設計挑戰,因為需要保證系統承受住 ESD 的沖擊,之后

2023-04-07 17:07:59

小竅門。 下面是經過多年設計總結出來的,在PCB設計中降低噪聲與電磁干擾的24個竅門: (1) 能用低速芯片就不用高速的,高速芯片用在關鍵地方。 (2) 可用串一個電阻的辦法,降低控制電路上下沿

2018-09-18 15:40:54

RF電路設計中降低寄生信號的八大途徑

2021-04-06 07:08:47

鄙人需要測量十幾pA的電流,,以下是我設計的方案,但是怕RF電阻噪聲太大,請教電路設計和噪聲分析?拜托了@

2018-09-11 10:05:01

,這樣,就可以使運放電路在有限的帶寬內只有一個極點,使運放電路變得容易調整。以上為運放電路設計中容易出現的問題和合適的解決方案,希望對大家有所啟發。`

2019-09-17 07:00:00

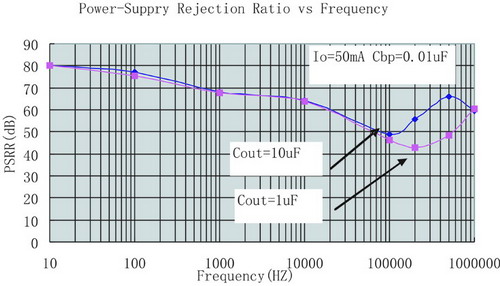

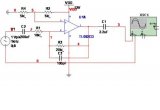

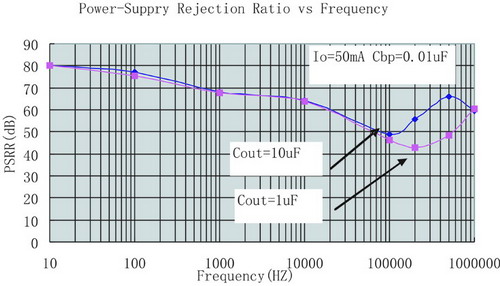

在全波整流的線性穩壓供電的電路中,100Hz紋波是主要的電源噪聲,對于運放電路,100Hz噪聲電平通常要求控制在10nV-100nV(RTI)內,這取決于三個因素:運放在100Hz時的電源抑制比

2018-03-28 17:14:04

從0學運放,史上最全運放電路設計入門資料從零學運放—01運算放大器的參數從零學運放—02怎樣分析運放電路從零學運放—03 運放設計中的常遇到的三FAQ從零學運放—04 單電源運放的設計從零學運放

2017-04-08 16:44:35

如果想要更小的噪聲的話應該依據什么選呢?另外如果想在現有電路基礎上降噪,有什么合適的辦法呢?最后想了解運放電路噪聲降低的問題的話,有什么資料和書籍可以看呢,現在有點不知道從哪下手?十分感謝!!!

2018-12-05 16:26:08

功放電路自身已帶電源,但在使用時也要外接電源,請問這兩者的關系,工作原理是怎樣的?

2011-08-07 22:51:52

摘要:紋波噪聲是衡量dcdc電源模塊一個重要指標,一個好的dcdc電源模塊必須要把輸出紋波噪聲控制在一個合理的范圍內。但一般有哪些行之有效的降低紋波噪聲的對策呢?下面由小編為您講解一下具體的方法。1

2018-08-09 13:58:12

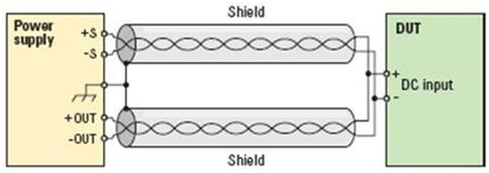

在測量過程中,有些被測件對直流電源輸入中的噪聲非常敏感,直接關乎到測試數據的準確性甚至測試是否能進行,那么怎樣盡可能地減少輸入噪聲呢?

2015-09-17 14:32:30

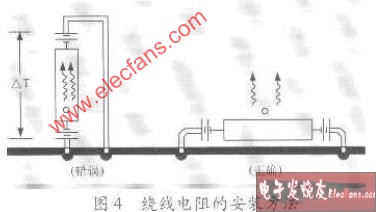

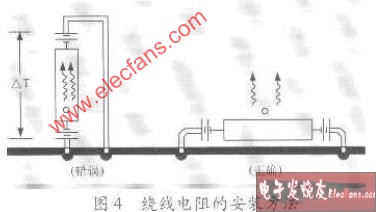

電源線不要和信號線捆扎在一起。

小結

在運放電路設計中降低電源噪聲的主要措施包括:

通過去耦、濾波等措施降低電源輸出的紋波和噪聲成分。

改善設計,提高電源電壓調整率。

合理電路結構、考究的PCB布線、合理的走線工藝。

選擇在敏感噪聲頻段的PSRR或CMRR較高的器件。

2023-11-21 06:27:27

,注意屏蔽層連接到被保護信號的參考地;走線設計上注意電源線不要和信號線捆扎在一起。小結在運放電路設計中降低電源噪聲的主要措施包括:通過去耦、濾波等措施降低電源輸出的紋波和噪聲成分。改善設計,提高電源電壓

2017-10-19 23:34:27

;使用1000p電容射頻多點接地,可以兼顧EMC和低頻信噪比的需求;對敏感電路加屏蔽,注意屏蔽層連接到被保護信號的參考地;走線設計上注意電源線不要和信號線捆扎在一起。小結在運放電路設計中降低電源噪聲的主要

2018-12-29 10:10:32

,可以合理的設計電源工作頻率。3. 電源布局設計 --- 噪聲的來源和降低1)運放的輸入與輸出在設計電源時,良好的布局可以降低電源噪聲,電源噪聲主要有三種:運算放大器的輸入與輸出,參考電壓和斜坡。如下

2020-10-03 19:30:00

分享最簡單可行的兩個步驟去有效降低測試中的噪聲

2021-05-07 06:54:16

捆扎在一起。小結:在運放電路設計中降低電源噪聲的主要措施包括- 通過去耦、濾波等措施降低電源輸出的紋波和噪聲成分 - 改善設計,提高電源電壓調整率 - 合理電路結構、考究的PCB布線、合理的走線工藝 - 選擇在敏感噪聲頻段的PSRR或CMRR較高的器件

2019-06-18 07:30:00

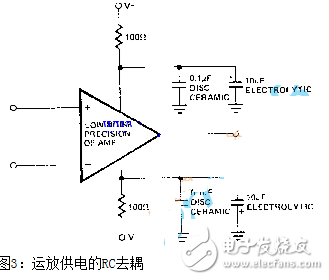

在運放中或者其他電路設計中我們會在電源上加一對旁路電容,一個大電容一個小電容倘若我為獲得更高的電源頻率濾除效果我再并接一個更小的電容或者并接更多的小電容來獲得更高的頻率響應,這個方法可行嗎?

2024-09-02 08:24:49

降低開關電源輸出紋波與噪聲的常用方法

2021-03-16 13:50:26

的責任。

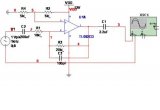

1.1 虛地

在單電源供電的運放電路中,需要外部提供一個虛地,通常為VCC的一半(VCC/2)。雖然這種方法能產生所需的電壓,但可能會降低系統的低頻特性。

圖2

R1和R2是等值電阻,選擇時需

2024-08-30 14:22:07

本帖最后由 siyugege 于 2015-12-30 15:09 編輯

我們要怎么降低電源輸出紋波噪聲?紋波噪聲是衡量電源的一個重要指標,一個好的電源必須要把輸出紋波噪聲控制在一個合理

2015-12-30 11:30:42

開關電源的特點是會產生很強的電磁噪聲,如果不嚴格控制,會產生很大的干擾。 下面介紹的技術有助于降低開關電源的噪聲,并可用于高度敏感的模擬電路。1.電路和設備的選擇關鍵是將dv / dt和di

2022-05-25 10:40:40

如何降低運放電路中的電源噪聲你能從這本書中學到什么這本書從電源噪聲產生的原因出發,深入分析了消除電源噪聲干擾的對策和影響準確性的因素。其中包括:電源噪聲產生的各種原因分析電源噪聲余量該從何分析如何消除電源

2019-02-26 18:13:03

在電路設計中涉及到電源部分的設計,關于電源芯片的選型是個很重要的問題。很多人知道用三端穩壓集成電路LM7805,因為這種電源芯片用得最多,電路應用范例也成熟。在我設計電路中接觸到的電源芯片,下面介紹

2019-02-26 06:30:00

噪聲波形轉換到頻域進行分析,從而更準確地定位噪聲來源和特性。頻域示波器在電源噪聲分析中的優勢

定位噪聲來源:

電源噪聲可能來自開關電源的開關動作、外部電磁干擾(EMI)或電路布局不合理等因素。頻域

2025-03-14 15:03:35

DC/DC電路噪聲:文波和噪聲DC/DC電源電路具有功耗低,功率高的優點,但同時由于DC/DC電路轉換通過開關方式完成,造成不可避免的噪聲引入,具體為電源電路的紋波和噪聲。在高速電路設計中,高端芯片

2019-12-14 07:00:00

|數字功放電路設計制作

2008-01-21 22:02:15 307

307 眾所皆知,電源電路設計,乃是在整體電路設計中最基礎的必備功夫,因此,在接下來的文章中,將會針對實體電源電路設計的案例做基本的探討。電源device電路※輸出電

2008-05-13 08:46:33 446

446 模擬電源電路設計資料(經典):眾所皆知,電源電路設計,乃是在整體電路設計中最基礎的必備功夫,因此,在接下來的文章中,將會針對實體電源電路設計的案例做基本的探討。

2010-01-04 18:35:43 117

117 模擬電源電路設計資料(經典)

電源電路設計.

眾所皆知,電源電路設計,乃是在整體電路設計中最基礎的必備功夫,因此,在接下來的文章中,將會針對

2010-03-13 15:24:58 0

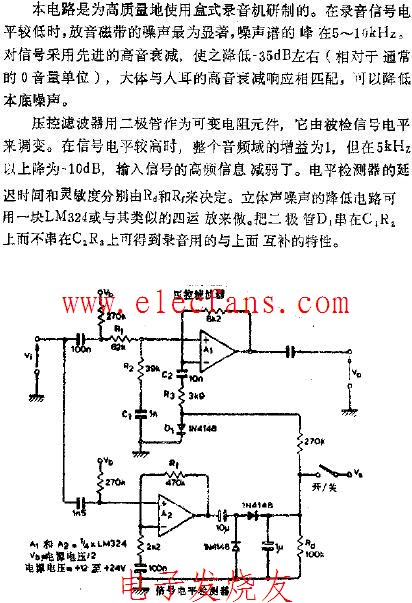

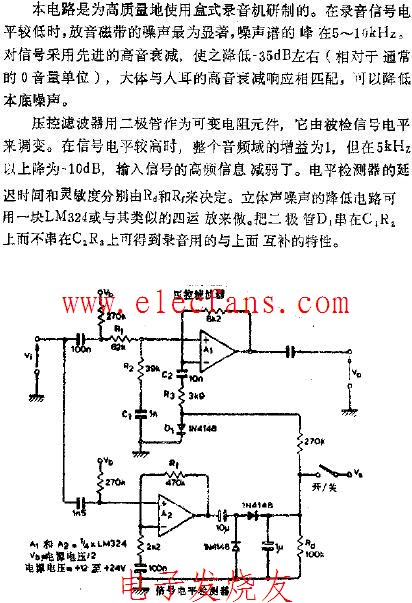

0 降低動態噪聲的電路圖

2008-02-25 22:09:09 971

971

運放電路設計中無源元件的選擇

以往我們的設計總是集中在運放本身的規范上,但常常是無源元件會成為系統性能的主要限制。本

2009-02-10 14:13:25 1358

1358

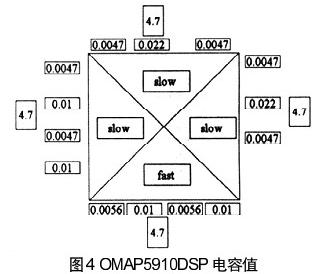

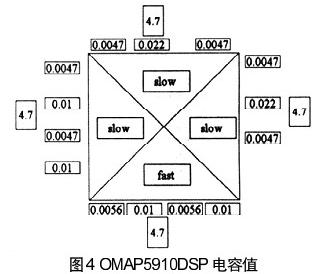

為了降低電源噪聲,對于高速DSP系統設計人員來講,識別和找出可能的噪聲原因以及采用良好的高速設計實踐是關鍵。本文說明交擾、鎖相環(PLL)、去耦/體電容器在降低噪聲中

2009-03-20 11:03:47 717

717

運放電路的電源噪聲電路圖

2009-07-17 14:52:56 1114

1114 RF電路中LDO電源抑制比和噪聲原理及選擇

本文討論LDO的特點以及RF電路對LDO的電源抑制比和噪聲的選擇。引言便攜產品電源設計需

2010-03-09 16:51:32 2972

2972

無噪聲的的功放電源電路

工作原理:交流電源輸入經T1進行濾波后分成兩路輸出,一路去降壓變壓器T3,在T3的初

2010-10-03 15:48:20 3710

3710 眾所皆知,電源電路設計,乃是在整體電路設計中最基礎的必備功夫,因此,在接下來的文章中,將會針對實體電源電路設計的案例做基本的探討。

2011-09-06 15:07:40 547

547 為什么要重視電源噪聲問題,內部晶體管狀態的轉換必然引起電源噪聲在芯片內部的傳遞,如果是由于電源系統產生的問題,電路將非常難調試,因此最好在電路設計之初就遵循某種成

2011-11-30 15:41:58 994

994 開關電源的特征就是產生強電磁噪聲,若不加嚴格控制,將產生極大的干擾。下面介紹的技術有助于降低開關電源噪聲。

2011-12-19 16:28:34 4127

4127 眾所皆知,電源電路設計,乃是在整體電路設計中最基礎的必備功夫,因此,在接下來的文章中,將會針對實體電源電路設計的案例做基本的探討。

2016-04-15 09:43:59 90

90 在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。下文結合紋波噪聲的波形、測試方式,從電源設計及外圍電路的角度出發,闡述幾種有效降低輸出紋波噪聲的方法。 1、電源的紋波與噪聲圖示 紋波和噪聲即:直流電源輸出上疊加的與電源開關頻率同頻的波動為紋波,高頻雜音為噪聲。

2016-11-09 02:08:11 10035

10035

如何降低電源紋波噪聲的分析與應用

2017-02-08 01:27:55 17

17 引起的噪聲使音頻、視頻、圖像和通信功能降低并對達到FCC/CE商標認證造成問題。為了降低電源噪聲,對于高速DSP系統設計人員來講,識別和找出可能的噪聲原因以及采用良好的高速設計實踐是關鍵。本文說明交擾、鎖相環(PLL)、去耦/體電容器在降低噪聲中

2017-10-29 10:47:33 0

0 運放電路設計中無源元件的選擇,selection of passive components in OPAMP circuit

關鍵字:運放電路設計,無源元件選擇

2018-09-20 18:18:40 1480

1480 開關電源的特征就是產生強電磁噪聲,若不加嚴格控制,將產生極大的干擾。下面介紹的技術有助于降低開關電源噪聲,能用于高靈敏度的模擬電路。

2018-10-14 10:43:00 5272

5272 紋波噪聲是衡量電源的一個重要指標,但有多少人知道紋波和噪聲其實是兩個性能指標,降低紋波和噪聲的方法是有一定區別的,本文將與大家一起探索如何降低紋波和噪聲。

2019-06-20 14:27:08 13530

13530

我們在設計電路板的時候,電路原理設計的很好,甚至說很優秀,但是,在調試過程中會出現各種各樣的噪聲,電路板不能達到預期目的,有時更甚者,不得不重新layout板子。那么怎樣才能降低電路板的噪聲呢?下面為大家來分析一下:

2020-08-16 09:23:44 7400

7400 首先,線路板設計帶有開關模式電源(SMPS)的電路可能會令人生畏,尤其是在嘗試降低噪聲時。 我們了解SMPS電路中噪聲(波紋和EMI)的概念,以及電路的布局和可以減輕噪聲的簡單設計技術。我們將從更大

2021-01-11 12:01:17 2336

2336

高速電路設計中的信號衰減是讓人頭疼的一件事,作為電路設計工程師在布線時應該降低信號衰減。本文主要介紹高速電路設計中降低信號衰減方法,希望對你有所幫助。 一、降低電抗路徑 在高速電路設計中,將接地

2021-01-28 11:06:26 4031

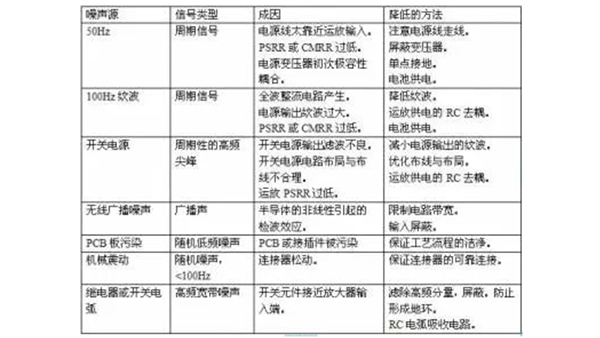

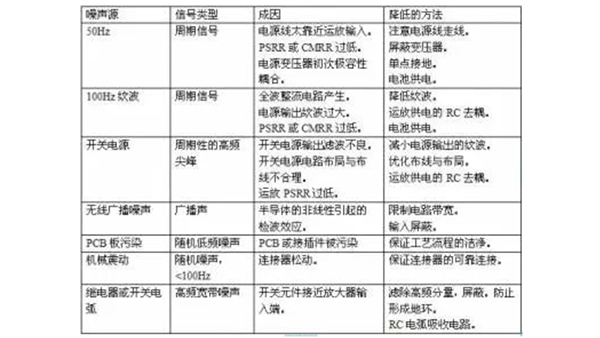

4031 、散彈噪聲和低頻噪聲(1/f噪聲)等;外部的噪聲通常指電源噪聲、空間耦合干擾等,通常通過合理的設計可以避免或減小影響。降低外部噪聲的影響對發揮低噪聲運放的性能至關重要。

常見外部噪聲源...

2022-02-22 11:23:41 2572

2572

通過對電路原理及邏輯關系的分析,闡明了CAN總線在客車電源、起動及熄火電路設計中的應用。

2021-04-12 16:36:09 37

37 眾所皆知,電源電路設計,乃是在整體電路設計中最基礎的必備功夫,因此,在接下來的文章中,將會針對實體電源電路設計的案例做基本的探討。

2021-04-16 10:07:30 56

56 電子發燒友網為你提供在運放電路設計中降低電源噪聲的主要措施資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-24 08:47:12 16

16 Saber軟件在電源電路設計中的應用技巧說明。

2021-06-19 10:33:00 35

35 擴頻降低EMI的DCDC穩壓器電路設計(ups電源技術參數)-該文檔為擴頻降低EMI的DCDC穩壓器電路設計總結文檔,是一份不錯的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-22 12:21:28 14

14 電路設計中電源芯片LDO還是DCDC的區別(通信電源技術 官方網站)-該文檔為電路設計中電源芯片LDO還是DCDC的區別總結文檔,是一份不錯的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-22 12:46:23 148

148 降低開關電源的紋波噪聲(通信電源技術雜志訂閱)-?降低開關電源的紋波噪聲,非常好的資料一、什么叫紋波??紋波(ripple)的定義是指在直流電壓或電流中,疊加在直流穩定量上的交流分

量;

它主要有

2021-09-27 09:41:41 29

29 在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。那么模塊的紋波噪聲該如何降低?下文為大家從紋波噪聲的波形、測試方式、模塊設計及應用的角度出發,闡述幾種有效降低輸出紋波噪聲的方法

2022-02-11 15:18:00 14

14 DC/DC電源電路具有功耗低,功率高的優點,但同時由于DC/DC電路轉換通過開關方式完成,造成不可避免的噪聲引入,具體為電源電路的紋波和噪聲。

2022-12-26 09:20:43 2366

2366 在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。下文結合紋波噪聲的波形、測試方式,從電源設計及外圍電路的角度出發,闡述幾種有效降低輸出紋波噪聲的方法。紋波噪聲的測試方法對于中小

2023-05-08 09:48:54 1742

1742

在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。下文結合紋波噪聲的波形、測試方式,從電源設計及外圍電路的角度出發,闡述幾種有效降低輸出紋波噪聲的方法。

2023-06-20 17:48:24 4036

4036

降低電源紋波噪聲的方法與實例

2023-10-24 17:37:22 1425

1425

如何降低放大器噪聲?? 放大器噪聲是實際電路中不可避免的。噪聲會對放大器的性能產生負面影響,因此在電子設計中,降低噪聲是一個非常重要的任務。在本文中,我們將討論如何降低放大器的噪聲。 1.理解噪聲

2023-09-19 16:50:01 2567

2567 在電子設備和系統中,電源噪聲是一個普遍存在的問題。電源噪聲會影響設備的性能、穩定性、可靠性和安全性。為了降低電源噪聲,我們可以采用各種方法,其中一種非常有效的方法是利用電源濾波器。那么,電源濾波器是怎么降低電源噪聲的?跟著電源濾波器維愛普小編一起來看一下。

2023-09-25 12:35:08 1760

1760 電阻Rb是什么作用?在運放電路中,何時加入Rb呢? 電阻Rb在運放電路中扮演著重要的角色。運放(Operational Amplifier)是一種具有巨大增益和高輸入阻抗的電子設備,廣泛應用于各種

2023-10-23 10:29:14 5545

5545 電源濾波器是怎么降低電源噪聲的? 隨著現代電子設備的發展,我們的生活變得越來越依賴電力。但是,這些設備所使用的電力并非完美的直流電,往往會受到來自外部環境的各種噪聲干擾,例如電源中的高頻噪聲,通常

2023-10-25 15:38:29 1444

1444 因為同相輸入端的電阻可以起到降低電流噪聲和共模噪聲的作用,同時還能改善電路的穩定性和可靠性。 首先,同相輸入端的電阻可以降低電流噪聲。在理想的運放中,同相輸入端的電壓等于反相輸入端的電壓,因此,同相輸入端的電流可

2023-10-29 17:29:56 7040

7040 的噪聲組成。 1. 熱噪聲 在運放電路中,最主要的噪聲來源之一是熱噪聲。這種噪聲是由于電路中的電阻體發出的,這種電阻體通常是將電流轉化為熱能的材料。其基本原理是熱噪聲與電阻體的阻值成正比,溫度與根號T成正比。因此,任何

2023-10-30 09:11:54 1495

1495 電源是如何影響放大電路的輸出噪聲的呢? 電源對于放大電路的輸出噪聲有著非常重要的影響。電路中的噪聲可以來源于多個方面,包括器件本身的熱噪聲、器件內部的電磁干擾、電源本身的噪聲以及其它外部環境噪聲等

2023-11-06 11:14:14 1392

1392 PD放大電路主要的噪聲源是哪些?如何降低PD放大電路噪聲? PD放大電路的主要噪聲源包括熱噪聲、隨機噪聲和1/f噪聲。熱噪聲源于電阻器的熱漲落,而隨機噪聲則由電子的熱激發引起。1/f噪聲則是一種低頻

2023-11-06 11:14:20 1751

1751 請問運放產生噪聲的原理是什么?怎么可以降低? 運放(Operational Amplifier,簡稱OP-AMP)是一種重要的電子元件,廣泛應用于模擬和線性電路中。然而,在實際應用中,運放會生成一定

2023-11-09 15:38:32 3185

3185 降低開關電源噪聲

2023-11-24 15:39:50 1166

1166 電源濾波器是怎么降低電源噪聲的? 電源濾波器是一種電子裝置,用于減少或消除電源中的噪聲。噪聲是電力系統中的一個常見問題,它可以由各種因素引起,包括電源脈動、電源雜散、電磁干擾等。這些噪聲不僅會對

2023-12-15 14:37:56 1572

1572 開關電源在運行時會產生多種噪聲,這些噪聲具有不同的特性和頻率。為了有效降低這些噪聲,我們采用各種針對性的策略和部件。 對于DC/DC轉換器這類設備,通常會根據其電路設計和工作電壓,選用由電感(L

2024-02-05 10:12:53 1771

1771 如何降低開關電源輸出紋波與噪聲

2024-03-12 19:49:03 2242

2242 電源濾波器作為電子設備中不可或缺的組成部分,其性能直接影響到設備的穩定性和可靠性。通過深入了解電源噪聲的來源、濾波器的工作原理及類型,并合理應用濾波技術,我們可以有效地降低電源噪聲,為電子設備提供一

2024-09-20 17:55:35 1167

1167

功放電路電源設計是確保功放電路穩定運行和提供足夠功率輸出的重要環節。以下是一些關于功放電路電源設計注意事項的介紹: 一、電源變壓器選擇 功率匹配 :電源變壓器的功率應足夠大,至少應為機內各部電路總耗

2024-12-03 10:41:33 2211

2211 在設計場效應管驅動電路時,降低場效應管的噪聲是至關重要的。以下是一些有效的措施來降低場效應管的噪聲: 一、電源噪聲的抑制 選擇穩定的電源 : 使用低噪聲、穩定的電源為場效應管供電,可以減少電源波動

2024-12-09 16:17:42 2025

2025 一、引言 運放電路中電容的常見身影 在運放電路里,我們常常能看到電容出現在一些特定的位置,比如電源 VCC 到地之間,反饋輸入輸出引腳之間,以及正負兩輸入端之間。即便電路中沒有這些電容,似乎也能夠

2024-12-22 15:00:00 3132

3132

低噪聲運放應用于微分器電路設計

2025-01-03 17:49:59 1109

1109

過程困難重重。例如,在無線通信接收機前端,外界環境噪聲、電路熱噪聲等與目標射頻信號一同進入接收鏈路。這些噪聲在頻譜上與信號相互混雜,降低了信號的信噪比(SNR)。就好比在嘈雜的集市中辨別遠處傳來的輕聲呼喊,信噪比的降低使

2025-02-05 15:45:00 941

941 在電子電路的運行過程中,噪聲如同不速之客,嚴重干擾信號的正常傳輸與處理,影響電路性能甚至導致系統故障。如何有效抑制電子電路中的噪聲,成為工程師們在電路設計與優化過程中必須攻克的難題。本文將從噪聲

2025-05-05 10:04:00 1512

1512 出有效的解決方案。 ?一、三星電容噪聲問題的成因 電容本身的物理特性 :電容在充放電過程中,由于介質損耗、電極反應等因素,會產生一定的噪聲。這種噪聲在高頻電路中尤為明顯,可能干擾電路的正常工作。 電路設計 :不合理的

2025-09-01 16:19:50 557

557

電子發燒友App

電子發燒友App

評論