鎖相環(huán)電路

鎖相環(huán)

2009-09-25 14:28:39 7723

7723

鎖相環(huán):在通信領(lǐng)域中,鎖相環(huán)是一種利用反饋控制原理實(shí)現(xiàn)的頻率及相位同步技術(shù),其作用是將電路輸出的時(shí)鐘與其外部的參考時(shí)鐘保持同步。

2023-06-30 15:53:39 6426

6426

大家都知道鎖相環(huán)很重要,它是基石,鎖相環(huán)決定了收發(fā)系統(tǒng)的基礎(chǔ)指標(biāo),那么如此重要的鎖相環(huán)選型原則有哪些呢?

2023-08-01 09:37:05 7303

7303

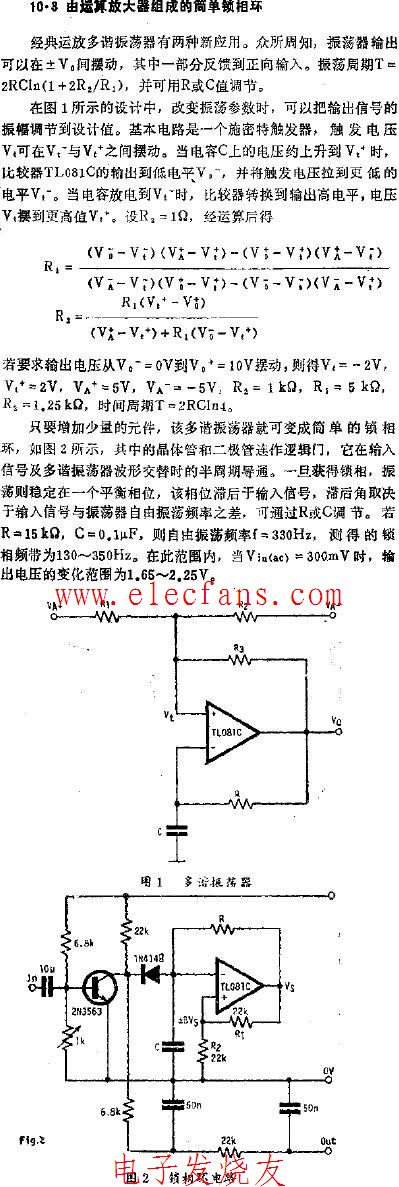

鎖相環(huán)是一種 反饋系統(tǒng) ,其中電壓控制振蕩器和相位比較器相互連接,使得振蕩器頻率(相位)可以準(zhǔn)確跟蹤施加的頻率或相位調(diào)制信號(hào)的頻率。鎖相環(huán)可用來(lái)從固定的低頻信號(hào)生成穩(wěn)定的輸出頻率信號(hào)。首批鎖相環(huán)由

2023-11-30 15:01:08 3710

3710

鎖相環(huán)仿真,可以參考一下!

2012-08-13 09:11:17

請(qǐng)問(wèn)鎖相環(huán)仿真用什么軟件好,我們需要用到ADF4110VOC選擇MAX2606

2016-06-27 15:57:53

用教材上的圖仿真一個(gè)鎖相環(huán),但是仿真過(guò)程總是提示按鍵開(kāi)關(guān)旁邊的電阻有錯(cuò)誤,還有就是截圖的那個(gè)電容有錯(cuò)誤還有一個(gè)錯(cuò)誤我就不知道了各位大神,求解啊求解啊

2013-05-03 16:47:56

我有一個(gè)鎖相環(huán)電路的pcb板和proteus仿真電路。

2023-10-04 07:58:55

要實(shí)現(xiàn)鎖相環(huán)的基本原理及工作狀態(tài),如何編寫(xiě)程序呢?

2014-06-11 21:33:38

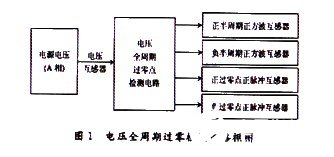

而已,設(shè)計(jì)出來(lái)的鎖相環(huán)肯定很精確。但是,在物理控制器中,還有一種很簡(jiǎn)單的設(shè)計(jì)方法,也就是我們的項(xiàng)目曾經(jīng)使用的鎖相方法,直接采集A相電壓,然后判斷A相電壓的過(guò)零點(diǎn),如果出現(xiàn)過(guò)零點(diǎn),那么就記錄下該時(shí)刻

2015-01-04 22:57:15

, 輸入信號(hào)與壓控振蕩器輸出信號(hào)之間的頻差為零, 相位不再隨時(shí)間變化, 誤差電壓為一固定值, 這時(shí)環(huán)路就進(jìn)入鎖定狀態(tài)。-------這個(gè)說(shuō)的是鎖相環(huán)工作的原理,如何穩(wěn)定頻率點(diǎn)的,但是沒(méi)看懂啥意思哪個(gè)知道的請(qǐng)指點(diǎn)迷津一下

2022-06-22 19:16:46

本人在進(jìn)在做鎖相環(huán)的仿真,進(jìn)行頻率跟蹤的用的,可是怎么做都放不出波形,可有會(huì)仿真鎖相環(huán)的?

2014-06-23 11:14:38

頻率合成器的主要性能指標(biāo)鎖相環(huán)頻率合成器原理鎖相環(huán)頻率合成器捕捉過(guò)程的分析與仿真

2021-04-22 06:27:35

新版AD公司鎖相環(huán)仿真軟件

2013-07-20 21:44:03

求助,CD4046鎖相環(huán)的參數(shù)要怎么設(shè)計(jì)呀?我設(shè)計(jì)的時(shí)候是根據(jù)datasheet設(shè)計(jì)的,可是用protues仿真的時(shí)候,在中心頻率也入不了鎖,引腳1輸出總是一高一低,然后把輸入信號(hào)的電壓調(diào)大后,不管

2020-10-11 13:02:47

、相位偏移等設(shè)計(jì)時(shí),寫(xiě)代碼的方式就顯得力不從心。此時(shí)就體現(xiàn)了學(xué)習(xí)鎖相環(huán)的必要性。接下來(lái)我們一起了解一下鎖相環(huán)的使用。

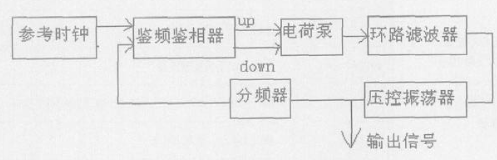

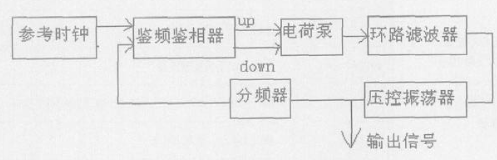

PLL鎖相環(huán)由以下幾部分組成:前置分頻計(jì)數(shù)器、相位頻率檢測(cè)器電路、電荷泵、環(huán)路

2023-06-14 18:09:08

LabVIEW鎖相環(huán)(PLL) 鎖相環(huán)是一種反饋電路,其作用是使得電路上的時(shí)鐘和某一外部時(shí)鐘的相位同步。PLL通過(guò)比較外部信號(hào)的相位和由壓控晶振(VCXO)的相位來(lái)實(shí)現(xiàn)同步的,在比較的過(guò)程中,鎖相環(huán)

2022-05-31 19:58:27

原理實(shí)現(xiàn)的頻率及相位的同步技術(shù),其作用是將電路輸出的時(shí)鐘與其外部的參考時(shí)鐘保持同步。當(dāng)參考時(shí)鐘的頻率或相位發(fā)生改變時(shí),鎖相環(huán)會(huì)檢測(cè)到這種變化,并且通過(guò)其內(nèi)部的反饋系統(tǒng)來(lái)調(diào)節(jié)輸出頻率,直到兩者

2021-11-04 08:57:18

PLL(鎖相環(huán))電路原理是什么?

2022-01-21 07:03:37

前輩們你們好,我是在校學(xué)生在做鎖相環(huán)鑒頻仿真實(shí)驗(yàn),但是無(wú)法得到好的結(jié)果,請(qǐng)問(wèn)前輩們可以指導(dǎo)一下么?謝謝!

2020-06-01 10:20:04

采用后向Euler數(shù)值積分法實(shí)現(xiàn)二階鎖相環(huán)的一個(gè)仿真模型,對(duì)二階鎖相環(huán)進(jìn)行仿真,那位大俠做過(guò)?可以參考下原代碼不?

2012-05-28 17:21:05

全數(shù)字鎖相環(huán)的設(shè)計(jì)及分析 1 引 言 鎖相環(huán)是一種能使輸出信號(hào)在頻率和相位上與輸入信號(hào)同步的電路,即系統(tǒng)進(jìn)入鎖定狀態(tài)(或同步狀態(tài))后,震蕩器的輸出信號(hào)與系統(tǒng)輸入信號(hào)之間相差為零,或者保持為常數(shù)

2010-03-16 10:56:10

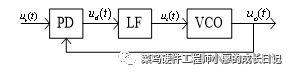

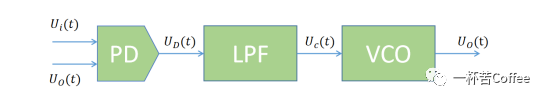

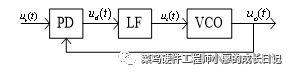

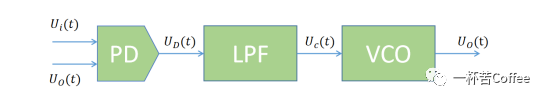

鎖相環(huán)路是一種反饋控制電路,簡(jiǎn)稱(chēng)鎖相環(huán)(PLL)。許多電子設(shè)備要正常工作,通常需要外部的輸入信號(hào)與內(nèi)部的振蕩信號(hào)同步,利用鎖相環(huán)路就可以實(shí)現(xiàn)這個(gè)目的。鎖相環(huán)通常由鑒相器(PD)、環(huán)路濾波器(LF

2019-03-17 06:00:00

使用場(chǎng)合。為實(shí)現(xiàn)無(wú)軸承同步磁阻電機(jī)高速超高速、低成本、實(shí)用化運(yùn)行,提出了一種基于鎖相環(huán)法的無(wú)速度傳感自檢測(cè)技術(shù)。通過(guò)應(yīng)用鎖相環(huán)原理,設(shè)計(jì)出無(wú)軸承同步磁阻電機(jī)無(wú)速度傳感器,并基于 Matlab

2025-07-29 16:22:56

一、內(nèi)容繼續(xù)無(wú)霍爾的學(xué)習(xí),根據(jù)原理及仿真,了解相關(guān)原理和實(shí)現(xiàn)方法。二、知識(shí)點(diǎn)1.基于鎖相環(huán)的轉(zhuǎn)子位置估計(jì)反正切函數(shù)的轉(zhuǎn)子位置估算由于是根據(jù)估算的擴(kuò)展反電動(dòng)勢(shì)進(jìn)行計(jì)算的,但是由于滑模控制在滑動(dòng)模態(tài)下

2021-08-27 06:54:13

全數(shù)字鎖相環(huán)由那幾部分組成?數(shù)字鎖相環(huán)的原理是什么?如何采用VHDL實(shí)現(xiàn)全數(shù)字鎖相環(huán)電路的設(shè)計(jì)?

2021-05-07 06:14:44

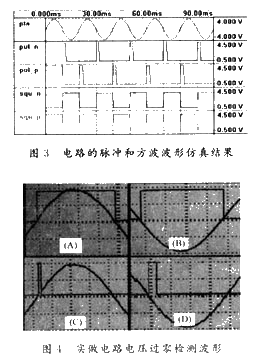

過(guò)零點(diǎn)存在毛刺,故此處選用由LM311(U1、U6)構(gòu)成的遲滯比較器實(shí)現(xiàn)過(guò)零檢測(cè)和方波整形。U1檢測(cè)電網(wǎng)電壓上升沿的過(guò)零點(diǎn),U4檢測(cè)電網(wǎng)電壓下降沿的過(guò)零點(diǎn)。3改進(jìn)鎖相環(huán)穩(wěn)定度的硬軟件方法 過(guò)零檢測(cè)電路

2018-12-05 09:53:26

由LM311(U1、U6)構(gòu)成的遲滯比較器實(shí)現(xiàn)過(guò)零檢測(cè)和方波整形。U1檢測(cè)電網(wǎng)電壓上升沿的過(guò)零點(diǎn),U4檢測(cè)電網(wǎng)電壓下降沿的過(guò)零點(diǎn)。3改進(jìn)鎖相環(huán)穩(wěn)定度的硬軟件方法過(guò)零檢測(cè)電路對(duì)電網(wǎng)過(guò)零點(diǎn)的檢測(cè)精度對(duì)數(shù)

2018-12-03 14:01:24

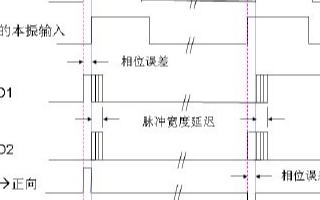

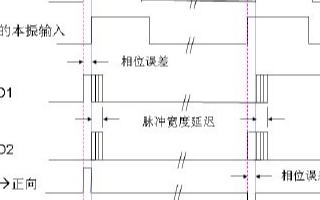

本文介紹了電荷泵鎖相環(huán)電路鎖定檢測(cè)的基本原理,通過(guò)分析影響鎖相環(huán)數(shù)字鎖定電路的關(guān)鍵因子,推導(dǎo)出相位誤差的計(jì)算公式。并以CDCE72010 為例子,通過(guò)實(shí)驗(yàn)驗(yàn)證了不合理的電路設(shè)計(jì)或外圍電路參數(shù)是如何影響電荷泵鎖相環(huán)芯片數(shù)字鎖定指示的準(zhǔn)確性。

2021-04-20 06:00:37

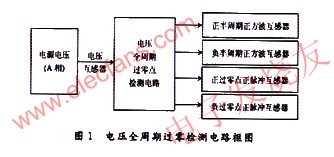

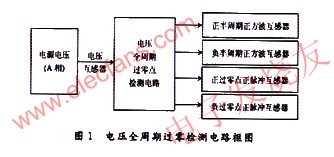

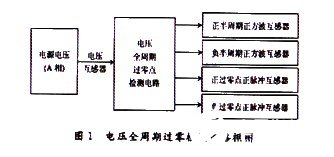

怎么設(shè)計(jì)一種無(wú)鎖相環(huán)的交流電壓全周期過(guò)零檢測(cè)電路?無(wú)鎖相環(huán)電壓全周期過(guò)零檢測(cè)電路原理是什么?如何設(shè)置交流電壓全周期過(guò)零檢測(cè)電路系統(tǒng)仿真參數(shù)?

2021-04-14 06:41:47

我剛接觸鎖相環(huán)沒(méi)多長(zhǎng)時(shí)間,最近想使用ADF4106搭建一個(gè)雙環(huán)鎖相環(huán),我閱讀的資料都沒(méi)有說(shuō)主環(huán)路環(huán)路濾波器參數(shù)計(jì)算問(wèn)題,我想咨詢(xún)專(zhuān)家ADIsimPLL是否可以仿真計(jì)算雙環(huán)鎖相環(huán),如果可以具體怎么考慮,如果可以告訴我一些主環(huán)路環(huán)路帶寬的知識(shí)就更好了.

2019-03-07 10:34:03

鎖相環(huán)在很多領(lǐng)域都得到了廣泛應(yīng)用。本文給出了一款全芯片集成鎖相環(huán)電路設(shè)計(jì),其工作輸出頻率范圍在50M 到150M 之間,抖動(dòng)在150ps 以?xún)?nèi),工作電壓為2.5 伏,該芯片采用了0.2

2008-08-15 12:35:05 27

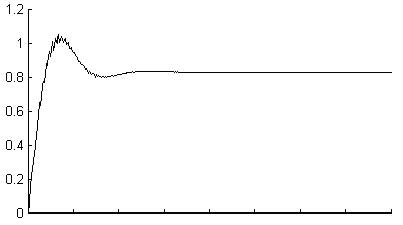

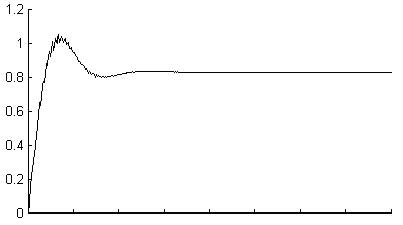

27 根據(jù)虛擬無(wú)線(xiàn)電技術(shù)的特點(diǎn)和鎖相環(huán)的基本原理,提出一種適于計(jì)算機(jī)軟件化實(shí)現(xiàn)的鎖相環(huán)數(shù)學(xué)模型,分析不同參數(shù)對(duì)鎖相環(huán)捕獲和跟蹤性能的影響,得出不同情況下參數(shù)設(shè)定的基

2008-08-15 12:36:19 101

101

鎖相環(huán)設(shè)計(jì)仿真與應(yīng)用:PLL Performance, Simulation, and Design3rd EditionI would like to thank the following people for their as

2008-08-16 10:14:53 75

75 一、實(shí)驗(yàn)?zāi)康?、掌握模擬鎖相環(huán)的組成及工作原理。2、學(xué)習(xí)用集成鎖相環(huán)構(gòu)成鎖相解調(diào)電路。3、學(xué)習(xí)用集成鎖相環(huán)構(gòu)成鎖相倍頻電路。

二、鎖相環(huán)路的基本原理

2009-03-22 11:44:37 127

127 以TRAC020LH 完全可重配置模擬器件和TRAC 開(kāi)發(fā)軟件為基礎(chǔ),設(shè)計(jì)模擬鎖相環(huán);給出仿真結(jié)果和利用PIC 單片機(jī)對(duì)器件進(jìn)行配置的應(yīng)用電路。該鎖相環(huán)成功應(yīng)用于逆變器的頻率跟蹤,性能

2009-04-15 11:42:39 11

11 以TRAC020LH 完全可重配置模擬器件和TRAC 開(kāi)發(fā)軟件為基礎(chǔ),設(shè)計(jì)模擬鎖相環(huán);給出仿真結(jié)果和利用PIC 單片機(jī)對(duì)器件進(jìn)行配置的應(yīng)用電路。該鎖相環(huán)成功應(yīng)用于逆變器的頻率跟蹤,性能

2009-05-15 15:38:05 6

6 智能全數(shù)字鎖相環(huán)的設(shè)計(jì):在FPGA片內(nèi)實(shí)現(xiàn)全數(shù)字鎖相環(huán)用途極廣。本文在集成數(shù)字鎖相環(huán)74297的基礎(chǔ)上進(jìn)行改進(jìn),設(shè)計(jì)了鎖相狀態(tài)檢測(cè)電路,配合CPU對(duì)環(huán)路濾波參數(shù)進(jìn)行動(dòng)態(tài)智能配

2009-06-25 23:32:57 72

72 鎖相環(huán)的性能,仿真和設(shè)計(jì)(第3版):

PLL BASICS ......9CHAPTER 1 BASIC PLL OVERVIEW .....11CHAPTER 2 THE CHARGE PUMP

2009-07-25 16:56:22 0

0 鎖相環(huán)電路的設(shè)計(jì):

2009-07-25 17:05:36 0

0 鎖相環(huán)設(shè)計(jì)舉例:鎖相環(huán)設(shè)計(jì)主要包括:確定所需環(huán)的類(lèi)型,選擇適當(dāng)?shù)膸挘赋鱿M姆€(wěn)定度。下面將舉例說(shuō)明要滿(mǎn)足這些設(shè)計(jì)要求而常用的基本方法。

2009-09-05 08:51:42 105

105 基于虛擬磁鏈和鎖相環(huán)的無(wú)電網(wǎng)電壓傳感器并網(wǎng)逆變器的研究:為了提高并網(wǎng)逆變器的可靠性和抗電網(wǎng)電壓波動(dòng),同時(shí)進(jìn)一步降低并網(wǎng)逆變器的成本,提出了一種基于鎖相環(huán)和虛

2010-02-18 13:16:58 42

42 在分析鎖相環(huán)工作原理的基礎(chǔ)上,利用傳遞函數(shù)法建立了鎖相環(huán)跟蹤誤差的二階等效模型,并對(duì)鎖相環(huán)的動(dòng)態(tài)頻相跟蹤特性進(jìn)行了理論分析.利用MATLAB構(gòu)建了鎖相環(huán)的仿真

2010-03-01 18:14:11 32

32 本文介紹鎖相環(huán)及其頻率跟蹤的基本原理,給出二階鎖相環(huán)和四階鎖相環(huán)的設(shè)計(jì)依據(jù)。在此基礎(chǔ)上,對(duì)四階鎖相環(huán)實(shí)現(xiàn)頻率跟蹤的轉(zhuǎn)換時(shí)間進(jìn)行了仿真,就如何減小頻率跟蹤的轉(zhuǎn)換時(shí)間

2010-07-29 16:28:14 44

44 CD4046鎖相環(huán)的介紹和應(yīng)用電路

鎖相的意義是相位同步的自動(dòng)控制,能夠完

2006-04-16 17:58:36 16126

16126

鎖相環(huán)原理

鎖相環(huán)路是一種反饋電路,鎖相環(huán)的英文全稱(chēng)是Phase-Locked Loop,簡(jiǎn)稱(chēng)PLL。其作用是使得電路上的時(shí)鐘和某一外部時(shí)鐘的相位同步。因鎖相環(huán)可以

2007-08-21 14:46:04 5484

5484 鎖相環(huán)電路圖

2008-02-25 21:48:30 4337

4337

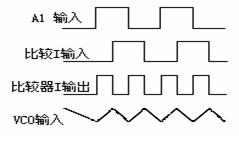

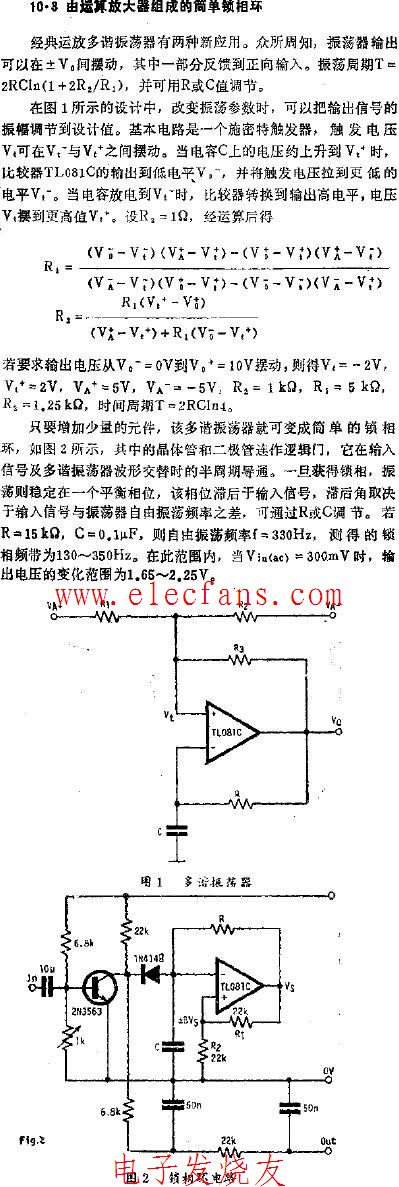

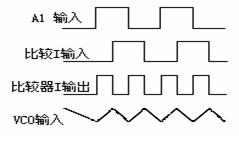

過(guò)零比較和鎖相環(huán)相位比較器電路原理圖如圖

2008-04-03 13:19:19 10158

10158

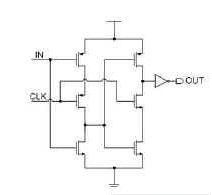

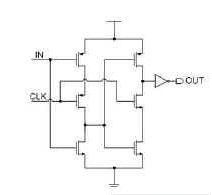

應(yīng)用于鎖相環(huán)的脈寬調(diào)整電路的設(shè)計(jì)

前言

在鎖相環(huán)PLL、DLL和時(shí)鐘數(shù)據(jù)恢復(fù)電路CDR等電路的應(yīng)用中,人們普遍要求輸出時(shí)鐘信號(hào)有50%的占空比,以便在時(shí)鐘上升及下

2008-10-16 08:59:42 1504

1504

摘要: 以TRAC020LH完全可重配置模擬器件和TRAC開(kāi)發(fā)軟件為基礎(chǔ),設(shè)計(jì)模擬鎖相環(huán);給出仿真結(jié)果和利用PIC單片機(jī)對(duì)器件進(jìn)行配置的應(yīng)用電路。該鎖相環(huán)成功應(yīng)用于逆變

2009-06-20 11:48:40 1328

1328

摘要: 在FPGA片內(nèi)實(shí)現(xiàn)全數(shù)字鎖相環(huán)用途極廣。本文在集成數(shù)字鎖相環(huán)74297的基礎(chǔ)上進(jìn)行改進(jìn),設(shè)計(jì)了鎖相狀態(tài)檢測(cè)電路,配合CPU對(duì)環(huán)路濾波參數(shù)進(jìn)行動(dòng)態(tài)智

2009-06-20 12:39:32 1760

1760

鎖相環(huán)(PLL),鎖相環(huán)(PLL)是什么意思

PLL的概念

我們所說(shuō)的PLL。其

2010-03-23 10:47:48 6368

6368 數(shù)字鎖相環(huán)(DPLL),數(shù)字鎖相環(huán)(DPLL)是什么?

背景知識(shí):

隨著數(shù)字電路技術(shù)的發(fā)展,數(shù)字鎖相環(huán)在調(diào)制解調(diào)、頻率合成、FM 立體聲解碼、彩色副

2010-03-23 15:06:21 6110

6110 模擬鎖相環(huán),模擬鎖相環(huán)原理解析

背景知識(shí):

鎖相技術(shù)是一種相位負(fù)反饋控制技術(shù),它利用環(huán)路的反饋原理來(lái)產(chǎn)生新的頻率點(diǎn)。它的主要

2010-03-23 15:08:20 6264

6264 為了達(dá)到與電源電壓同步的目的,除了可以使用鎖相同步電路外,還可以實(shí)時(shí)檢測(cè)電源電壓的過(guò)零點(diǎn)和頻率,根據(jù)過(guò)零點(diǎn)和

2010-09-28 16:47:02 3158

3158

電荷泵鎖相環(huán)的鎖定指示電路設(shè)計(jì),常用的方法是在PFD 電路中通過(guò)檢測(cè)經(jīng)分頻后的參考輸入和本振反饋信 號(hào)的相位誤差來(lái)實(shí)現(xiàn),當(dāng)相位誤差超過(guò)某個(gè)鎖定檢測(cè)窗口時(shí),鎖相環(huán)電路就上報(bào)失鎖告警。由于數(shù)字鎖定指示電路 設(shè)計(jì)簡(jiǎn)單,易于被監(jiān)控而被廣泛應(yīng)用。在實(shí)際的

2011-03-16 10:20:51 59

59 目錄: 基礎(chǔ)理論 環(huán)路的性能 電路實(shí)解 鎖相環(huán)在手機(jī)中的應(yīng)用

2011-05-02 11:05:01 474

474 鎖相環(huán)英文為PLL,即PLL鎖相環(huán)。可以分為模擬鎖相環(huán)和數(shù)字鎖相環(huán)。兩種分類(lèi)的鎖相環(huán)原理有較大區(qū)別,通過(guò)不同的鎖相環(huán)電路實(shí)現(xiàn)不同的功能。

2011-10-26 12:40:28

電子發(fā)燒友網(wǎng)站提供《第五版鎖相環(huán)設(shè)計(jì)、仿真與應(yīng)用(中文版).txt》資料免費(fèi)下載

2014-11-06 17:25:10 0

0 有關(guān)鎖相環(huán)的部分資料,對(duì)制作鎖相環(huán)有一定的幫助。

2015-10-29 14:16:55 70

70 如何設(shè)計(jì)并調(diào)試鎖相環(huán)(PLL)電路 pdf

2016-01-07 16:20:08 0

0 基于鎖相環(huán)的滯后超前環(huán)路濾波器的設(shè)計(jì)與仿真,設(shè)計(jì)方案。技術(shù)指標(biāo)、電路等。

2016-05-24 10:03:05 13

13 一種改進(jìn)的無(wú)鎖相環(huán)FBD諧波電流檢測(cè)方法_王清亮

2017-01-05 15:24:15 2

2 一、設(shè)計(jì)目標(biāo) 基于鎖相環(huán)的理論,以載波恢復(fù)環(huán)為依托搭建數(shù)字鎖相環(huán)平臺(tái),并在FPGA中實(shí)現(xiàn)鎖相環(huán)的基本功能。 在FPGA中實(shí)現(xiàn)鎖相環(huán)的自動(dòng)增益控制,鎖定檢測(cè),鎖定時(shí)間、失鎖時(shí)間的統(tǒng)計(jì)計(jì)算,多普勒頻偏

2017-10-16 11:36:45 19

19 為了能夠有效地治理諧波,提高電力系統(tǒng)中諧波信息的檢測(cè)精度,提出了自適應(yīng)鎖相環(huán)的分次諧波檢測(cè)優(yōu)化算法。首先,研究了改進(jìn)自適應(yīng)鎖相環(huán)的設(shè)計(jì)方法,并且構(gòu)造了相應(yīng)的數(shù)學(xué)模型;其次,設(shè)計(jì)了分次諧波檢測(cè)優(yōu)化算法

2017-10-30 16:16:15 11

11 針對(duì)傳統(tǒng)數(shù)字鎖相環(huán)存在的反饋滯后造成系統(tǒng)動(dòng)、靜態(tài)性能退化的問(wèn)題,提出一種消除反饋滯后一拍的方法,以無(wú)反饋滯后理想數(shù)字鎖相環(huán)為參考模型,利用數(shù)字鎖相環(huán)當(dāng)前輸出與上一時(shí)刻輸出,計(jì)算得到與理想數(shù)字鎖相環(huán)

2018-01-02 10:30:41 9

9 鎖相環(huán)(PLL)是模擬電路中的一個(gè)重要模塊,本文研究的是廣泛使用的電荷泵型鎖相環(huán)(CPPLL)。鎖相環(huán)電路通過(guò)比較參考輸入和輸出反饋信號(hào)的頻率/相位,并將此特征轉(zhuǎn)化為電壓,然后通過(guò)與壓控振蕩器

2019-06-14 08:03:00 4590

4590

參考信號(hào)代替鎖相環(huán)的無(wú)鎖相環(huán)單相檢測(cè)方法,能同時(shí)檢測(cè)出基波有功、基波無(wú)功和諧波,具有延時(shí)小、受頻差、電壓畸變影響小、可自動(dòng)跟蹤電源頻率的特性。文中結(jié)論的正確性在于可靠提取低頻信號(hào),討論了采用低通濾波器和積分法提取低頻信號(hào)的特性

2019-07-24 08:00:00 8

8 過(guò)零點(diǎn)的準(zhǔn)確檢測(cè)變得異常關(guān)鍵,因?yàn)槠渲档拇_定直接決定著系統(tǒng)計(jì)算的電網(wǎng)電壓頻率的跟蹤效果和補(bǔ)償電流注入電網(wǎng)的時(shí)間,進(jìn)而直接影響到靜止型無(wú)功功率補(bǔ)償器對(duì)電網(wǎng)補(bǔ)償?shù)臏?zhǔn)確性和實(shí)時(shí)性,即同步性。本文充分利用現(xiàn)代電子電路設(shè)

2020-07-16 18:54:00 0

0 ,為了減小壓控振蕩器控制電壓的紋波,它采用了二階無(wú)源環(huán)路濾波器,這樣就構(gòu)成了三階電荷泵鎖相環(huán)。系統(tǒng)級(jí)設(shè)計(jì)與仿真驗(yàn)證是鎖相環(huán)設(shè)計(jì)的第一步和關(guān)鍵的一步。本文對(duì)一種用作時(shí)鐘倍頻器的三階電荷泵鎖相環(huán)進(jìn)行了系統(tǒng)級(jí)設(shè)計(jì)與仿真驗(yàn)證,仿真環(huán)境采用SIMULINK。

2020-07-24 09:59:51 4279

4279

用于閉環(huán)跟蹤電路。鎖相環(huán)在工作的過(guò)程中, 當(dāng)輸出信號(hào)的頻率與輸入信號(hào)的頻率相等時(shí), 輸出電壓與輸入電壓保持固定的相位差值, 即輸出電壓與輸入電壓的相位被鎖住, 這就是鎖相環(huán)名稱(chēng)的由來(lái)。

2020-08-06 17:58:25 26

26 電荷泵鎖相環(huán)的鎖定檢測(cè)電路設(shè)計(jì),包括模擬鎖定檢測(cè)和數(shù)字鎖定檢測(cè)兩種方法。其中,模擬檢測(cè)電路采用經(jīng)鑒頻鑒相器PFD 輸出的相位誤差,產(chǎn)生脈沖信號(hào)對(duì)外部電容進(jìn)行充電和放電,需要較長(zhǎng)的時(shí)間以達(dá)到穩(wěn)定的電平

2020-08-24 14:11:38 4386

4386

因鎖相環(huán)可以實(shí)現(xiàn)輸出信號(hào)頻率對(duì)輸入信號(hào)頻率的自動(dòng)跟蹤,所以鎖相環(huán)通常用于閉環(huán)跟蹤電路。鎖相環(huán)在工作的過(guò)程中,當(dāng)輸出信號(hào)的頻率與輸入信號(hào)的頻率相等時(shí),輸出電壓與輸入電壓保持固定的相位差值,即輸出電壓與輸入電壓的相位被鎖住,這就是鎖相環(huán)名稱(chēng)的由來(lái)。

2020-11-03 14:55:49 16784

16784

本文充分利用現(xiàn)代電子電路設(shè)計(jì)軟件的方便條件,在Protel 99SE仿真分析的基礎(chǔ)之上,設(shè)計(jì)了一種無(wú)鎖相環(huán)的交流電壓全周期過(guò)零檢測(cè)電路,不僅設(shè)計(jì)簡(jiǎn)單,而且其準(zhǔn)確性也得到了實(shí)驗(yàn)的驗(yàn)證,有一定的實(shí)用價(jià)值。同時(shí),以 Protel 99SE為電路仿真的手段有一定實(shí)際意義。

2021-02-18 09:54:47 5356

5356

鎖相環(huán)路是一種反饋控制電路,簡(jiǎn)稱(chēng)鎖相環(huán)(PLL,Phase-Locked Loop)。鎖相環(huán)的特點(diǎn)是:利用外部輸入的參考信號(hào)控制環(huán)路內(nèi)部振蕩信號(hào)的頻率和相位。

2022-03-29 09:54:55 15826

15826 因鎖相環(huán)可以實(shí)現(xiàn)輸出信號(hào)頻率對(duì)輸入信號(hào)頻率的自動(dòng)跟蹤,所以鎖相環(huán)通常用于閉環(huán)跟蹤電路。鎖相環(huán)在工作的過(guò)程中,當(dāng)輸出信號(hào)的頻率與輸入信號(hào)的頻率相等時(shí),輸出電壓與輸入電壓保持固定的相位差值,即輸出電壓與輸入電壓的相位被鎖住,這就是鎖相環(huán)名稱(chēng)的由來(lái)。

2022-05-10 14:25:19 8969

8969 模擬鎖相環(huán)和數(shù)字鎖相環(huán)的主要區(qū)別在于它們的控制方式不同。模擬鎖相環(huán)是通過(guò)模擬電路來(lái)控制頻率和相位,而數(shù)字鎖相環(huán)是通過(guò)數(shù)字信號(hào)處理技術(shù)來(lái)控制頻率和相位。此外,模擬鎖相環(huán)的精度較低,而數(shù)字鎖相環(huán)的精度較高。

2023-02-15 13:47:53 6625

6625 鎖相環(huán)電路,是調(diào)頻電路的重要組成之一,鎖相環(huán)電路的原理的認(rèn)識(shí)是DDS學(xué)習(xí)的一個(gè)重點(diǎn)之一。

2023-07-24 15:37:05 4645

4645

硬件鎖相環(huán)電路怎么設(shè)計(jì)?硬件鎖相環(huán)電路的設(shè)計(jì)通常包括以下步驟。

2023-08-08 11:16:46 1534

1534 以及各種時(shí)鐘信號(hào),下面將從這些方面逐一介紹。 一、鎖相環(huán) 鎖相環(huán)(Phase-Locked Loop, PLL)是一種基于反饋控制的電路,由比較器、低通濾波器、振蕩器和除法器等組成。輸入信號(hào)和振蕩器產(chǎn)生的參考信號(hào)經(jīng)過(guò)比較器比較,將誤差信號(hào)通過(guò)低通濾波器進(jìn)

2023-09-02 14:59:24 4879

4879 信號(hào)倍頻。在本文中,我們將詳細(xì)探討鎖相環(huán)如何實(shí)現(xiàn)倍頻。 鎖相環(huán)的基本原理 在介紹鎖相環(huán)如何實(shí)現(xiàn)倍頻之前,我們先來(lái)回顧一下鎖相環(huán)的基本原理。鎖相環(huán)電路主要由三個(gè)部分組成:相位檢測(cè)器(Phase Detector, PD)、環(huán)路濾波器(Loop Filter, LF)和振蕩器(Voltage Cont

2023-09-02 14:59:37 5119

5119 鎖相環(huán)可不可以用于倍頻非周期信號(hào)? 鎖相環(huán)(Phase Locked Loop,簡(jiǎn)稱(chēng)PLL)是一種常用的電子電路,可以用來(lái)鎖定輸入信號(hào)的相位和頻率。它具有廣泛的應(yīng)用領(lǐng)域,如通信系統(tǒng)、數(shù)字信號(hào)處理

2023-09-02 15:12:37 1173

1173 pll鎖相環(huán)的作用 pll鎖相環(huán)的三種配置模式? PLL鎖相環(huán)是現(xiàn)代電子技術(shù)中廣泛應(yīng)用的一種電路,它的作用是將一個(gè)特定頻率的輸入信號(hào)轉(zhuǎn)換為固定頻率的輸出信號(hào)。PLL鎖相環(huán)的三種配置模式分別為

2023-10-13 17:39:48 5285

5285 軟件鎖相環(huán)在頻率突變時(shí)鎖不住 鎖相環(huán)無(wú)法鎖定怎么辦?? 鎖相環(huán)(PLL)是一種用于在電路中生成穩(wěn)定頻率的技術(shù)。它是在1960年代開(kāi)發(fā)的,并被廣泛應(yīng)用于通信、雷達(dá)、衛(wèi)星技術(shù)等領(lǐng)域中。鎖相環(huán)的主要作用

2023-10-13 17:39:58 3086

3086 鎖相環(huán)在相位檢測(cè)中的應(yīng)用? 鎖相環(huán)(PLL)是一種電子技術(shù)中廣泛應(yīng)用的電路,用于調(diào)整一個(gè)輸出信號(hào)的相位來(lái)精確匹配一個(gè)參考信號(hào)。鎖相環(huán)在各種不同的應(yīng)用領(lǐng)域都有著廣泛的應(yīng)用,例如通信系統(tǒng)、控制系統(tǒng)、測(cè)量

2023-10-29 11:35:19 1739

1739 當(dāng)鎖相環(huán)無(wú)法鎖定時(shí),該怎么處理的呢?如何解決鎖相環(huán)無(wú)法鎖定? 鎖相環(huán)作為一種常見(jiàn)的電路設(shè)計(jì),具有廣泛的應(yīng)用領(lǐng)域。然而,在一些情況下,由于種種原因,鎖相環(huán)可能無(wú)法正常鎖定,這時(shí)需要進(jìn)行一系列的測(cè)試

2023-10-30 10:16:33 3646

3646 、無(wú)線(xiàn)通信、數(shù)據(jù)轉(zhuǎn)換、模擬信號(hào)處理等眾多應(yīng)用領(lǐng)域。然而,頻繁的開(kāi)關(guān)PLL的電源可能對(duì)其造成不良影響。 PLL芯片是由多個(gè)模擬電路和數(shù)字電路組成的。在PLL芯片中,鎖相環(huán)控制器是最重要的組成部分。這個(gè)控制器包含一個(gè)相位檢測(cè)器

2023-10-30 10:16:40 1293

1293 應(yīng)用。本文將重點(diǎn)介紹載波同步電路中的鎖相環(huán)設(shè)計(jì)的關(guān)鍵點(diǎn)。 1. 基本原理 PLL 的基本原理是將一個(gè)輸入信號(hào)與一個(gè)內(nèi)部參考頻率比較,通過(guò)不斷調(diào)整內(nèi)部振蕩電路的頻率和相位,使得輸入信號(hào)和參考信號(hào)在相位上保持一致。通常情況下,PLL 由相位檢測(cè)器、環(huán)路濾波

2023-10-30 10:51:28 1376

1376

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論