本文介紹了TDA7513的射頻電路設計方法,根據實際設計經驗提出了提高射頻電路EMC特性和噪聲特性的設計方法和措施,并指出了射頻電路性能測試的注意要點。

2015-03-30 13:49:30 8447

8447 今天,我要談談在測試電源性能時需要考慮的另一個重要指標:噪聲測量。 電源噪聲從何而來? 電源噪聲的生成有多種不同的來源。與任何一款放大器一樣,電源也會產生各種不同類型的噪聲,而開關模式設計還需要處理

2018-03-27 09:13:33 11720

11720

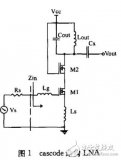

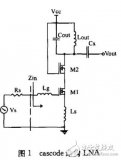

射頻LNA設計要求:低噪聲放大器(LNA)作為射頻信號傳輸鏈路的第一級,它的噪聲系數特性決定了整個射頻電路前端的噪聲性能,因此作為高性能射頻接收電路的第一級LNA的設計必須滿足。

2015-03-30 11:40:10 23294

23294

電源線是EMI 出入電路的重要途徑。通過電源線,外界的干擾可以傳入內部電路,影響RF電路指標。為了減少電磁輻射和耦合,要求DC-DC模塊的一次側、二次側、負載側環路面積最小。電源電路不管形式有多復雜,其大電流環路都要盡可能小。電源線和地線總是要很近放置。

2017-08-09 09:29:55 3262

3262

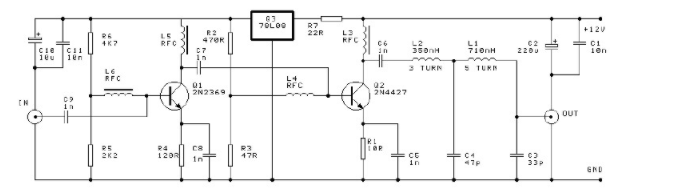

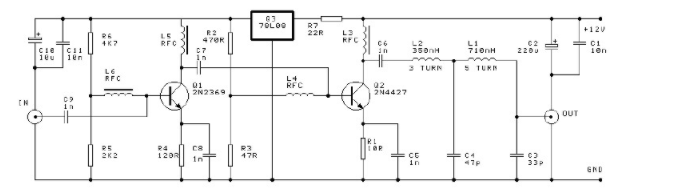

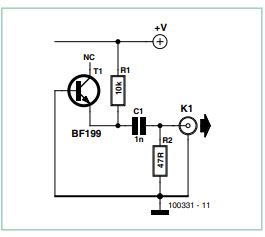

這是一個250mW射頻功率放大電路項目。該電路設計用于將大約7mW寬帶FM發射機的輸出放大到大約250mW的最終電平。通用12V直流電源可用于操作此射頻放大器電路。

2022-06-10 15:31:19 8877

8877

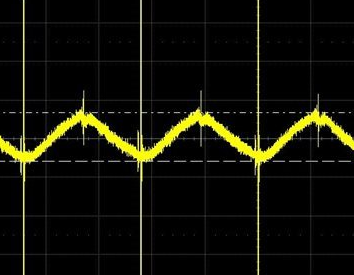

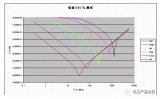

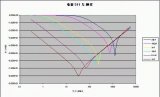

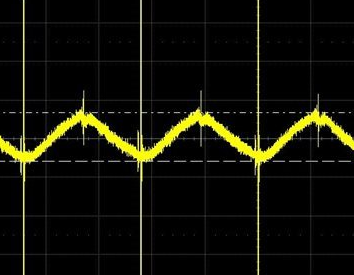

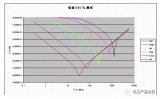

Q:我想問一個噪聲惡化問題,之前做PA在放大一個單音信號,從頻譜儀上看,間隔基波幾十兆的頻率會有一個小山坡(鼓包)一樣的雜波,RBW改小以后發現并不是單音雜散,有點類似于底噪惡化,不是外部電源引入的,調整匹配也無法消除。這種間隔基波的底噪惡化是什么原因呀?類似于紅色曲線這樣的呈現。

2022-09-02 10:43:40 3142

3142 在不需要外加電源的條件下,就可以顯示其特性的電子元件。射頻無源器件有哪些?無源器件主要包括電阻,電容,電感,轉換器,漸變器,匹配網絡,諧振器,濾波器,混頻器和開關等。

2023-07-19 09:33:09 2224

2224

今天我們一起來看一下射頻電路中的那些無源器件。和數字和低頻電路類似,射頻電路也分為無源器件和有源器件

2023-10-08 16:03:25 1661

1661

每個電路設計人員都使用不同的技術來消除電路設計中的噪聲。在構建與音頻或電力電子相關的任何電路時,噪聲是主要問題之一,但是今天,我們將制造一個會產生噪聲的電路。一種特殊類型的噪聲,表示為白噪聲。

2022-10-28 11:57:39 11632

11632

)相結合,能夠為任何RF系統設計奠定穩固的基礎。盡管實際設計中還會存在降低系統性能指標的其它因素,但是,擁有一個“無噪聲”的電源是優化系統性能的基本要素.

2019-08-29 07:30:00

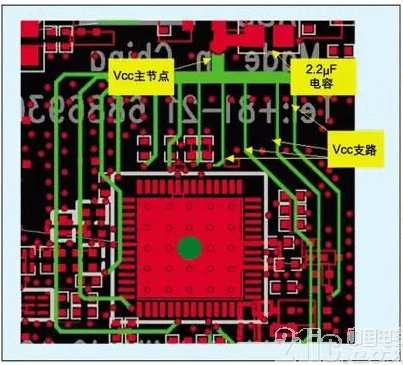

受到噪聲的干擾。 良好的電源去耦技術與嚴謹的PCB布局、Vcc引線(星型拓撲)相結合,能夠為任何RF系統設計奠定穩固的基礎。盡管實際設計中還會存在降低系統性能指標的其它因素,但是,擁有一個“無噪聲”的電源是優化系統性能的基本要素.

2019-05-06 08:00:00

誰能幫忙提供點關于E/DE類射頻電源設計的相關資料啊,求眾大神幫忙

2014-10-21 16:03:37

關于TD-SCDMA射頻測試內容,總結的太棒了

2021-05-08 08:50:01

關于地線回路與射頻接地的知識點總結的太棒了

2021-09-30 08:04:08

開關電源PCB排版與數字電路PCB排版的區別在哪里?開關電源PCB排版技術要點有哪些?

2021-04-25 09:38:28

噪聲抑制電路有哪些主要技術參數?CPLD有哪些設計要點?

2021-06-04 07:02:35

其它可能帶來噪聲的走線隔離開來。

此外,要確保VCO的電源已得到充分去耦,由于VCO的RF輸出往往是一個相對較高的電平,VCO輸出信號很容易干擾其它電路,因此必須對VCO加以特別注意。事實上,VCO往往布放在RF

2023-05-16 15:20:41

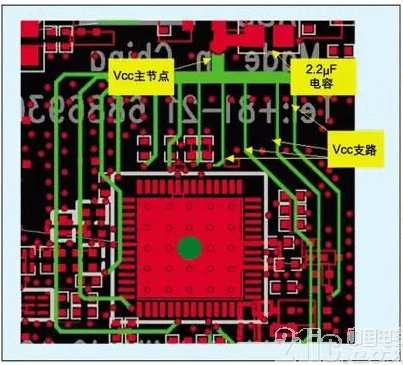

使用星型拓撲,則會減輕不同電源引腳之間的耦合。良好的電源去耦技術與嚴謹的PCB布局、Vcc引線(星型拓撲)相結合,能夠為任何RF系統設計奠定穩固的基礎。盡管實際設計中還會存在降低系統性能指標的其它因素,但是,擁有一個“無噪聲”的電源是優化系統性能的基本要素。

2021-11-30 07:00:00

你注意到電源對你的射頻系統的影響嗎?對于高性能的無線通信系統,電源對射頻的影響可能是“隱性”的,但卻不可忽視。小編收集整理了業界廣泛關注的幾條設計射頻電路電源的要點與經驗。一、電源線是EMI 出入

2019-07-08 08:04:55

的研究生教材,也可供從事射頻電路和系統設計工作的工程技術人員參考。

此書是作者20年射頻設計成與敗的設計經驗總結,理論知識和實踐經驗都很豐富。講解獨特,強調匹配和射頻接地。

獲取完整文檔資料可下載附件哦!!!!如果內容有幫助可以關注、點贊、評論支持一下哦~

2025-06-13 17:07:27

些頻點容易受到噪聲的干擾。 良好的電源去耦技術與嚴謹的PCB布局、Vcc引線(星型拓撲)相結合,能夠為任何RF系統設計奠定穩固的基礎。盡管實際設計中還會存在降低系統性能指標的其它因素,但是,擁有一個“無噪聲”的電源是優化系統性能的基本要素.

2018-11-20 10:50:19

``射頻電路作為設計電路是你遇到過或將會遇到的一個重要部分,相信大家一定都不會太陌生,那么射頻電路的電源設計有哪些要點呢?廢話不多說,不要“前奏”,我們直接進“主歌”:(1)電源線是EMI 出入電路

2017-08-20 11:14:15

容易受到噪聲的干擾。 良好的電源去耦技術與嚴謹的PCB布局、Vcc引線(星型拓撲)相結合,能夠為任何RF系統設計奠定穩固的基礎。盡管實際設計中還會存在降低系統性能指標的其它因素,但是,擁有一個“無噪聲”的電源是優化系統性能的基本要素。

2018-10-17 16:51:17

使用星型拓撲則會減輕不同電源引腳之間的耦合。良好的電源去耦技術與嚴謹的PCB布局、Vcc引線(星型拓撲)相結合,能夠為任何RF系統設計奠定穩固的基礎。盡管實際設計中還會存在降低系統性能指標的其它因素,但是,擁有一個“無噪聲”的電源是優化系統性能的基本要素。

2019-05-31 04:20:29

。 良好的電源去耦技術與嚴謹的PCB布局、Vcc引線(星型拓撲)相結合,能夠為任何RF系統設計奠定穩固的基礎。盡管實際設計中還會存在降低系統性能指標的其它因素,但是,擁有一個“無噪聲”的電源是優化系統性能的基本要素。

2018-09-29 09:21:17

印制電路板的抗干擾規劃關于減小系統電磁信息輻射具有重要的含義。射頻電路板的密度越來越高,射頻PCB印制電路板規劃的好壞對立干擾影響很大,同一電路,不同的射頻PCB印制電路板規劃結構,其功能目標會相差很大

2023-06-08 14:48:14

TOP1 射頻低噪聲放大器電路 射頻LNA設計要求:低噪聲放大器(LNA)作為射頻信號傳輸鏈路的第一級,它的噪聲系數特性決定了整個射頻電路前端的噪聲性能,因此作為高性能射頻接收電路的第一級LNA

2021-07-28 08:51:10

1、射頻LNA設計要求低噪聲放大器(LNA)作為射頻信號傳輸鏈路的第一級,它的噪聲系數特性決定了整個射頻電路前端的噪聲性能,因此作為高性能射頻接收電路的第一級LNA的設計必須滿足[1]:(1)較高

2019-06-20 07:41:39

在把射頻芯片或模塊集成到典型的嵌入式系統中時,設計人員必須面臨的一項常見任務是追蹤和消除噪聲和雜散信號。潛在的噪聲來源包括:開關電源、來自系統其它部分的數字噪聲、以及外部噪聲來源。在考慮噪聲時,還應

2019-06-10 07:08:32

上次,我發表了關于“如何測試電源設計”三篇文章中的第一篇:電源測試,效率測量,主要介紹有關測試的基礎知識,包括必要設備以及如何準備用于測試的電路等。此外,我還介紹了如何精確測量啟動時間、電流限值以及

2022-11-23 06:19:44

*通信測試設備 一般說明 ADF5001預分頻器是一個低噪聲、低功率、固定射頻分頻器塊,可用于將高達18GHz的頻率分成適合輸入到PLL IC(如ADF4156或ADF4106)的較低

2020-07-13 15:02:33

[導讀] 前文總結了單片機串口個人認為值得注意的一些要點,本文來梳理一下 I2C 總線的一些要點。這個題目有點大,本文對于 I2C 其實很多地方也沒整清楚,只為了與前文形成系列,如果大家...

2021-07-26 08:01:47

MSP430G2553時鐘系統要點總結時鐘總覽時鐘源的選用默認狀態控制寄存器例程個人總結的MSP430G2553各個模塊功能要點,主要側重于實用編程與理解。本章主要側重于第四部分寄存器的理解

2022-02-15 06:57:11

晶振電源電路原理圖設計要點PCB設計要點

2021-02-25 08:25:34

[摘要]隨著射頻集成電路(RFIC)中集成的元件不斷增多,噪聲耦合源也日益增多,使電源管理變得越來越重要。本文將描述電源噪聲可能對RFIC 性能造成的影響。雖然本文的例子是集成鎖相環(PLL)和電壓

2015-09-24 14:05:01

為何將電源濾波電路作為一個全頻段的噪聲衰減器?

2021-02-26 06:08:15

什么是射頻集成電路的電源管理? 隨著射頻集成電路(RFIC)中集成的元件不斷增多,噪聲耦合源也日益增多,使電源管理變得越來越重要。本文將描述電源噪聲可能對RFIC 性能造成的影響。雖然本文的例子

2019-07-30 07:00:05

設計奠定穩固的基礎。盡管實際設計中還會存在降低系統性能指標的其它因素,但是,擁有一個“無噪聲”的電源是優化射頻系統性能的基本要素。

2019-06-17 14:11:17

設計一個射頻電路需要考慮以下幾個方面: 信號傳輸線路:首先需要確定電路中信號的傳輸線路,例如使用微波或者激光等。 天線:天線是射頻電路中非常重要的組成部分之一,它的作用是將信號傳輸到目標設備

2023-04-21 11:31:06

直接影響著接收機的性能。另一方面,LNA的設計也是無線電設備相關電路設計中最具有挑戰性的內容之一。這主要表現在它同時需要滿足高增益、低噪聲、良好的輸入輸出匹配和在盡可能小的工作電流時的無條件穩定性。那么,大家知道我們該如何設計CDMA射頻前端低噪聲放大器電路嗎?

2019-08-01 06:34:15

上避免帶噪聲的大電流流過前級小信號地;單點接地,電源、模擬、數字電路分開接地;布板使用地平面層,最小化地線阻抗;開關電源輸出從最后一個濾波電容的地端引出電源地,避免從濾波電感前的電容的地端引出

2023-11-21 06:27:27

、模擬、數字電路分開接地;布板使用地平面層,最小化地線阻抗;開關電源輸出從最后一個濾波電容的地端引出電源地,避免從濾波電感前的電容的地端引出。 圖5:共模阻抗噪聲耦合示意圖開關管漏極開關電壓驅動

2018-12-29 10:10:32

最后一個濾波電容的地端引出電源地,避免從濾波電感前的電容的地端引出。 圖5:共模阻抗噪聲耦合示意圖開關管漏極開關電壓驅動的位移電流,通過初次級分布電容,次級電路,次級對大地與雜散電容,大地與初級

2017-10-19 23:34:27

/DC,開關穩壓器設計中的PCB板布局都是非常重要的。在此也再次強調一遍,開關電源是模擬電路(近年來還有“數字電源”),自身會產生噪聲,同時對噪聲也非常敏感。另外,由于開關噪聲會作為EMI對周邊產生影響

2018-12-03 14:24:36

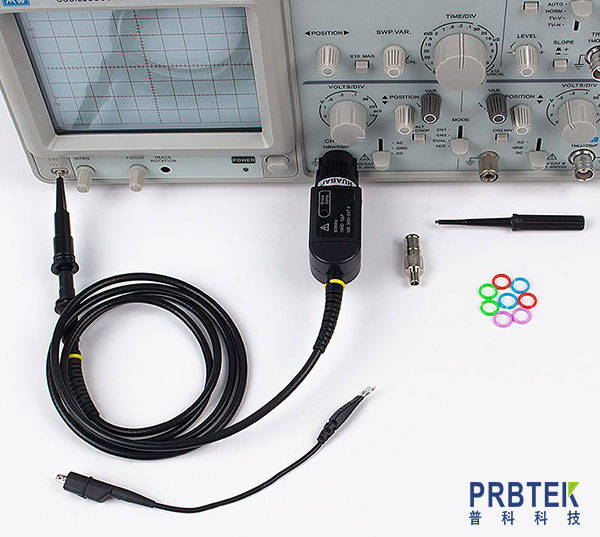

交流耦合檔位;

②帶寬限制選擇20MHz;

③將示波器探頭的地夾線去掉,換上彈簧接地環,用探針靠接電源的輸出端,接地環就近連接在裸露的地上,觀察輸出的波形。

以上是關于開關電源紋波與噪聲總結的一些內容了

2024-11-26 17:35:33

了八點開關電源PCB排版的基本要點。下面就為大家簡單總結一下這八個要點分別都是什么。要點1、旁路瓷片電容器的電容不能太大,而它的寄生串聯電感應盡量小,多個電容并聯能改善電容的阻抗特性;要點2、電感

2016-07-15 11:41:38

電源功率器件在 PCB 上正確的放置和走線將決定整個電源工作是否正常。設計人員首先要對開關電源功率器件上的電壓和電流的波形有一定的了解。中國IC交易網下面顯示一個降壓式開關電源功率電路元器件上的電流

2019-05-13 11:41:22

本文將探討實際的開關電源產生的噪聲。開關電源產生的噪聲首先,使用同步整流型降壓DC/DC轉換器的等效電路來了解一下開關電流的路徑。SW1為高邊開關,SW2為低邊開關。SW1導通(SW2為OFF

2018-11-29 14:47:35

本文將探討實際的開關電源產生的噪聲。開關電源產生的噪聲首先,使用同步整流型降壓DC/DC轉換器的等效電路來了解一下開關電流的路徑。SW1為高邊開關,SW2為低邊開關。SW1導通(SW2為OFF

2019-03-18 06:20:14

定制的一個開關電源,使用后,系統噪聲稍大,用手接觸開關電源金屬外殼,系統噪聲就正常了。開關電源外殼是接大地的。感覺是可能EMI導致的噪聲,目前無好的測試方案,無法證明。各位壇友有好的建議么?開關電源輸入接了一個電源濾波器。

2019-10-28 05:43:03

你注意到電源對你的射頻系統的影響嗎?對于高性能的無線通信系統,電源對射頻的影響可能是“隱性”的,但卻不可忽視。 怎么設計射頻電路電源?需要注意哪些事項呢?

2019-08-21 06:28:41

高頻RFID射頻電子電路設計的原理是什么?怎樣去設計一種射頻低噪聲放大器電路呢?

2021-10-18 08:42:39

、線性化等放大器的諸多知識點和設計方法。第4章對無源和有源混頻器進行詳細分析。第5童闡述射頻振蕩器原理,深入分析柑位噪聲和高Q振蕩電路,示范大量成熟的電路是本章的一個特點。關于射頻頻率綜合的最后·章重點

2025-06-13 17:46:06

無線通訊的噪聲干擾與驗證要點是什么?

2021-05-25 06:37:45

不斷進步。

文章總結了工作中的一些設計經驗,有利于提高射頻電路PCB的抗干擾能力,幫助射頻電路設計初學者少走不必要的彎路。

PCB射頻電路四大基礎特性

本文從射頻界面、小的期望信號、大的干擾信號、相鄰頻道的干擾四個方面

2024-08-20 11:44:32

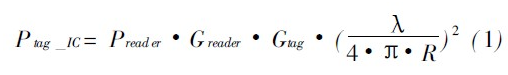

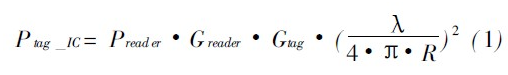

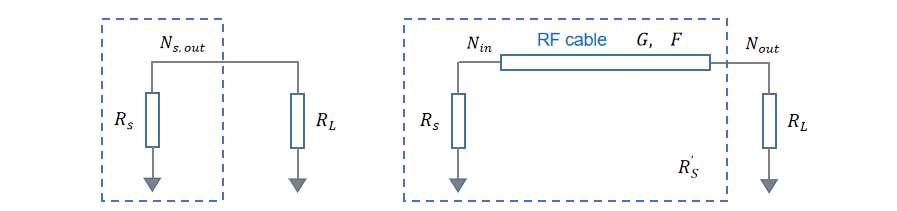

衰減信號和噪聲,不管怎樣,網絡的輸出端總會有來自網絡內部和前級的噪聲啊,不會只有將網絡等效成負載的信號源的內阻所產生的熱噪聲啊?(上傳了一張書上的圖,《射頻集成電路與系統》p100,圖4-18)

2012-11-13 20:42:59

的基礎。盡管實際設計中還會存在降低系統性能指標的其它因素,但是,擁有一個“無噪聲”的電源是優化系統性能的基本要素。

2019-08-20 16:09:26

請教一下各位pcb板上電源部分布局和走線的有哪些要點哦,可以把主板電源做紋波和噪聲盡可能的小,最好能提供一下實物的參考layout板學習哦,謝謝各位了

2014-10-24 15:08:06

請問射頻接收芯片結構選擇要點有哪些?

2021-10-12 09:26:13

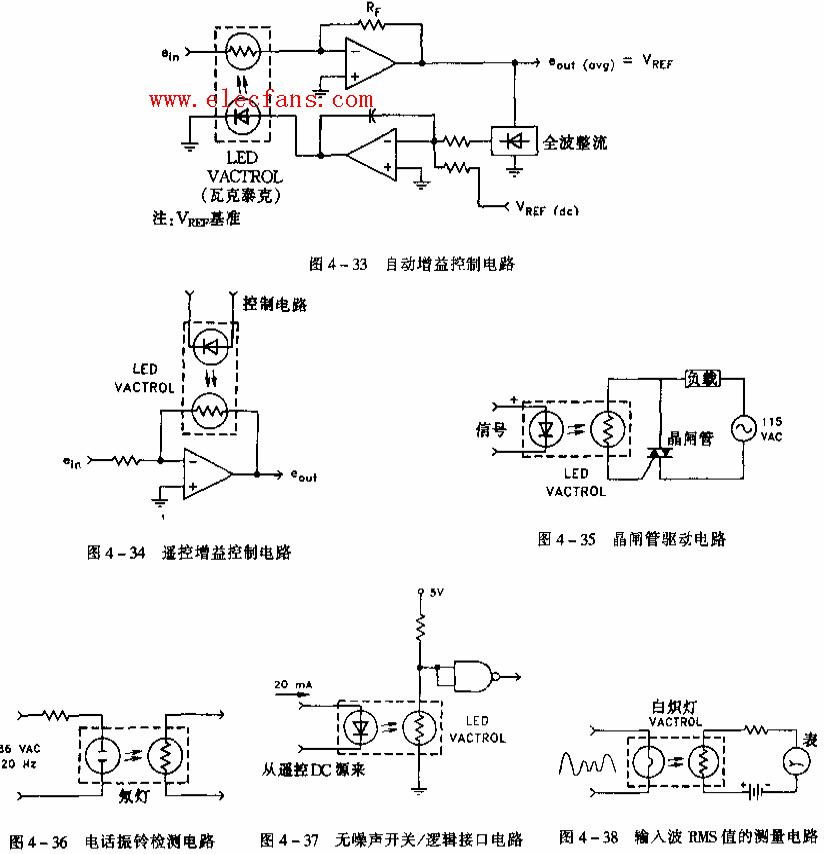

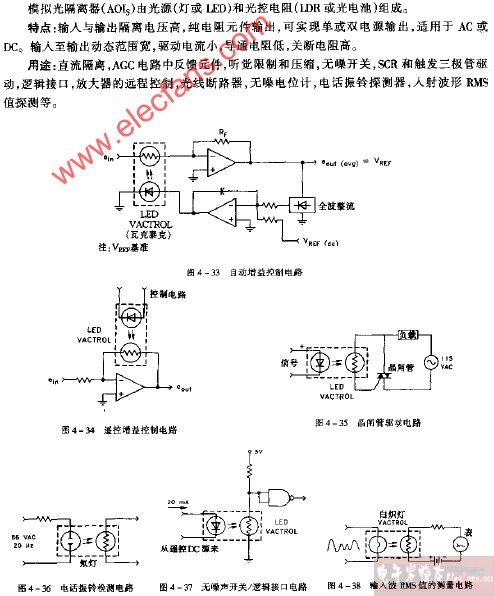

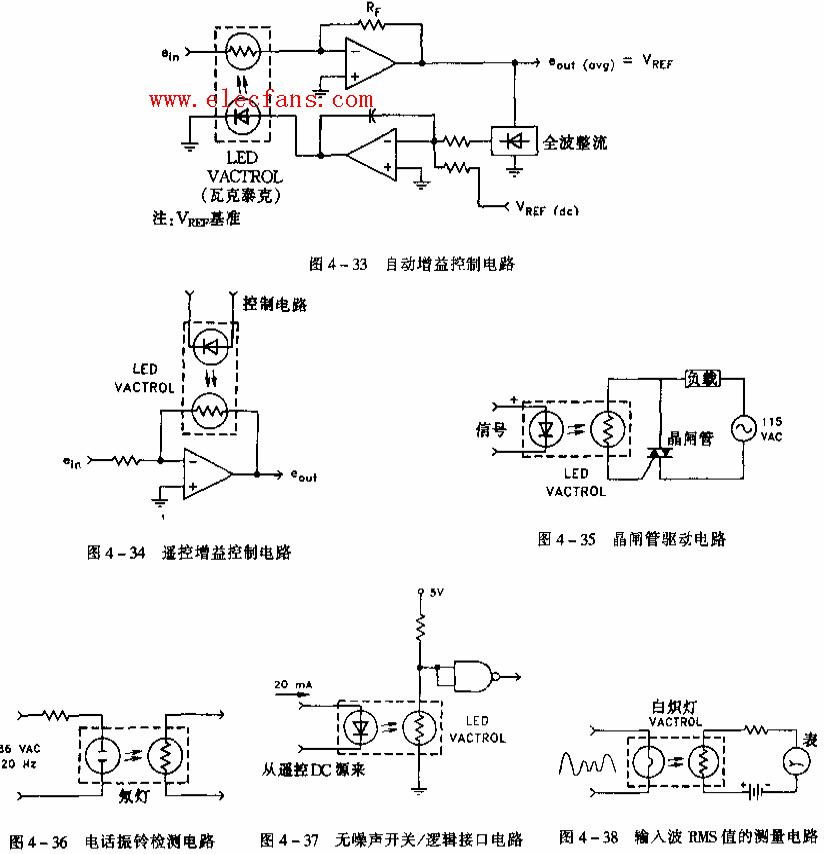

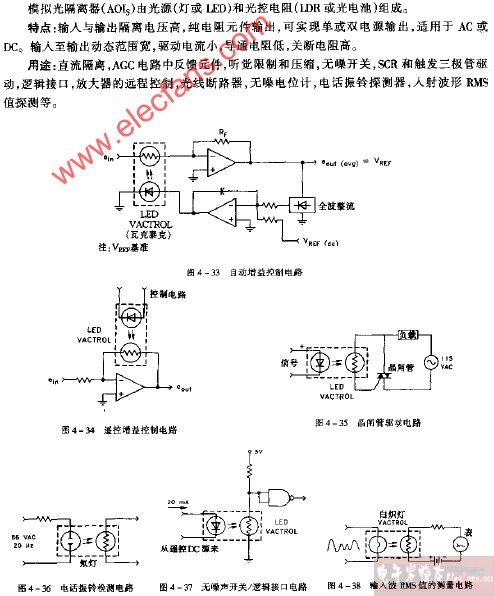

無噪聲開關邏輯接口電路

2008-05-15 09:51:37 979

979

無噪聲開關、邏輯接口電路圖

2009-06-30 10:03:19 460

460

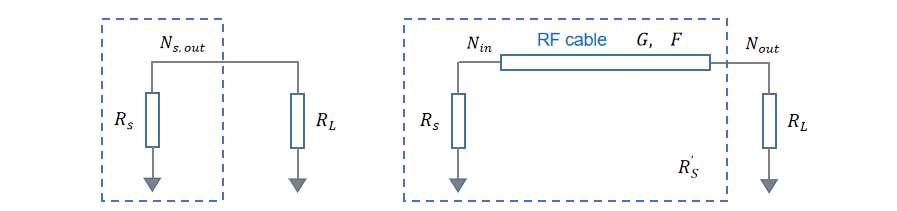

低功耗無源超高頻射頻識別應答器芯片的射頻電路

本文提出了一種符合ISO/IEC18000-6B標準的高性能低功耗無源超高頻(UHF)射頻識別(RFID)應答器芯片的射頻電路。該射

2010-01-26 11:14:03 2253

2253

LED驅動電源設計須做到調試前計算,調試時測量,調試后老化以下整理了5個要點供參考

1、LED電流大小

2010-07-19 16:00:09 604

604 無噪聲電源并非是偶然設計出來的。一種好的電源布局是在設計時最大程度的縮短實驗時間。花費數分鐘甚至是數小時的時間來仔細查看電源布局,便可以省去數

2010-08-14 08:45:31 613

613

無噪聲的的功放電源電路

工作原理:交流電源輸入經T1進行濾波后分成兩路輸出,一路去降壓變壓器T3,在T3的初

2010-10-03 15:48:20 3710

3710 重點討論芯片級和PCB級射頻電路設計和測試中經常遇到的阻抗匹配、接地、單端到差分轉換、容差分析、噪聲與增益和靈敏度、非線性和雜散波等關鍵問題。

2012-02-23 15:30:54 0

0 文中的電路是關于采用單端15V 輸入電源的低噪聲12V 電源電路圖。 LTC3260 是一款低噪聲、雙極性輸出電源,包括一個兼具正和負 LDO 穩壓器的負輸出充電泵。充電泵在一個 4.5V 至 32V 的寬

2012-06-11 11:22:16 4346

4346

高一物理知識要點全面總結高一物理知識要點全面總結

2016-02-15 08:15:13 0

0 前言: 噪聲是模擬電路設計的一個核心問題,它會直接影響能從測量中提取的信息量,以及獲得所需信息的經濟成本。遺憾的是,關于噪聲有許多混淆和誤導信息,可能導致性能不佳、高成本的過度設計或資源使用效率低下。本文闡述關于模擬設計中噪聲分析的11個由來已久的誤區。

2017-04-26 16:47:40 1740

1740

小代 2017年08月11日 全部文章 37 0 射頻電路作為設計電路是你遇到過或將會遇到的一個重要部分,相信大家一定都不會太陌生,那么射頻電路的電源設計有哪些要點呢?廢話不多說,不要“ 前奏

2017-11-29 20:37:36 959

959

你注意到電源對你的射頻系統的影響嗎?對于高性能的無線通信系統,電源對射頻的影響可能是“隱性”的,但卻不可忽視。這里收集整理了業界廣泛關注的幾條設計射頻電路電源的要點與經驗,小伙伴們轉走不謝.

2017-12-22 09:59:17 15031

15031

隨著集成電路制造工藝水平的迅猛發展,不同的功能模塊,比如數字,模擬,射頻電路集成在一塊芯片上。然而電源噪聲會大大削弱對噪聲敏感的電路模塊的性能,如改變VCO輸出信號的頻率和相位,所以必須通過電源管理

2018-02-23 11:41:48 0

0 無噪聲電源并非是偶然設計出來的。一種好的電源布局是在設計時最大程度的縮短實驗時間。花費數分鐘甚至是數小時的時間來仔細查看電源布局,便可以省去數天的故障排查時間。圖 1 顯示的是電源內部一些主要噪聲敏感型電路的結構圖。

2018-04-16 08:44:25 23

23 本文檔的主要內容詳細介紹的是射頻電路與芯片設計要點中文電子教材免費下載

2018-07-04 08:00:00 182

182 近年來,915MHz以及2.45GHz等UHF波段的射頻標簽由于工作距離遠,天線尺寸小等優點越來越受到重視。射頻標簽芯片的射頻接口模塊包括電源恢復電路、穩壓電路和解調整形電路。射頻接口的設計直接影響到射頻標簽的關鍵性能指標。

2019-10-11 16:05:38 2188

2188

你注意到電源對你的射頻系統的影響嗎?對于高性能的無線通信系統,電源對射頻的影響可能是“隱性”的,但卻不可忽視。這里收集整理了業界廣泛關注的幾條設計射頻電路電源的要點與經驗,小伙伴們轉走不謝~ (1)電源線是EMI 出入電路的重要途徑。通過電源線,外界的干擾可以傳入內部電路,影響RF電路指標。

2020-10-29 10:41:00 5

5 你注意到電源對你的射頻系統的影響嗎?對于高性能的無線通信系統,電源對射頻的影響可能是“隱性”的,但卻不可忽視。小編收集整理了業界廣泛關注的幾條設計射頻電路電源的要點與經驗。一、電源線是EMI 出入電路的重要途徑。通過電源線,外界的干擾可以傳入內部電路,影響RF電路指標。

2020-10-14 10:43:00 5

5 1、射頻LNA設計要求低噪聲放大器(LNA)作為射頻信號傳輸鏈路的第一級,它的噪聲系數特性決定了整個射頻電路前端的噪聲性能,因此作為高性能射頻接收電路的第一級LNA的設計必須滿足:

2020-07-31 18:51:00 4

4 1. 電源線是EMI出入電路的重要途徑。通過電源線,外界的干擾可以傳入內部電路,影響RF電路指標。為了減少電磁輻射和耦合,要求DC-DC模塊的一次側、二次側、負載側環路面積最小。電源電路不管形式有多

2020-09-11 11:38:00 3334

3334 良好的電源去耦技術與嚴謹的 PCB 布局、Vcc 引線(星型拓撲)相結合,能夠為任何 RF 系統設計奠定穩固的基礎。盡管實際設計中還會存在降低系統性能指標的其它因素,但是,擁有一個“無噪聲”的電源

2020-10-30 17:32:31 807

807 總結電源排版的10個基本要點

2021-03-17 16:42:21 2431

2431

射頻電路與芯片設計要點(中文版)免費下載。

2021-05-12 15:16:30 0

0 關于交流電路電源噪聲信號優化檢測仿真_朱秀娥(usb電源接線圖)-關于交流電路電源噪聲信號優化檢測仿真_朱秀娥這是一份非常不錯的資料,歡迎下載,希望對您有幫助!

2021-07-26 12:41:20 2

2 零星總結一些步驟和要點供大家參考。(這里的陳述是根據本人所使用的泰克混合信號示波器MSO4000系列(MSO4034)以及泰克的探頭配置,不同示波器和探頭會有些差異)選擇示波器的幾個要點。

2022-03-15 15:51:41 2526

2526 電源步板基本要點之一:旁路瓷片。電容的電容量不易太大,而它的寄生串聯電感量應該盡量減小。多個電容并聯能改善單個電容的阻抗特性。最小容量的瓷片電容應最靠近負載。

2022-09-27 15:24:06 804

804 你注意到電源對你的射頻系統的影響嗎?對于高性能的無線通信系統,電源對射頻的影響可能是“隱性”的,但卻不可忽視。這里收集整理了業界廣泛關注的幾條設計射頻電路電源的要點與經驗,小伙伴們轉走不謝。

2023-02-21 09:52:55 1856

1856 射頻工程師都了解這樣的常識:無源器件的噪聲系數與損耗相同,但是為什么是這樣的?是否在任何條件下都成立?無源器件的損耗對輸出噪聲功率有什么樣的影響?

2023-06-12 10:31:33 2280

2280

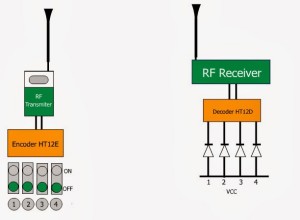

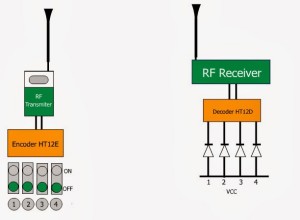

射頻遙控電路具有廣泛的應用,我們在日常生活中一直在使用它。對于電子工程師和業余愛好者來說,了解基于射頻的無線遙控器的操作以實現遠距離通信非常重要。本文為您簡要介紹了射頻發射器和接收器電路,通過這些電路可以實現遠距離通信,也可以用作基于射頻的無線遙控器。

2023-07-02 16:03:47 5157

5157

在射頻電路設計中,電路的穩態運行是設計人員需要設定的主要目標之一。在穩態下,對信號保真度、失真、噪聲和干擾等電路參數進行評估,以衡量射頻電路的性能。因此,RF電路設計應側重于提高信號保真度和減輕噪聲、失真和干擾問題。RF無源、有源元件和基板材料的行為差異會影響電路性能,因此需要考慮減輕這種影響。

2023-07-05 14:44:20 1865

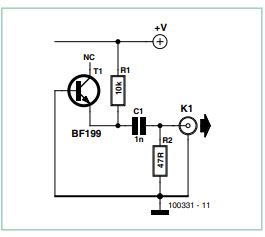

1865 簡單的射頻噪聲源是一種有用的電路,可用于多種任務,包括射頻系統測試和故障排除、確定接收器靈敏度以及運行射頻工程研究。該電路產生寬帶隨機噪聲信號,頻率范圍通常為幾千赫茲到幾千兆赫茲。

2023-08-03 17:34:08 2923

2923

電子發燒友網站提供《開關電源電路設計要點與調試.pdf》資料免費下載

2023-10-26 10:11:11 15

15 。針對于不同的噪聲,對于電源的要求也會不一樣。 在放大電路中,最常見的電源噪聲就是直流電源的紋波噪聲。直流電源的主要作用就是提供恒定的電壓和電流,而在電源內部,共模干擾和差模干擾是產生噪聲的主要原因。共模噪聲

2023-11-06 11:14:14 1393

1393 在測量電源的噪聲紋波時,采用無源探頭是一種常見的選擇。無源探頭是指在測量過程中不需要額外的電源供電的探頭。那么,為什么我們要選擇無源探頭呢?下面將詳細解釋這個問題。 首先,無源探頭具有高頻

2024-02-01 10:10:06 1215

1215

電子發燒友App

電子發燒友App

評論