本文概述了ADI T1/E1/J1收發器的環回功能。T1和E1是術語,用來描述通過任意介質進行的1.544Mbps和2.048Mbps傳輸。環回模式有助于器件或設備的診斷測試。在環回模式下,收發器將

2025-10-22 09:30:17 2601

2601

本文主要詳解基于FPGA的模糊PID控制器的設計實現,首先介紹了FPGA工作原理、基本特點以及FPGA的優勢,其次闡述了使用Altera的FPGA設計實現的數字模糊PID控制器,具體的跟隨小編一起來了解一下。

2018-06-01 09:26:51 18187

18187 的認識以外,還必須能將E1原理準確地運用到障礙處理中。一、E1(2M)電路從物理結構上看,E1傳輸設備的E1物理接頭都是有2個,一收一發。E1物理接頭阻抗可分為75Ω非平衡和120Ω平衡,75Ω非平衡

2018-02-23 10:00:09

首先要能及時和準確地處理E1線路障礙,除了必須要對E1原理有清楚的認識以外,還必須能將E1原理準確地運用到障礙處理中。一、E1(2M)電路從物理結構上看,E1傳輸設備的E1物理接頭都是有2個,一收

2017-10-28 15:32:18

當連接E1到CS+, 電機download會出現下面的錯誤,這是哪里沒有設對嗎?相同的連接使用flash programmer是可以燒寫程序的。謝謝!

2018-11-09 12:11:35

E1接口對接時,雙方的E1不能有信號丟失/幀失步/復幀失步/滑碼告警,但是雙方在E1接口參數上必須完全一致,因為個別特性參數的不一致,不會在指示燈或者告警臺上有任何告警,但是會造成數據通道的不通/誤碼/滑碼/失步等情況。

2019-10-23 09:12:19

AE400系列E1接口音頻編解碼器,是采用先進數字處理芯片,使用先進的FPGA、數字編解碼轉換和時鐘恢復技術方法設計的。適用于廣播節目源傳輸的設備。音頻編碼器是將輸入的立體聲音頻信號或AES數字音頻

2011-03-02 20:51:53

FPGA實現的SATA控制器FPGA實現的SATA控制器

2012-08-11 18:08:52

我正在設計一個HDLC接收器接口。該接口看起來非常類似于SPI從器件,除了沒有外部芯片選擇進入。幀同步發生在數據中使用唯一的令牌。因此有2個信號進入FPGA:EXT_CLK:在我的情況下幾兆DIN

2019-04-28 12:39:33

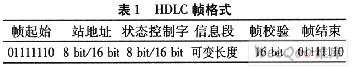

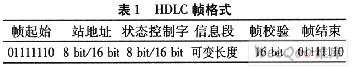

5個連“1”則在其后插入1個“0”,數據發送結束后發送幀尾“7E”。FPGA設計FPGA中實現的主要是鏈路層協議完成HDLC數據接口的收發,并完成與DSP的數據交互,該電路由接口模塊interface

2011-03-17 10:23:56

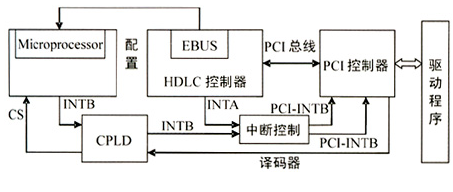

個高效、可靠的LBS控制器來實現FPGA和PEX8311的通信。如圖1所示。本系統的控制的核心是LBS控制器,該控制器是通過FPGA采用VerilogHDL實現的,其優點是穩定性強、不會造成死機

2015-01-29 14:09:17

PowerPC,dsp和fpga實現,fpga負責接收E1口,K口等數據,通過dsp的mcbsp接口傳輸到dsp,進行話音編解碼處理,然后通過HPI接口與PowerPC交互,或者通過dsp的網口直接收發數據。整個設備相當于一個路由器,它可以接入各種電臺!

2015-09-10 11:15:14

距離傳感器檢測是否有阻擋物。·小e1有耳機接口,可播放音頻。硬件整體上都不錯,模塊齊全。2.軟件/云 先看看機智云:左邊是app,右邊是微信上的操作界面。送風抽濕是控制電機的。下面來看小e1:小e1有

2016-10-29 11:39:01

E1仿真器是瑞薩的片上調試仿真器,能用于大部分瑞薩MCU,包括RL78。 1、E1與單片機的連接,有兩種通信方式可供選擇:串行連接和JTAG連接。取決于你使用的MCU的調試接口。RL78使用單線串行

2014-12-31 17:35:36

關于以太網到多路E1適配電路設計及FPGA實現你想知道的都在這

2021-05-06 06:17:04

的應用也越來越普遍。E1是我國電信傳輸網一次群使用的傳輸標準,速率是2.048 Mb/s。實現多路接口與E1協議的相互轉換,將可以把多種設備同時連接至高速的E1線路。本文基于FPGA(Field

2019-06-10 05:00:04

本文提出了一種基于FPGA的SDRAM控制器的設計方法,并用Verilog給于實現,仿真結果表明通過該方法設計實現的控制器可以在FPGA芯片內組成如圖1所示的SDRAM接口,從而使得系統用戶對SDRAM的操作非常方便。

2021-04-15 06:46:56

本文研究設計了一種基于高速隔離芯片的高速串行隔離型ADC。該數字隔離型ADC頻帶寬,延時小,穩定性高并且電路結構簡單。利用FPGA作為控制器,很好地實現了模數轉換和隔離傳輸。

2021-05-06 06:38:57

本文描述了E1 幀的基本結構,詳細介紹了E1 基本幀和CRC 復幀同步的算法,采用VHDL 語言對符 合G.704 和G.706 標準的成/解幀電路進行了RTL 描述,并最終得到ASIC 實現。

2021-04-27 06:11:42

本文介紹通過FPGA實現的步進電機控制器。該控制器可以作為單片機或DSP的一個直接數字控制的外設,只需向控制器的控制寄存器和分頻寄存器寫入數據,即可實現對步進電機的控制。

2021-04-29 06:05:44

與低速的E1信號結合起來,實現以太網與E1信號的復用。既滿足了用戶對大帶寬、高容量數據的傳輸要求,又提供了E1信號接入功能,實現電話業務及其他專用通信系統的接入功能。

2019-08-14 08:01:09

求一種基于FPGA的HDLC協議控制器設計方案

2021-04-30 06:53:06

基于FPGA的MCU設計有兩種基本實現方式如何實現微控制器與FPGA的接口設計

2021-05-06 10:05:17

一:概述1路E1 PDH光端機是漢源高科(北京)科技有限公司以超大規模集成電路核心構成的1路光電合一傳輸設備。可提供面向電信的E1傳輸,面向ISDN的傳輸和多種接口(音頻、數據),面向 LAN

2022-06-13 21:14:08

MT9079是Mitel公司生產的E1控制器,具有高密度3電平碼、歸零碼、不歸零碼、雙極性歸零碼四種編碼方式,接收彈性緩沖區可緩沖峰峰值為208 個比特的線路信息抖動,功能強大,使用方便,是

2009-04-23 15:53:09 10

10 傳統交通燈控制器多數由單片機或PLC 實現。本論文介紹一種用FPGA 實現交通燈控制器的設計方法。關鍵詞:FPGA; VHDL; MAXPLUSll; 交通燈控制器Abstract:Traffic light controller is usually

2009-06-12 11:12:52 90

90 以太網到多路E1適配電路設計及FPGA實現

摘要:介紹了一種基于現場可編程門陣列(FPGA)的以太網數據-多路E1反向復用器同步電路設計,分析了FPGA具體實現過程中的一些常

2009-11-13 20:59:00 22

22 本文詳細介紹了E1 信號基本幀和復幀的結構,以及基本幀和復幀的同步算法,并對E1 接口的時鐘恢復,碼型轉換實現做了具體介紹。同時對各種告警信號的產生做了詳細闡述。采用VH

2010-01-20 11:45:18 24

24 NandFlash控制器的FPGA實現方法技巧與程序案例分享。

2017-09-21 09:40:00 78

78 摘要:基于EPON的網絡接入,通過E1電路仿真實現信號傳輸.其E1數據包到EPON總線的傳輸,通過HDB3線路編碼到NRZ數字信號的轉換,系統及網絡時鐘設定,EPON數據幀的組織,El仿真電路

2010-05-06 10:11:02 40

40 概述AE400系列E1接口音頻編解碼器,是采用先進數字處理芯片,使用先進的FPGA、數字編解碼轉換和時鐘恢復技術方法設計的。適用于廣播節目源傳輸的設備。音頻編碼器是將輸入

2010-07-05 15:48:46 55

55 使用嵌入式微處理器S3C4510B內部包含的HDLC控制器封裝和解析HDLC協議,微處理器既可實現系統功能,又可完成HDLC協議的數據傳輸,降低了設計的復雜度。本設計已應用于微波網絡管理

2010-07-08 15:26:27 46

46 The Agilent Technologies E4206 T1/E1 Frame Processor is a high-performance hardware module

2010-07-09 17:49:46 11

11 利用FPGA 設計一個類似點陣LCD 顯示的VGA 顯示控制器,可實現文字及簡單的圖表顯示。工作時只需將要顯示內容轉換成對應字模送入FPGA,即可實現相應內容的顯示。關鍵詞:FPGA

2010-09-22 10:17:23 138

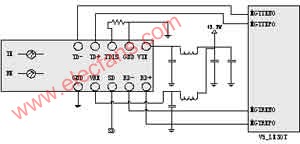

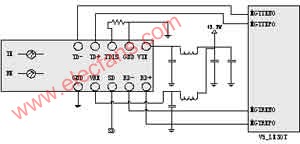

138 為了滿足某測控平臺的設計要求,設計并實現了基于FPGA的六通道HDLC并行通信系統。該系統以FPGA為核心,包括FPGA、DSP、485轉換接口等部分。給出了系統的電路設計、關鍵模塊及軟件

2010-09-30 16:49:30 43

43 高級數據鏈路控制HDLC協議是一種面向比特的鏈路層協議,具有同步傳輸數據、冗余度低等特點,是在通信領域中應用最廣泛的鏈路層協議之一。提出實現HDLC通信協議的主要模塊—

2010-11-26 16:51:03 33

33 在WTB底層協議的研究中,其基本幀格式與ISO3309的HDLC要求一致,故設計了一種基于FPGA的HDLC編解碼器。重點介紹了協議和實現方法,給出了相應的Verilog代碼,通過硬件下載與標準的WTB

2010-12-11 16:07:25 26

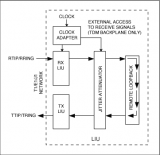

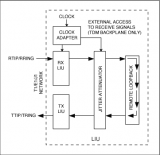

26 DS33R11 以太網映射器,集成了T1/E1/J1收發器

DS33R11 概述

DS33R11將MAC幀按照HDLC或X.86 (LAPS)格式進行打包,以T1/E1/J1數據流

2008-10-06 14:51:08 1501

1501 摘要:具有多端口T1/E1/J1線卡的現代通信系統通過增加冗余來滿足電信網絡的高可用性要求。過去,這些系統曾經用繼電器來實現N+1冗余切換。隨著每個線卡上的T1/E1/J1端口數和每

2009-04-20 09:00:25 1553

1553

, DS21Q55, DS21Q50 and DS26528 in T1/E1, 2MHz, 4MHz, 8MHz clock mode. The hardware connection and software configuration are given.

2009-04-20 09:26:34 1782

1782

摘要:具有多端口T1/E1/J1線卡的現代通信系統通過增加冗余來滿足電信網絡的高可用性要求。過去,這些系統曾經用繼電器來實現N+1冗余切換。隨著每個線卡上的T1/E1/J1端口數和每

2009-04-20 11:14:48 2177

2177

DS31256 HDLC控制器的配置步驟—橋接模式

本應用筆記提供了怎樣配置橋接模式下DS31256 HDLC控制器T1端口的例子。文章提供了一個實際例程,以方便最終用戶使用,幫助他

2009-04-21 14:59:48 1851

1851

DS31256 -256通道、高吞吐率HDLC控制器

概述

DS31256是一款256通道高層數據鏈路控制器(HDLC),

2009-04-21 23:17:11 1713

1713

摘 要:介紹了SDRAM的特點和工作原理,提出了一種基于FPGA的SDRAM控制器的設計方法,使用該方法實現的控制器可非常方便地對SDRAM進行控制。

關鍵

2009-06-20 13:04:51 2458

2458 摘要: HDLC(高級數據鏈路控制)的一般實現方法為采用ASIC器件和軟件編程等。應用ASIC器件時設計簡單,但靈活性較差;軟件編程方法靈活,但占用處理器資源多

2009-06-20 13:47:15 4110

4110

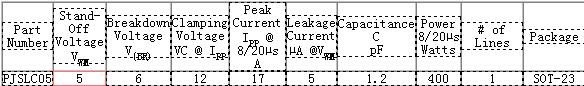

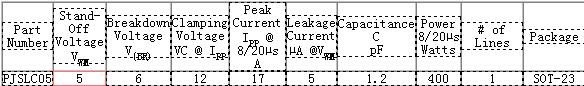

E1(T1)保護電路及方案

2009-11-20 09:06:38 2892

2892

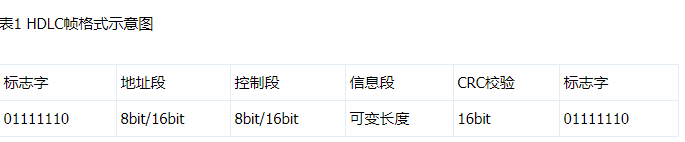

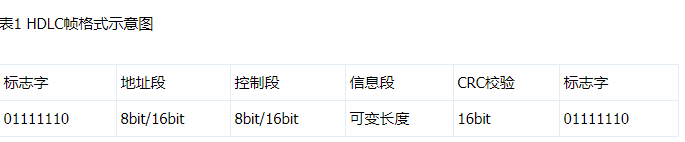

基于FPGA的多通道HDLC收發電路設計

HDLC(High Level Date Link Control)協議是通信領域中應用最廣泛的協議之一,它是面向比特的高級數據鏈路控制規程,具有差錯檢測功能強大

2009-12-10 10:14:35 2245

2245 什么是T1與E1線路

Leased Line 租用線路 租用線路是電信公司為某一機構建造的永久性通信電路。租用線路旁路了本地交換電信局(LEC)上的

2010-03-19 14:10:45 7679

7679 本文設計的基于Xilinx FPGA的千兆位以太網及E1信號的光纖傳輸系統采用Xilinx XC5VLX30T芯片,通過以太網測試儀和數據誤碼儀對本系

2010-07-06 09:09:10 3062

3062

摘要:為了實現高速HDLC通訊協議,設計了DSP+FPGA結構的485通訊接口,接口包括DSP、FPGA、485轉換等硬件電路,以及DSP與FPGA之間的數據交換程序和FPGA內部狀態機;其中DSP用于實現數據控制,FPGA用于實現HDLC通訊協議,DSP與FPGA之間采用XINTF方式,通過雙FI

2011-02-25 17:24:34 98

98 HDLC協議是通信領域中應用最廣泛的協議之一! 它是面向位的高級數據鏈路控制規程! 具有差錯檢測功能強大 高效和同步傳輸的特點,目前市場上有很多專用的HDLC芯片! 但這些芯片功能和接

2011-05-17 10:40:26 91

91 本文提出了一種多路接口與E1的協議轉換設計方法,并具體介紹了時隙分配及調度、空時隙處理等技術難點。通過實現V.35,RS449,RS 232三路接口與E1的協議轉換,證明該方案是可行的

2011-05-31 10:25:15 4616

4616

為了實現軍航管制系統中雷達數據的可靠傳輸,根據 HDLC 協議的幀結構和循環冗余校驗(CRC)原理,提出了一種新型的基于并行機制的HDLC協議控制器,討論采用FPGA新技術實現HDLC協議幀的構成

2011-07-20 16:17:50 93

93 研究實現了一種 HDLC (High Level Data Link Contr01)協議的改進方法,該方法把HDLC協議傳統的同步傳榆方式改成了異步傳輸方式,既保留了原有HDLC協議的主要優點,又增強了傳榆教據的抗干擾

2011-07-20 17:25:50 62

62 介紹了嵌入式PowerPC 處理器MPC8280 和多通道控制器的主要特征。MPC8280 具有8 個TDM 接口,每個TDM 均支持E1/T1 接口。多通道控制器可以使MPC8280 最多支持256路獨立的HDLC 或者透明傳輸通道。通

2011-09-16 15:13:27 2247

2247

介紹了采用Xilinx spartan2系列FPGA 芯片,配以異步SRAM ,完成了以太網數據流和E1數據流之間的相互轉換,并給出了SRAM 接口模塊和HDB3編碼模塊的算法設計流程及相關仿真結果。

2011-10-11 15:04:35 34

34 介紹了HDLC協議RS485總線控制器的FPGA實現

2012-02-14 14:59:36 100

100 本設計基于FPGA的彩色觸摸屏控制器能夠實現顏色深度為24 bit,分辨率為480×272的TFT-LCD控制和ADS7843芯片的時序控制,為后續IP核的編寫工作打下了基礎。

2013-01-07 11:08:20 3441

3441

快速浮_定點PID控制器FPGA的研究與實現

2016-05-11 11:30:19 20

20 Xilinx FPGA工程例子源碼:FPGA實現CAN總線控制器源碼

2016-06-07 14:13:43 97

97 基于FPGA的VGA圖像控制器的設計與實現

2016-08-30 15:10:14 13

13 E1基礎知識講座

2016-12-23 02:36:25 0

0 一種基于FPGA的E1數字傳輸分析儀成解幀實現方法_耿立華

2017-03-14 16:50:00 2

2 DSP和FPGA的HDLC協議通訊電路設計

2017-10-19 14:46:11 7

7 引言 HDLC(高級數據鏈路控制)廣泛應用于數據通信領域,是確保數據信息可靠互通的重要技術。實施HDLC的一般方法通常是采用ASIC器件或軟件編程等。 HDLC的ASIC芯片使用簡易,功能針對性強

2017-10-25 16:52:15 0

0 HDLC(高級數據鏈路控制)廣泛應用于數據通信領域,是確保數據信息可靠互通的重要技術。實施HDLC的一般方法通常是采用ASIC器件或軟件編程等。 HDLC的ASIC芯片使用簡易,功能針對性強,性能

2017-10-26 16:50:59 1

1 體制的。但當前一些專用網絡中還大量保有傳統的E1信道,為了使基于IP網絡體制的視頻設備能夠充分利用傳統的E1信道進行數據傳輸,設計了一種基于E1信道的視頻數據傳輸系統。采用高性能通信媒體處理器Hi3520D.實現720P面質的視頻實時編碼,配

2017-11-15 11:21:46 13

13 信號與低速的E1信號結合起來,實現以太網與E1信號的復用。既滿足了用戶對大帶寬、高容量數據的傳輸要求,又提供了E1信號接入功能,實現電話業務及其他專用通信系統的接入功能。

2017-11-24 14:16:32 7388

7388

基于SDH E1信道的時間同步傳輸精度受到時延、采樣誤差、碼速調整、指針調整等因素的影響。本文對光纜傳輸時延和設備處理時延進行了分析,通過示意圖和案例對采樣誤差進行了解釋并得出結論,通過比較兩個固定

2017-12-12 18:09:10 1

1 高級數據鏈路控制(HDLC,High-Level Data Control)是一種同步數據傳輸、面向比特的數據鏈路層協議,具有差錯檢測功能強大、高效和同步傳輸的特點,目前HDLC協議已成為是通信領域中應用最廣泛的協議之一,在飛行器設計領域經常用作飛控與舵機,助推器等之間通信的通信協議。

2018-05-05 09:26:00 3360

3360

在線調試工具E1

2018-07-23 00:08:00 4366

4366 FPGA能對任意數據寬度的信號進行處理,內部的功能模塊可以并行處理。因此,采用FPGA技術設計HDLC協議控制器可以均衡整個系統的負荷,實現多通道的高性能HDLC協議控制器,保證通信的可靠性。同時

2018-12-30 11:00:00 4456

4456

DS21Q59是美國MAXIM公司出品的單片四路E1收發器芯片,是一種優化的高密度E1線路終端。它包含四個由線路接口單元(LIU)和成幀器組成的完全獨立的收發器,具備了連接四條E1線路所需的各種功能

2018-10-11 10:03:00 9330

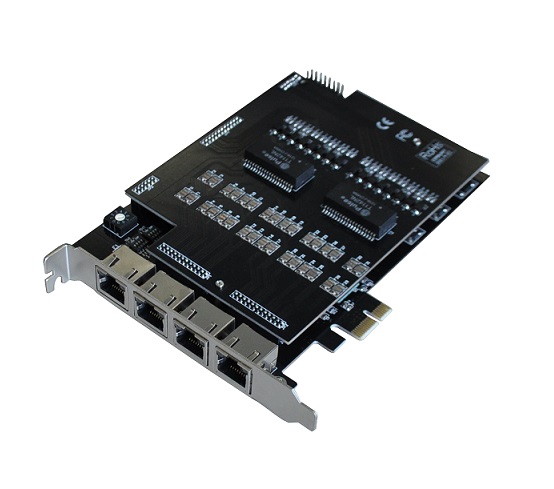

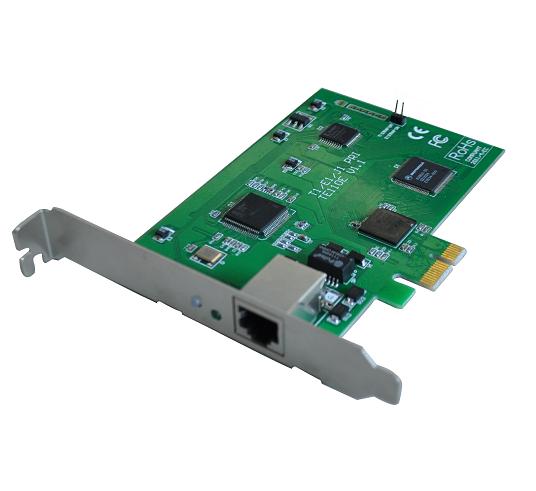

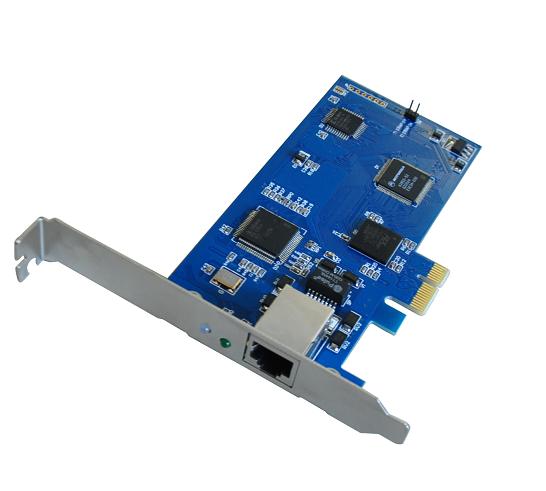

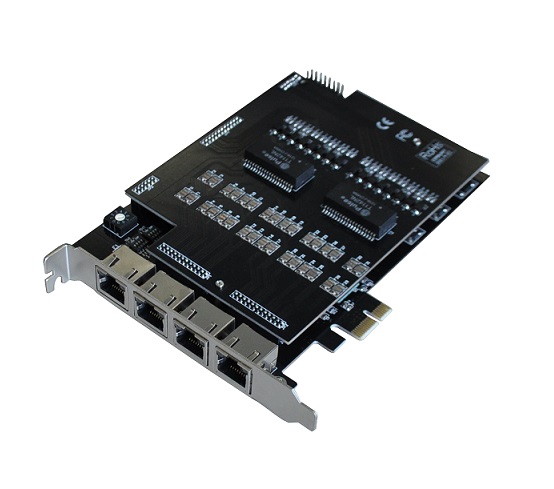

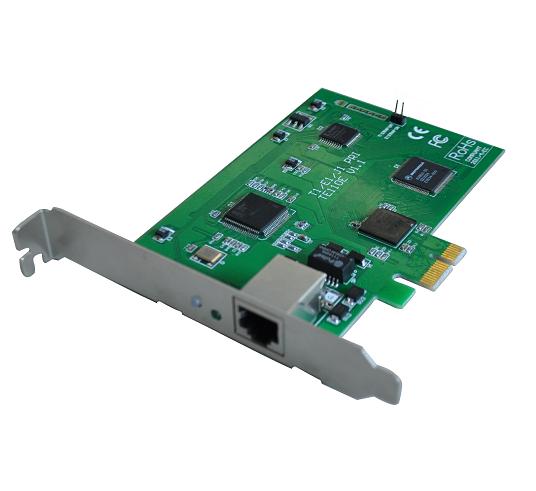

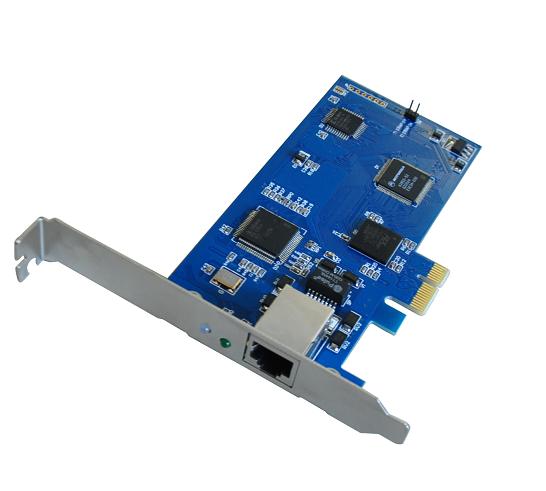

9330 SinoV-TE820E PCI-E數字E1語音板卡是基于Asterisk 開源IP-PBX的PCI-E語音板卡.支持8 E1/T1接口,提供全雙工速率16.384M數據傳輸或者240路語音通訊.

2019-11-20 16:42:26 3964

3964

SinoV-TE110E-B 單E1語音板卡是基于Asterisk 開源IP-PBX的PCI-E語音板卡,支持1 E1/T1接口,提供全雙工速率16.384M數據傳輸或者30路語音通訊.每臺機器可以

2019-11-25 15:04:45 2187

2187

/D4T1/E1),卡上提供了2個獨立的HDLC收發器,支持SS7的FISU收發,該卡還提供了Jitter Attenuator,可以對線路抖動進行處理.

2019-11-25 15:13:22 2479

2479

/D4T1/E1),卡上提供了2個獨立的HDLC收發器,支持SS7的FISU收發,該卡還提供了Jitter Attenuator,可以對線路抖動進行處理.

2019-11-25 15:11:10 2965

2965

/D4T1/E1),卡上提供了2個獨立的HDLC收發器,支持SS7的FISU收發,該卡還提供了Jitter Attenuator,可以對線路抖動進行處理.

2019-11-25 15:15:46 2162

2162

/D4T1/E1),卡上提供了2個獨立的HDLC收發器,支持SS7的FISU收發,該卡還提供了Jitter Attenuator,可以對線路抖動進行處理.

2019-11-25 15:28:05 2500

2500

SinoV-TE110E 單E1語音板卡是基于Asterisk 開源IP-PBX的PCI-E語音板卡,支持1 E1/T1接口,提供全雙工速率16.384M數據傳輸或者30路語音通訊.每臺機器可以支持

2019-11-25 15:14:34 2674

2674

跟蹤模式。同時芯片內部提供豐富信令功能,可提供CAS信令的提取,提取內容輸出方式靈活。CPU通過Bus控制對E1模塊進行配置以及實現各種告警的監控和管理。

2020-04-04 17:23:00 6537

6537

.同時它還具有設計開發周期短、設計制造成本低、可實時在線檢驗等優點,因此被廣泛用于特殊芯片設計中.本設計中采用Altera公司的FLEX10K芯片EPF10K20RC240-3來實現HDLC協議控制器.

2020-09-27 21:00:12 1830

1830

為了實現軍航管制系統中雷達數據的可靠傳輸,根據HDLC協議的幀結構和循環冗余校驗(CRC)原理,提出了一種新型的基于并行機制的HDLC協議控制器,討論采用FPGA新技術實現HDLC協議幀的構成

2020-11-04 18:04:10 15

15 E1協議轉換器也叫接口轉換器,是實現數據通信網以太網接口與光纖通信傳送網E1接口連接時進行兩種接口轉換的設備。廣泛應用在傳輸站E1接口與網絡交換機相連時的接口轉換中。現飛暢科技小編對其使用過程中常見故障及解決方法進行歸納,希望對大家在應用此類設備時有所幫助

2020-12-25 15:13:31 3974

3974 單E1光端機是一種將G.703的E1信號調制到光纖上傳輸的設備。采用大規模集成芯片,電路簡單,功耗低,可靠性高,具有完整的告警狀態指示和完善的網管功能。那么,單E1光端機分類及技術指標有哪些呢?接下來我們就跟隨飛暢科技的小編一起來看看吧!

2021-01-13 14:39:24 3055

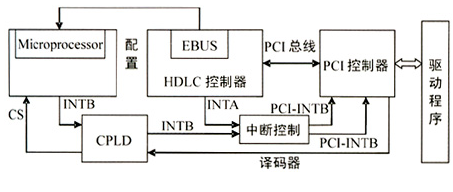

3055 E1數據采集卡從E1線上采集信令消息(包括七號信令等),用以監視和仿真整個通話流程。控制流程如圖1所示,PCI接口芯片(HDLC控制器)是一個多功能設備,包括一個網絡控制器和一個PCI橋設備

2021-05-22 15:31:17 4105

4105

實現基于FPGA的SPIFlash控制器設計(嵌入式開發工作怎么樣)-該文檔為實現基于FPGA的SPIFlash控制器設計簡介資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-30 09:10:17 5

5 基于FPGA的SDRAM控制器的設計與實現簡介(嵌入式開發工程師和基層公務員)-該文檔為基于FPGA的SDRAM控制器的設計與實現簡介文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 09:34:59 11

11 本應用筆記介紹如何使用達拉斯半導體DS21X52和DS21X54單芯片收發器(SCT)和DS216xx時鐘適配器(CLAD)將T1轉換為E1,反之亦然。DS21X52 SCT用于T1信號

2023-01-10 13:45:37 2874

2874

本應用筆記提供了使用達拉斯半導體/Maxim通信產品T1/E1單芯片收發器(SCT)和T1/E1成幀器的小數T1和E1電路設計示例。

2023-01-10 14:09:48 2591

2591

DS31256有16個物理端口(16 Tx和16 Rx)或鏈路,可配置為信道化或非信道化。通道化端口可以處理一個、兩個或四個 T1 或 E1 數據鏈路。這些端口或鏈路的時鐘可以支持間隔時鐘。本應用筆記介紹如何在256通道HDLC控制器DS31256中實現間隙時鐘應用。

2023-01-13 10:25:28 1617

1617

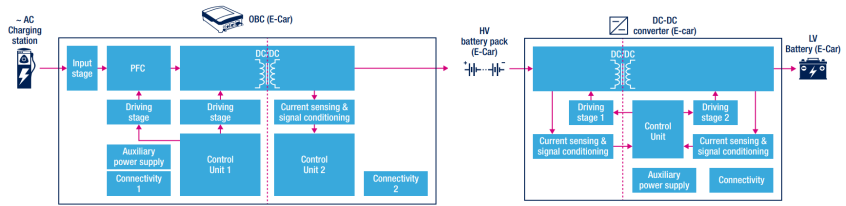

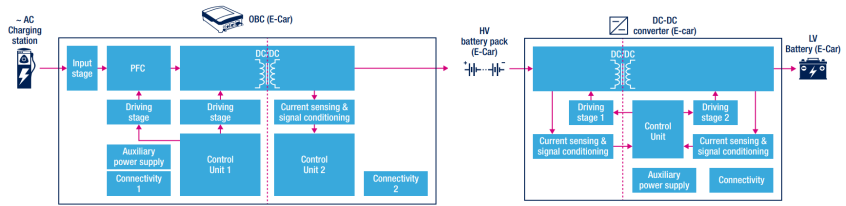

基于全新Stellar E1微控制器的22KW OBC-DC/DC ST 系統解決方案

2023-10-30 18:25:13 2449

2449

電子發燒友網站提供《步進電機控制器的FPGA的實現.pdf》資料免費下載

2023-10-07 16:29:17 1

1 實時視頻SDRAM控制器的FPGA設計與實現

2022-12-30 09:21:26 4

4

電子發燒友App

電子發燒友App

評論