完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態的最佳平臺。

先談談第二點關于思維習慣。我發現有些人會有這樣一種習慣,先用一段式狀態機實現功能,仿真ok后,再將其轉成三段式,他們對這種開發方式的解釋是一段式更直觀,可以更便捷的構建功能框架,但是大家都說三段式性能會更好...

fpga 會從 0 開始讀,地址不斷自增,直到讀取到有效的同步字 sync word(0xAA995566),才認為接下來的內容是一個有效的 bin 文件內容的開始。讀到有效 sync word 后不會再繼續讀搜尋其他的 bin 文件。如 UG470 文檔 page81 描述:...

LMZ31506 簡單開關器等電源模塊可以將 DC/DC 轉換器、功率 MOSFET、屏蔽電感器和無源器件集成到薄型 QFN 封裝中。這可以減少設計時間,因為所有東西都已經集成到一個封裝中,并且只需要最少的外部組件。...

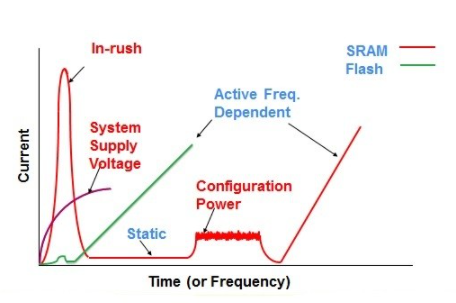

當今以 DSP 為中心的系統設計面臨著越來越大的壓力,需要在各種應用中最大限度地降低功耗。通過降低總功耗而不僅僅是靜態功耗,當今基于閃存的 FPGA 技術在實現下一代高速、DSP 密集型系統設計方面發揮著關鍵作用,這些設計必須以不斷縮小的外形尺寸提供高算法性能和最低可能的功耗。...

現場可編程門陣列(FPGA)可以實現任意數字邏輯,從微處理器到視頻生成器或加密礦機,一應俱全。FPGA由許多邏輯模塊組成,每個邏輯模塊通常由觸發器和邏輯功能以及連接邏輯模塊的路由網絡組成。...

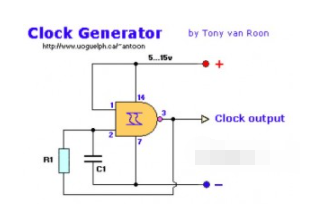

您可以在此電路中使用 IC 7400 或 4011。7400 是晶體管-晶體管邏輯 (TTL) 類型,而 4011 是互補金屬氧化物半導體 (CMOS) 類型。IC 4011 比 7400 便宜,但 7400 比 4011 快。...

XADC具有兩個12位的ADC,具有獨立的跟蹤和保持放大器,模擬多路復用器(最多17個外部模擬輸入通道)以及片上散熱和片上電壓傳感器。可以將兩個ADC配置為同時采樣兩個外部輸入模擬通道。采樣保持放大器支持一系列模擬輸入信號類型,包括單端輸入,雙端輸入和差分輸入。模擬輸入可以支持信號帶寬在1M SPS...

always 模塊的敏感表為電平敏感信號的電路可幾乎可以完成對所有組合邏輯電路的建模。always模塊的敏感列表為所有判斷條件信號和輸入信號,但一定要注意敏感列表的完整性(注意通配符*的使用)。...

表1-1列出了7系列FPGA封裝中的管腳定義。注意:表1-12有單獨列出的專用通用用戶I/O,也有標記IO_LXXY_ZZZ#或者I/O_XX_ZZZ_#標識的多功能I/O,其中ZZZ代表一種或幾種附加的功能。如果多功能I/O不用做特殊用途,它們可以當作普通I/O使用,這一點我們在硬件設計時要注意。...

DC-SCM架構定義了與CPU板互操作的輸入/輸出端口。DC-SCM服務器在HPM(主機處理器模塊)板上只有基本的中央計算元件(CPU)、高速存儲器和IO連接器,其他所有組件均在模塊化DC-SCM(安全、控制、管理)板上。...

調用內部鎖相環由輸入的12M時鐘得到120MHZ工作時鐘,驅動DDS控制模塊,輸出作為DAC的轉換時鐘。...

對于現今的FPGA芯片供應商,在提供高性能和高集成度獨立FPGA芯片和半導體知識產權(IP)產品的同時,還需要提供性能卓越且便捷易用的開發工具。...

自動電壓調節器(AVR)通常也稱為穩壓器,它通過補償輸入電壓的波動來調節供電電壓電平,在許多工業和住宅應用中都很常見。例如,AVR被用于船舶發電機組、應急電源和石油鉆井平臺,以在電力需求波動期間穩定電壓電平。...

? ? Xilinx zynq系列FPGA實現神經網絡評估 本篇目錄 1. 內存占用 ??? 1.1?FPGA程序中內存的實現方式 ????1.2?Zynq的BRAM內存大小 ????1.3?一個卷積操作占用的內存 2. PipeCNN可實現性 ??? PipeCNN論文解析:用OpenCL實現FP...

FIFO是隊列機制中最簡單的,每個接口上只有一個FIFO隊列,表面上看FIFO隊列并沒有提供什么QoS保證,甚至很多人認為FIFO嚴格意義上不算做一種隊列技術,實則不然,FIFO是其它隊列的基礎...

面對我國航天型號任務發展與需求的快速變化,空間站、深空探測、北斗導航等軟件密集型系統迅速擴大,智能化、網絡化需求越來越多。...

遷移預覽部分列出了從源庫中標識的元件類型組——作為元件類型() 或建議的文件夾結構() 并包括這些元件 ( Components ) 的基于參數的網格視圖。網格中的參數值可以即時編輯,無需打開和編輯源庫。下方的詳細信息區域包括來自當前選定元件的附加信息——零部件選擇、模型和數據表等。...

但是作為從 Web 里誕生的框架,和 React Native/ Weex 不同的是,前者是先有了 Web 下的 React 和 Vue 實現之后才有的客戶端支持,而對于 Flutter 則是反過來,先有客戶端實現之后才支持 Web 平臺,這里其實可以和 Weex 做個簡單對照。...

通過邏輯內部定位發現丟包地點為下行SSRAM讀寫處,即下行業務包寫入SSRAM,再讀出后包內容出錯導致報文丟棄。FPGA外掛SSRAM結構框圖見圖1,進入FPGA內部的上行業務和下行業務都需要通過各自的SSRAM進行緩存來實現一些功能。...

對于testbench而言,端口應當和被測試的module一一對應。端口分為input,output和inout類型產生激勵信號的時候,input對應的端口應當申明為reg, output對應的端口申明為wire,inout端口比較特殊,下面專門講解。...