完善資料讓更多小伙伴認識你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)技術(shù)文庫為您提供最新技術(shù)文章,最實用的電子技術(shù)文章,是您了解電子技術(shù)動態(tài)的最佳平臺。

在密碼領(lǐng)域,美國一直在向全世界推廣MD5密碼,還多次聲稱:沒人能破解我們的MD5密碼,就連著名的密碼學(xué)家Biham,也把破解MD5密碼作為一生的夢想。(這是多年前的言論。不要過度解讀,做個簡單開場白~)...

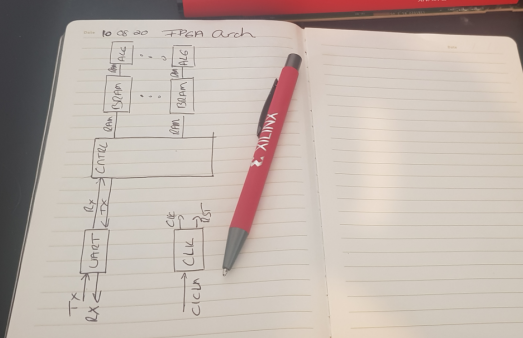

今天給大家介紹一下FPGA上部署深度學(xué)習(xí)的算法模型的方法以及平臺。希望通過介紹,算法工程師在FPGA的落地上能“稍微”緩和一些,小白不再那么迷茫。...

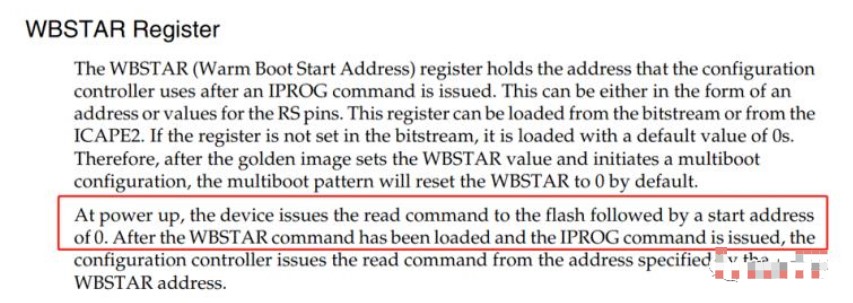

階段0,主要是運行芯片內(nèi)部固化的BootROM程序,這個BootROM主要是識別啟動模式(spi/sd/nand/nor/)是哪一種?...

圖像是用各種觀測系統(tǒng)以不同形式和手段觀測客觀世界而獲得的,可以直接或間接作用于人眼進而產(chǎn)生視知覺的實體。...

引言:7系列FPGA具有多個時鐘路由資源,以支持各種時鐘方案和要求,包括高扇出、短傳播延遲和極低的偏移。...

7系列FPGA擁有豐富的時鐘資源。各種緩沖器類型、時鐘輸入管腳和時鐘連接,可以滿足許多不同的應(yīng)用需求。選擇合適的時鐘資源可以改善布線、性能和一般FPGA資源利用率。BUFGCTRL(最常用作BUFG)是最常用的時鐘布線資源。這些真正的全局時鐘可以連接到器件的任何位置。但是在某些情況下,出于性能、功能...

最早的ML應(yīng)用實現(xiàn)是軟件導(dǎo)向的,并對CPU和GPU產(chǎn)生了巨大影響。但CPU和GPU面臨的挑戰(zhàn)在于其巨大的功耗——即使對于數(shù)據(jù)中心來說也是這樣。“人們試著用軟件實現(xiàn)創(chuàng)新,但卻無法控制功耗...

鑒相器將輸入周期信號的相位與壓控振蕩器輸出信號的相位進行比較,得到相位差θc,PD將θc轉(zhuǎn)換為誤差電壓信號ud(t)輸出。誤差電壓通過環(huán)路濾波器進行濾波,濾除交流成分,濾波的過程即為對誤差電壓信號ud(t)求平均值的過程,輸出直流控制電壓uc(t)。...

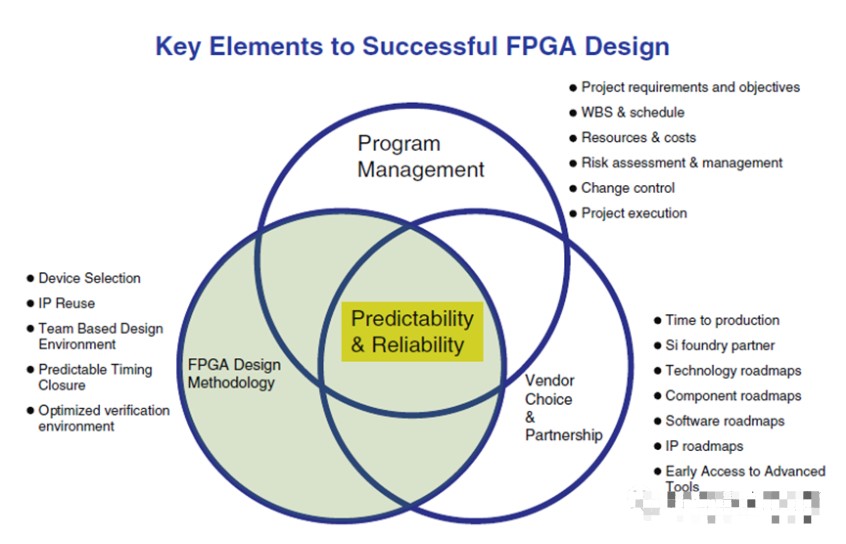

為了在越來越復(fù)雜的系統(tǒng)設(shè)計中,F(xiàn)PGA工程師之間保持高效溝通和工作推進,這就需要找到一個適合的設(shè)計方法論。目標是通過在設(shè)計團隊之間建立一個通用的方法來提高FPGA設(shè)計團隊的生產(chǎn)力,同時允許跨團隊交換設(shè)計模塊。 FPGA設(shè)計中的三個關(guān)鍵因素:...

在5G無線、衛(wèi)星通信、雷達探測、航天測控等復(fù)雜系統(tǒng)設(shè)計中,F(xiàn)PGA工程師扮演著重要角色。...

中科億海微神針系列可編程邏輯芯片EQ6GL9具有小尺寸和超低靜態(tài)功耗的顯著優(yōu)勢,最小尺寸為11mm×11mm,最低靜態(tài)電流為2mA,支持塑封和陶封兩種封裝類型的多種封裝方式,可替換國外知名可編程邏輯芯片廠家百萬門級器件和CPLD器件。...

由于亞穩(wěn)態(tài)的輸出在穩(wěn)定下來之前可能是毛刺、振蕩、固定的某一電壓值,因此亞穩(wěn)態(tài)除了導(dǎo)致邏輯誤判之外,輸出在0~1之間的中間電壓值還會使下一級產(chǎn)生亞穩(wěn)態(tài)(導(dǎo)致亞穩(wěn)態(tài)的傳播)。...

使用Laplacian算子濾波是將模板與圖像做卷積運算,然后將得到的結(jié)果取絕對值后,再進行防治溢出(灰度值大于255)處理。所以在用硬件實現(xiàn)Laplacian算子時可分成三個步驟:構(gòu)造模板;使用模板對圖像進行卷積運算;對卷積后的結(jié)果做后處理。...

什么是FPGA原型?? FPGA原型設(shè)計是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗證專門應(yīng)用的集成電路(ASIC),專用標準產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能和性能。? 由于硬件復(fù)雜性不斷增加,需要驗證的相關(guān)軟件數(shù)量不斷增加,因此它今天的使用范圍更加廣泛。? 為...

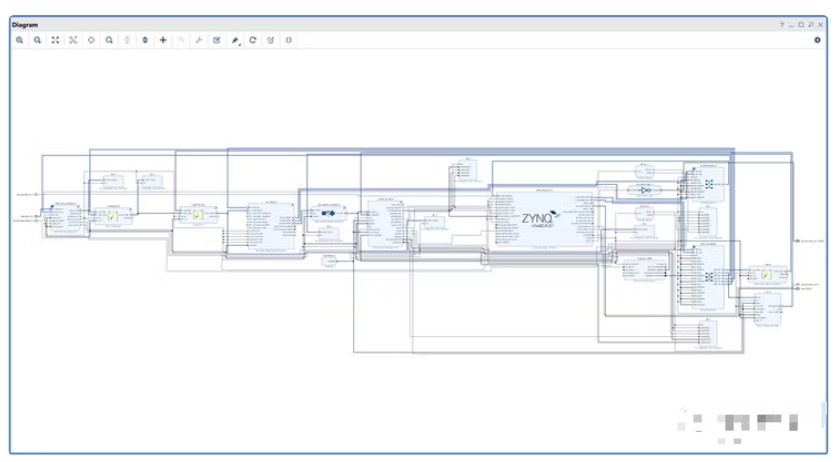

在這個項目中,我們將探索使用 PCAM(FMC擴展板) 和 Display Port 建立和運行圖像處理。然后,我們可以添加圖像處理 IP 內(nèi)核以進一步展示FPGA的處理圖像的能力。...

今天給大俠帶來基于FPGA的數(shù)字視頻信號處理器設(shè)計,由于篇幅較長,分三篇。今天帶來第三篇,下篇,程序測試與運行。話不多說,上貨。...

今天給大俠帶來的是一周掌握FPGA Verilog HDL 語法,今天開啟第二天。上一篇提到了整數(shù)型以及參數(shù)型,此篇我們繼續(xù)來看變量以及后續(xù)其他內(nèi)容,結(jié)合實例理解理論語法,會讓你理解運用的更加透徹。下面咱們廢話就不多說了,一起來看看吧。...

今天給大俠帶來的是一周掌握FPGA Verilog HDL 語法,今天開啟第一天,下面咱們廢話就不多說了,一起來看看吧。...

fpga 上電時,默認是從 flash 的 0x00 地址開始讀數(shù)據(jù)。...

高效的架構(gòu)和實現(xiàn)應(yīng)盡可能利用供應(yīng)商的現(xiàn)有IP核。確定可以在整個體系結(jié)構(gòu)中重用的模塊也是明智的,例如控制算法或通信總線。我的設(shè)計中有3個FPGA需要構(gòu)建,因此識別可以通用的模塊將在開發(fā)和驗證過程中節(jié)省大量時間。...